### INTRODUCTION

S6A0073 is a dot matrix LCD driver & controller LSI which is fabricated by low power CMOS technology. It can display 1, 2 or 4 lines with  $5 \times 8$  or  $6 \times 8$  dots format.

### **FUNCTIONS**

- Character type dot matrix LCD driver & controller

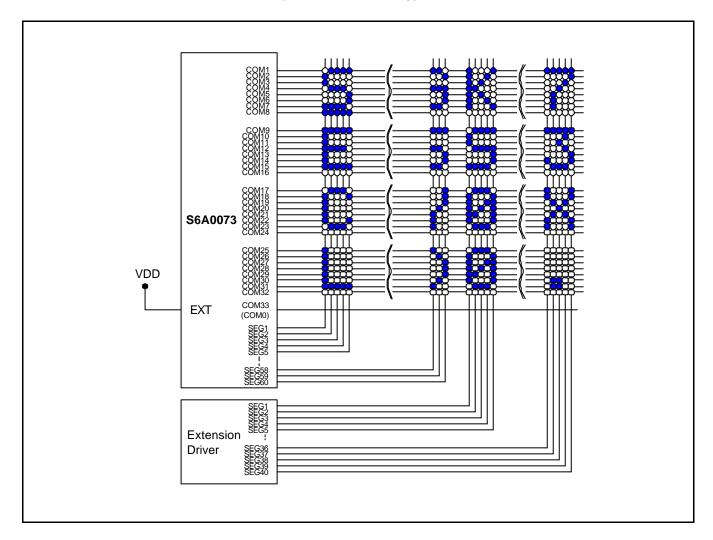

- Internal driver: 34 common and 60 segment signal output

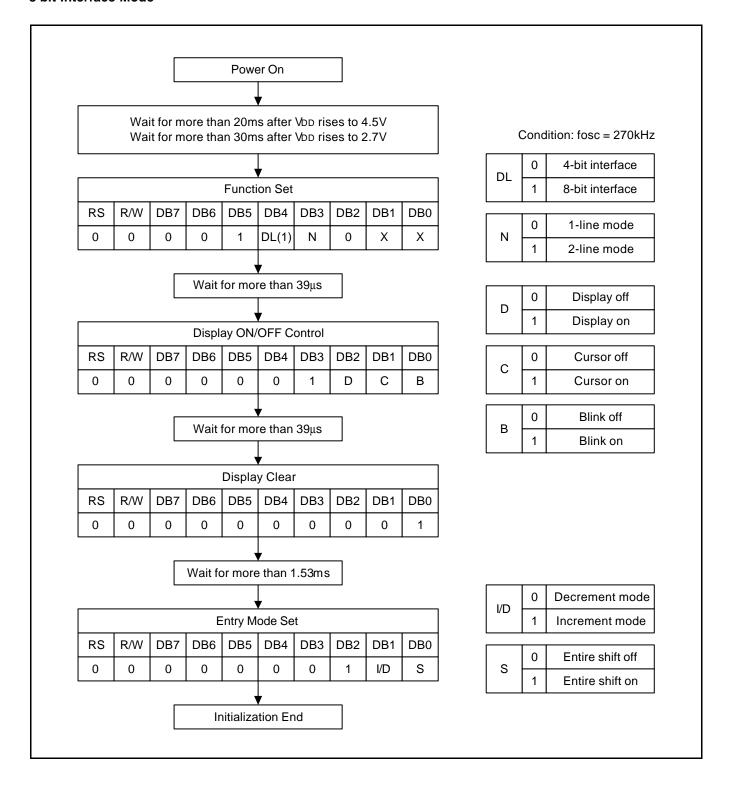

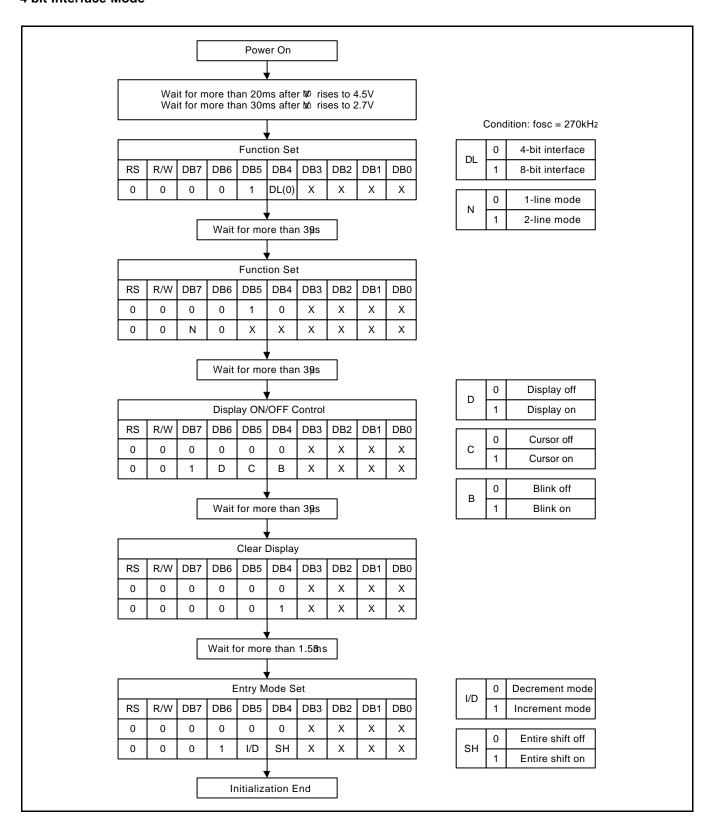

- Easy interface with 4-bit or 8-bit MPU

- Clock synchronized serial Interface

- $5 \times 8$  or  $6 \times 8$  dots matrix possible

- Extension driver interface possible

- Bi-directional shift function

- All character reverse display

- Display shift per line

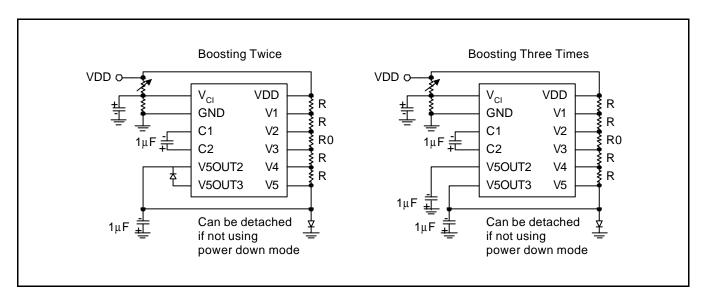

- Voltage converter for LCD drive voltage: 13V max (2 times/3 times)

- Various instruction functions

- Automatic power on reset

### **FEATURES**

- Internal Memory

- Character Generator ROM (CGROM): 9,600 bits (240 characters × 5 × 8 dot)

- Character Generator RAM (CGRAM) :  $64 \times 8$  bits (8 characters  $\times 5 \times 8$  dot)

- Segment Icon RAM (SEGRAM) : 16 × 8 bits (96 icons max.)

- Display Data RAM (DDRAM): 80 × 8 bits (80 characters max.)

- Low power operation

- Power supply voltage range: 2.7 to 5.5V (V<sub>DD</sub>)

- LCD Drive voltage range: 3.0 to 13.0V (V<sub>DD</sub> V5)

- CMOS process

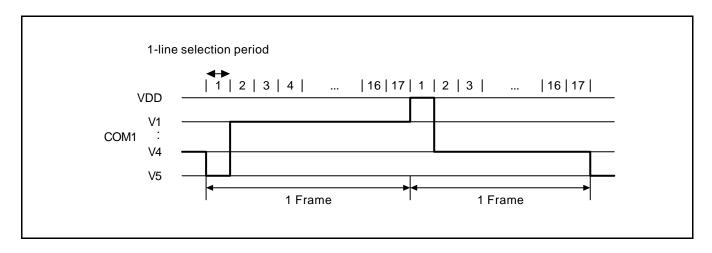

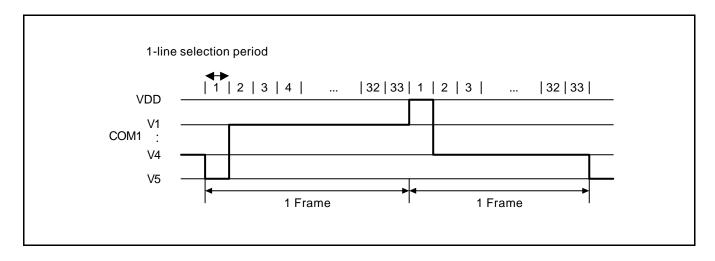

- Programmable duty cycle: 1/17, 1/33 (refer to Table 1)

- Internal oscillator with an external resistor

- Low power consumption

- TCP or bare chip available

**Table 1. Programmable Duty Cycles**

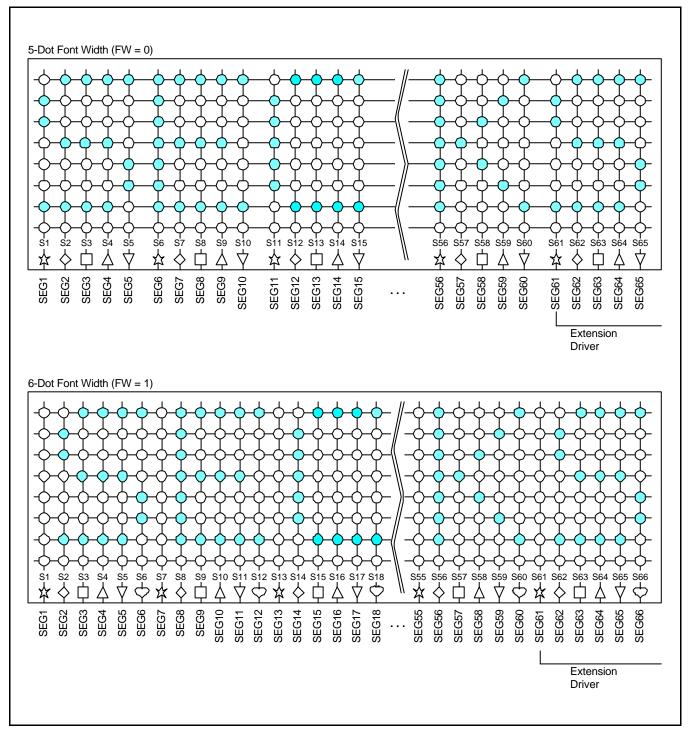

### 1) 5-dot Font Width

| Display |                   | Single-chip              | Operation | With Extens                 | ion Driver     |

|---------|-------------------|--------------------------|-----------|-----------------------------|----------------|

| Line    | <b>Duty Ratio</b> | Displayable              | Possible  | Displayable                 | Possible icons |

| Numbers |                   | characters               | icons     | characters                  |                |

| 1       | 1/17              | 1 line of 24 characters  | 60        | 1 line of 52 characters     | 80             |

| 2       | 1/33              | 2 lines of 24 characters | 60        | 2 lines of 32<br>characters | 80             |

| 4       | 1/33              | 4 lines of 12 characters | 60        | 4 lines of 20 characters    | 80             |

### 2) 6-dot Font Width

| Display |            | Single-chip              | Operation      | With Extension Driver    |                |  |  |  |  |

|---------|------------|--------------------------|----------------|--------------------------|----------------|--|--|--|--|

| Line    | Duty Ratio | Displayable              | Possible icons | Displayable              | Possible icons |  |  |  |  |

| Numbers |            | characters               |                | characters               |                |  |  |  |  |

| 1       | 1/17       | 1 line of 20 characters  | 60             | 1 line of 50 characters  | 96             |  |  |  |  |

| 2       | 1/33       | 2 lines of 20 characters | 60             | 2 lines of 30 characters | 96             |  |  |  |  |

| 4       | 1/33       | 4 lines of 10 characters | 60             | 4 lines of 20 characters | 96             |  |  |  |  |

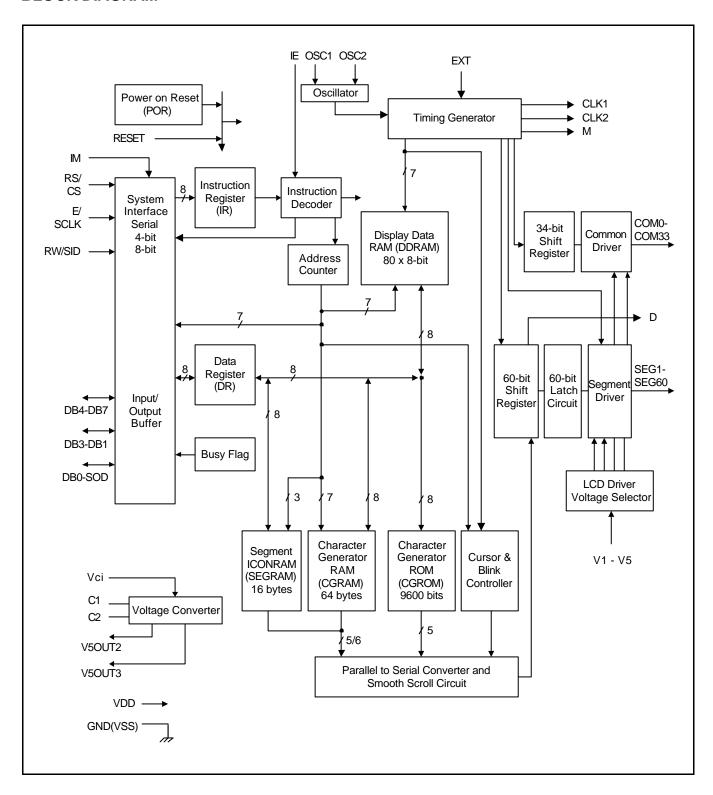

### **BLOCK DIAGRAM**

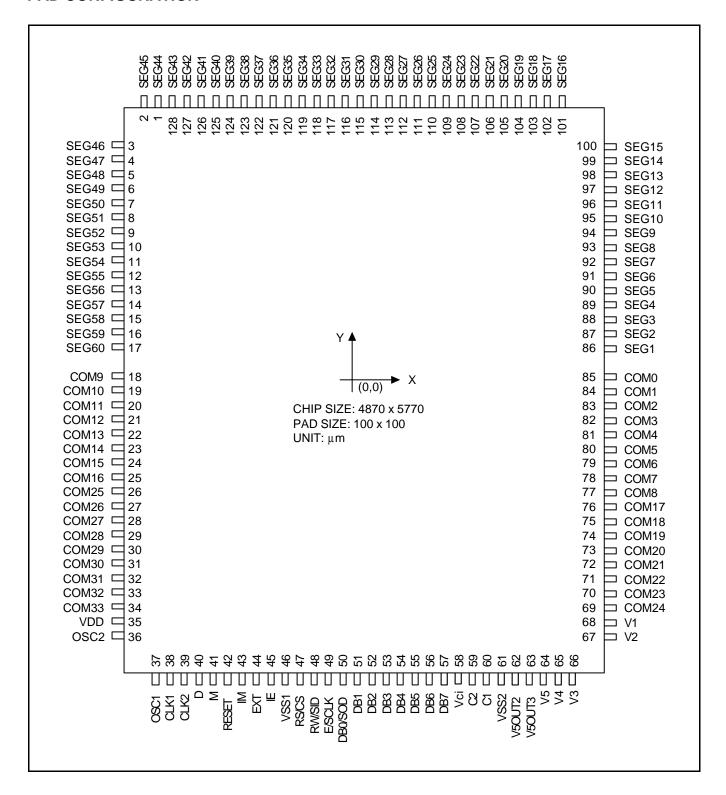

### PAD CONFIGURATION

## **PAD CENTER COORDINATES**

| Pad  | Pad   | Coord | dinate | Pad  | Pad     | Coord | linate | Pad  | Pad   | Coor | dinate |

|------|-------|-------|--------|------|---------|-------|--------|------|-------|------|--------|

| Num. | Name  | Х     | Υ      | Num. | Name    | Х     | Υ      | Num. | Name  | Х    | Υ      |

| 1    | SEG44 | -1687 | 2719   | 44   | EXT     | -986  | -2719  | 87   | SEG2  | 2269 | 497    |

| 2    | SEG45 | -1812 | 2719   | 45   | ΙE      | -861  | -2719  | 88   | SEG3  | 2269 | 622    |

| 3    | SEG46 | -2269 | 2122   | 46   | VSS1    | -736  | -2719  | 89   | SEG4  | 2269 | 747    |

| 4    | SEG47 | -2269 | 1997   | 47   | RS/CS   | -611  | -2719  | 90   | SEG5  | 2269 | 872    |

| 5    | SEG48 | -2269 | 1872   | 48   | RW/SID  | -486  | -2719  | 91   | SEG6  | 2269 | 997    |

| 6    | SEG49 | -2269 | 1747   | 49   | E/SCLK  | -361  | -2719  | 92   | SEG7  | 2269 | 1122   |

| 7    | SEG50 | -2269 | 1622   | 50   | DB0/SOD | -236  | -2719  | 93   | SEG8  | 2269 | 1247   |

| 8    | SEG51 | -2269 | 1497   | 51   | DB1     | -111  | -2719  | 94   | SEG9  | 2269 | 1372   |

| 9    | SEG52 | -2269 | 1372   | 52   | DB2     | 14    | -2719  | 95   | SEG10 | 2269 | 1497   |

| 10   | SEG53 | -2269 | 1247   | 53   | DB3     | 139   | -2719  | 96   | SEG11 | 2269 | 1622   |

| 11   | SEG54 | -2269 | 1122   | 54   | DB4     | 264   | -2719  | 97   | SEG12 | 2269 | 1747   |

| 12   | SEG55 | -2269 | 997    | 55   | DB5     | 389   | -2719  | 98   | SEG13 | 2269 | 1872   |

| 13   | SEG56 | -2269 | 872    | 56   | DB6     | 514   | -2719  | 99   | SEG14 | 2269 | 1997   |

| 14   | SEG57 | -2269 | 747    | 57   | DB7     | 639   | -2719  | 100  | SEG15 | 2269 | 2122   |

| 15   | SEG58 | -2269 | 622    | 58   | Vci     | 764   | -2719  | 101  | SEG16 | 1813 | 2719   |

| 16   | SEG59 | -2269 | 497    | 59   | C2      | 889   | -2719  | 102  | SEG17 | 1688 | 2719   |

| 17   | SEG60 | -2269 | 372    | 60   | C1      | 1014  | -2719  | 103  | SEG18 | 1563 | 2719   |

| 18   | СОМ9  | -2269 | 134    | 61   | VSS2    | 1139  | -2719  | 104  | SEG19 | 1438 | 2719   |

| 19   | COM10 | -2269 | 9      | 62   | V5OUT2  | 1264  | -2719  | 105  | SEG20 | 1313 | 2719   |

| 20   | COM11 | -2269 | -116   | 63   | V5OUR3  | 1389  | -2719  | 106  | SEG21 | 1188 | 2719   |

| 21   | COM12 | -2269 | -241   | 64   | V5      | 1514  | -2719  | 107  | SEG22 | 1063 | 2719   |

| 22   | COM13 | -2269 | -366   | 65   | V4      | 1639  | -2719  | 108  | SEG23 | 938  | 2719   |

| 23   | COM14 | -2269 | -491   | 66   | V3      | 1764  | -2719  | 109  | SEG24 | 813  | 2719   |

| 24   | COM15 | -2269 | -616   | 67   | V2      | 2269  | -2116  | 110  | SEG25 | 688  | 2719   |

| 25   | COM16 | -2269 | -741   | 68   | V1      | 2269  | -1991  | 111  | SEG26 | 563  | 2719   |

| 26   | COM25 | -2269 | -866   | 69   | COM24   | 2269  | -1866  | 112  | SEG27 | 438  | 2719   |

| 27   | COM26 | -2269 | -991   | 70   | COM23   | 2269  | -1741  | 113  | SEG28 | 313  | 2719   |

| 28   | COM27 | -2269 | -1116  | 71   | COM22   | 2269  | -1616  | 114  | SEG29 | 188  | 2719   |

| 29   | COM28 | -2269 | -1241  | 72   | COM21   | 2269  | -1491  | 115  | SEG30 | 63   | 2719   |

| 30   | COM29 | -2269 | -1366  | 73   | COM20   | 2269  | -1366  | 116  | SEG31 | -62  | 2719   |

| 31   | COM30 | -2269 | -1491  | 74   | COM19   | 2269  | -1241  | 117  | SEG32 | -187 | 2719   |

| 32   | COM31 | -2269 | -1616  | 75   | COM18   | 2269  | -1116  | 118  | SEG33 | -312 | 2719   |

# PAD CENTER COORDINATES (Continued)

| Pad  | Pad   | Coord | dinate | Pad  | Pad   | Coord | linate | Pad  | Pad   | Coor  | dinate |

|------|-------|-------|--------|------|-------|-------|--------|------|-------|-------|--------|

| Num. | Name  | Х     | Y      | Num. | Name  | Х     | Υ      | Num. | Name  | Х     | Y      |

| 33   | COM32 | -2269 | -1741  | 76   | COM17 | 2269  | -991   | 119  | SEG34 | -437  | 2719   |

| 34   | COM33 | -2269 | -1866  | 77   | COM8  | 2269  | -866   | 120  | SEG35 | -562  | 2719   |

| 35   | VDD   | -2269 | -1991  | 78   | COM7  | 2269  | -741   | 121  | SEG36 | -687  | 2719   |

| 36   | OSC2  | -2269 | -2116  | 79   | COM6  | 2269  | -616   | 122  | SEG37 | -812  | 2719   |

| 37   | OSC1  | -1861 | -2719  | 80   | COM5  | 2269  | -491   | 123  | SEG38 | -937  | 2719   |

| 38   | CLK1  | -1736 | -2719  | 81   | COM4  | 2269  | -366   | 124  | SEG39 | -1062 | 2719   |

| 39   | CLK2  | -1611 | -2719  | 82   | COM3  | 2269  | -241   | 125  | SEG40 | -1187 | 2719   |

| 40   | D     | -1486 | -2719  | 83   | COM2  | 2269  | -116   | 126  | SEG41 | -1312 | 2719   |

| 41   | М     | -1361 | -2719  | 84   | COM1  | 2269  | 9      | 127  | SEG42 | -1437 | 2719   |

| 42   | RESET | -1236 | -2719  | 85   | COM0  | 2269  | 134    | 128  | SEG43 | -1562 | 2719   |

| 43   | IM    | -1111 | -2719  | 86   | SEG1  | 2269  | 372    |      |       |       |        |

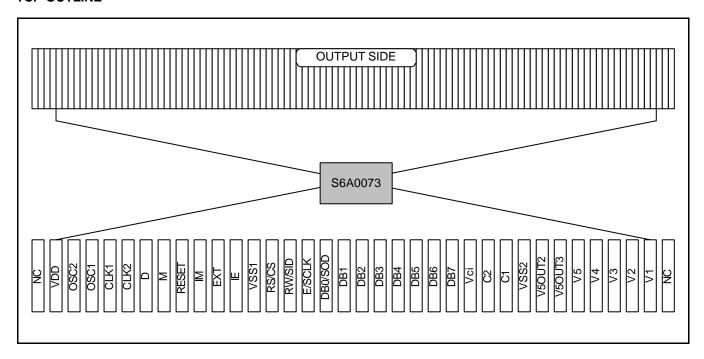

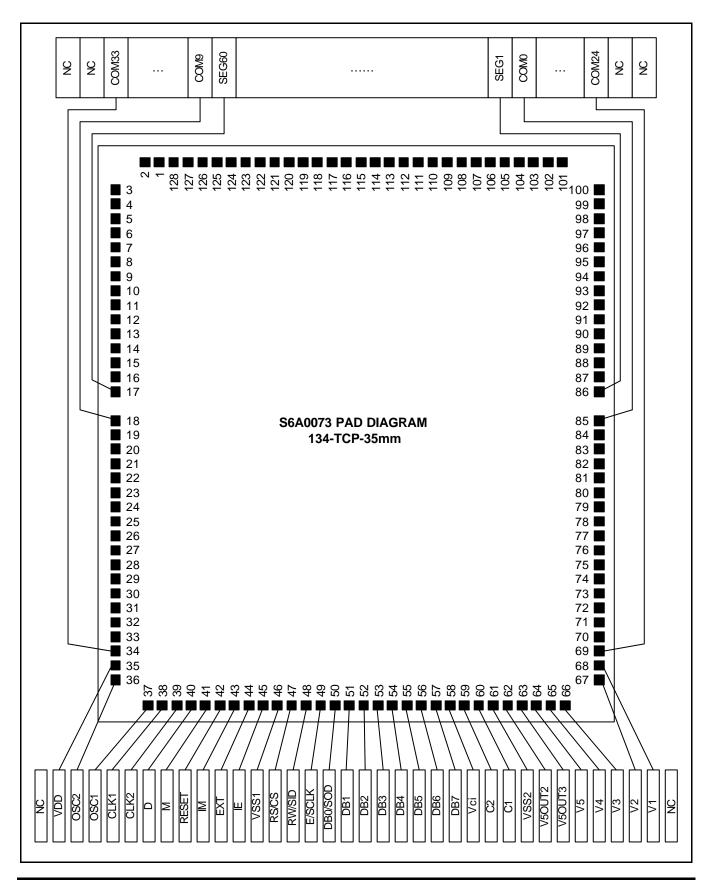

## PIN CONFIGURATION OF TCP

### **TCP OUTLINE**

## **PIN DESCRIPTION**

| Pin (No)                           | I/O                 | Name                                    | Description                                                                                                                                             | Interface                            |

|------------------------------------|---------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| V <sub>DD</sub> (35)               | -                   | Power supply                            | for logical circuit (+3V, +5V)                                                                                                                          | Power Supply                         |

| VSS1, VSS2<br>(46, 61)             |                     |                                         | 0V (GND)                                                                                                                                                |                                      |

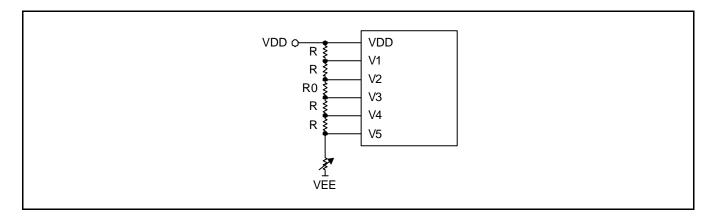

| V1-V5 (68 - 64)                    |                     |                                         | Bias voltage level for LCD driving                                                                                                                      |                                      |

| Vci (58)                           | I                   |                                         | Input voltage to the voltage converter to generate LCD drive voltage (Vci = 1.0 to 4.5V).                                                               |                                      |

| SEG1 - SEG60<br>(86 -128, 1- 17)   | 0                   | Segment output                          | Segment signal output for LCD drive.                                                                                                                    | LCD                                  |

| COM0 - COM33<br>(85 - 69, 18 - 34) | 0                   | Common output                           | Common signal output for LCD drive                                                                                                                      | LCD                                  |

| OSC1, OSC2<br>(37, 36)             | I(OSC1),<br>O(OSC2) | Oscillator                              | When using internal oscillator, connect external Rf resistor. If external clock is used, connect it to OSC1.                                            | External resistor/oscilla tor (OSC1) |

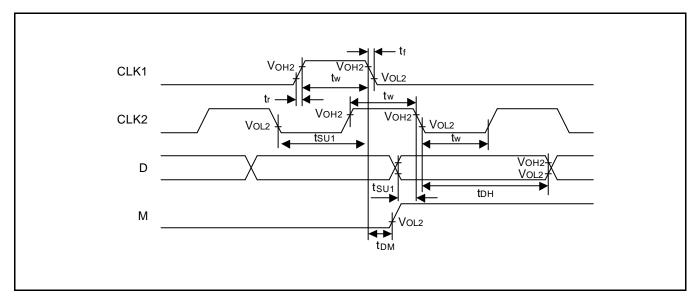

| CLK1, CLK2<br>(38, 39)             | 0                   | Latch (CLK1)/<br>Shift (CLK2) clock     | When EXT = "High", each outputs latch clock and shift clock for extension driver.                                                                       | Extension<br>driver                  |

| C1, C2<br>(60, 59)                 | I                   | External capacitance input              | To use the voltage converter (2 times /3 times), these pins must be connected to the external capacitance.                                              | External capacitance                 |

| M (41)                             | 0                   | Alternated signal for LCD driver output | When EXT = "High", outputs the alternating signal to convert LCD driver waveform to AC for Extension driver.                                            | Extension<br>driver                  |

| D(40)                              | 0                   | Display data interface                  | When EXT = "High", outputs extension driver data (the 61th dot's data)                                                                                  | Extension<br>driver                  |

| EXT(44)                            | l                   | Extension driver control signal         | When EXT = "High", makes extension driver control signal enable, When EXT = "Low", suppress extra current consumption and CLK1,CLK2,M,D should be open. | -                                    |

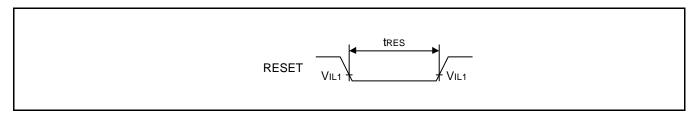

| RESET (42)                         | I                   | Reset pin                               | Initialized to Low                                                                                                                                      | _                                    |

| IE (45)                            | I                   | Selection pin of instruction set.       | When IE = "High", instruction set is selected as Table 6.                                                                                               |                                      |

|                                    |                     |                                         | When IE = "Low", instruction set is selected as Table 10.                                                                                               |                                      |

# PIN DESCRIPTION (continued)

| Pin(No)                | I/O    | Name                                  | Description                                                                                                                                                                                                 | Interface          |

|------------------------|--------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| V5OUT2 (62)            | 0      | Two times converter output            | The value of Vci is converted two times. To use three times converter, the same capacitance as that of C1-C2 should be connected here.                                                                      | V5/<br>capacitance |

| V5OUT3 (63)            |        | Three times converter output          | The value of Vci is converted three times.                                                                                                                                                                  | V5                 |

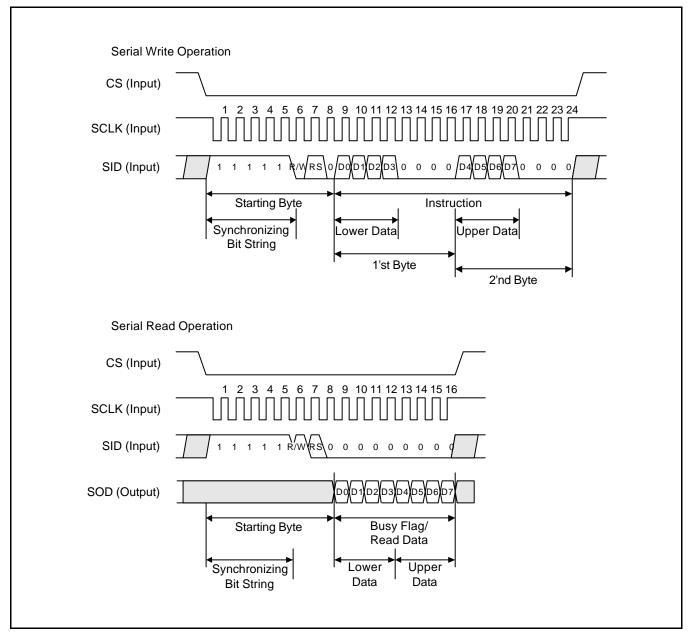

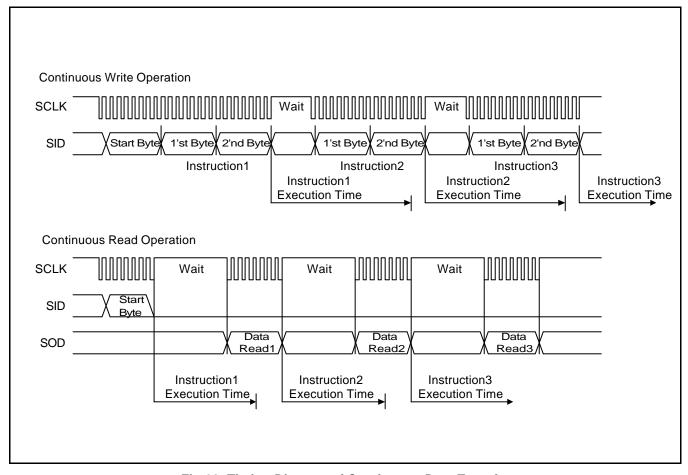

| IM (43)                | I      | Interface mode selection              | Select Interface mode with the MPU. When IM = "Low" : serial mode, When IM = "High" : 4-bit/8-bit bus mode.                                                                                                 | Ι                  |

| RS/CS (47)             | I      | Register select<br>/Chip select       | When bus mode, used as register selection input. When RS/CS = "High", Data register is selected. When RS/CS = "Low", Instruction register is selected.  In serial mode, used as chip selection              | MPU                |

|                        |        |                                       | input. When RS/CS = "Low", selected. When RS/CS = "High", not selected.(Low access enable)                                                                                                                  |                    |

| RW/SID (48)            | I      | Read, write<br>/Serial input data     | In bus mode, used as read/write selection input.  When RW/SID = "High", read operation When RW/SID = "Low", write operation. In serial mode, used for data input pin.                                       | MPU                |

| E/SCLK (49)            | I      | Read, write enable<br>/Serial clock   | When bus mode, used as read, write enable signal.                                                                                                                                                           | MPU                |

|                        |        |                                       | When serial mode, used as serial clock input pin.                                                                                                                                                           |                    |

| DB0/SOD (50)           | I/O, O | Data bus 0 bit<br>/Serial output data | In 8-bit bus mode, used as lowest bi-<br>directional data bit. During 4-bit bus mode,<br>Open this pin.                                                                                                     | MPU                |

|                        |        |                                       | In serial mode, used as serial data output pin. If not in read operation, open this pin.                                                                                                                    |                    |

| DB1 - DB3<br>(51 - 53) | I/O    | Data bus 1- 7                         | In 8-bit bus mode, used as low order bidirectional data bus.                                                                                                                                                | MPU                |

|                        |        |                                       | During 4-bit bus mode or serial mode, open these pins.                                                                                                                                                      |                    |

| DB4 - DB7<br>(54 - 57) |        |                                       | In 8-bit bus mode, used as high order bi-<br>directional data bus. In case of 4-bit bus<br>mode, used as both high and low order.<br>DB7 used for Busy Flag output.<br>During serial mode, open these pins. | MPU                |

### **FUNCTION DESCRIPTION**

#### **System Interface**

This chip has all three kinds of interface type with MPU: serial, 4-bit bus and 8-bit bus. Serial and bus(4-bit/8-bit) are selected by IM input, and 4-bit bus and 8-bit bus are selected by DL bit in the instruction register. During read or write operation, two 8-bit registers are used. one is data register (DR), the other is instruction register(IR). The data register(DR) is used as temporary data storage place for being written into or read from DDRAM/CGRAM/SEGRAM, target RAM is selected by RAM address setting instruction. Each internal operation, reading from or writing into RAM, is done automatically. Hence, after MPU reads DR data, the data in the next DDRAM/CGRAM/SEGRAM address is transferred into DR automatically. Also after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM/SEGRAM automatically. The Instruction register(IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data. To select register, use RS/CS input pin in 4-bit/8-bit bus mode(IM = "High") or RS bit in serial mode(IM = "Low").

RS R/W Operation

L Instruction Write operation (MPU writes Instruction code into IR)

L H Read Busy flag(DB7) and address counter (DB0 – DB6)

H L Data Write operation (MPU writes data into DR)

H Data Read operation (MPU reads data from DR)

Table 2. Various Kinds of Operations according to RS and R/W Bits

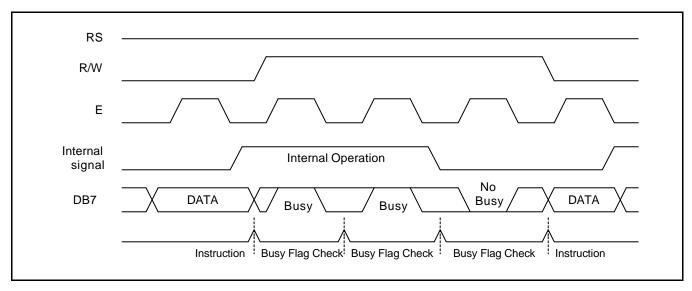

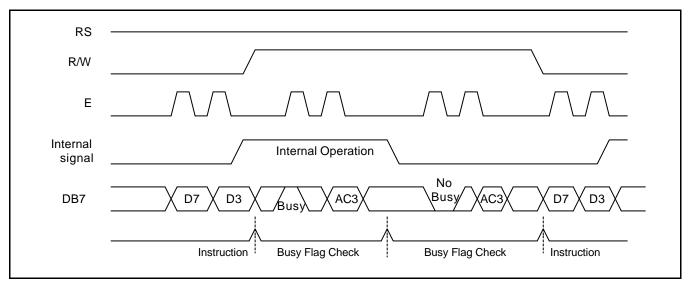

### **Busy Flag (BF)**

When BF = "High", it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when RS = Low and R/W = High (Read Instruction Operation), through DB7. Before executing the next instruction, be sure that BF is not High.

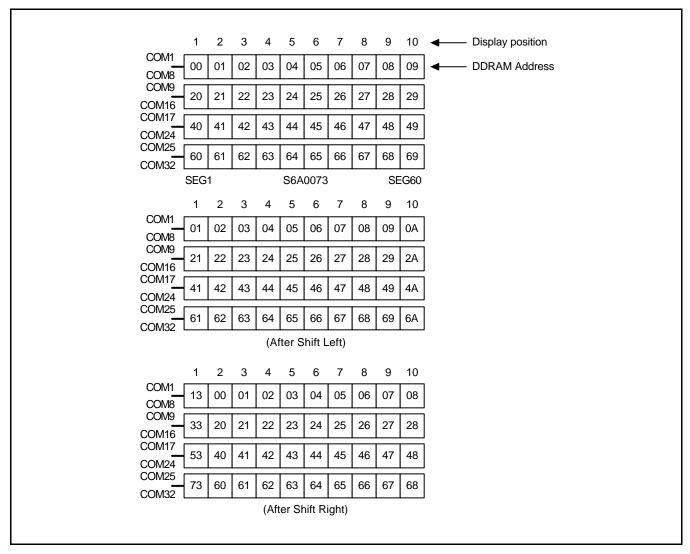

### **Display Data RAM (DDRAM)**

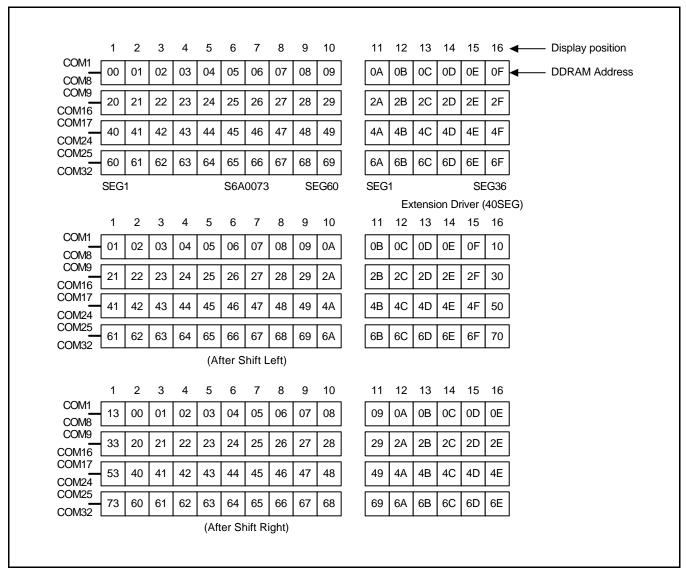

DDRAM stores display data of maximum  $80 \times 8$  bits (80 characters). DDRAM address is set in the address counter (AC) as a hexadecimal number. (refer to Figure 1.)

Figure 1. DDRAM Address

### 1) Display of 5-dot Font Width Character

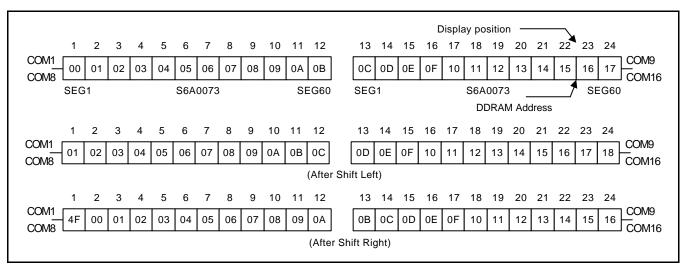

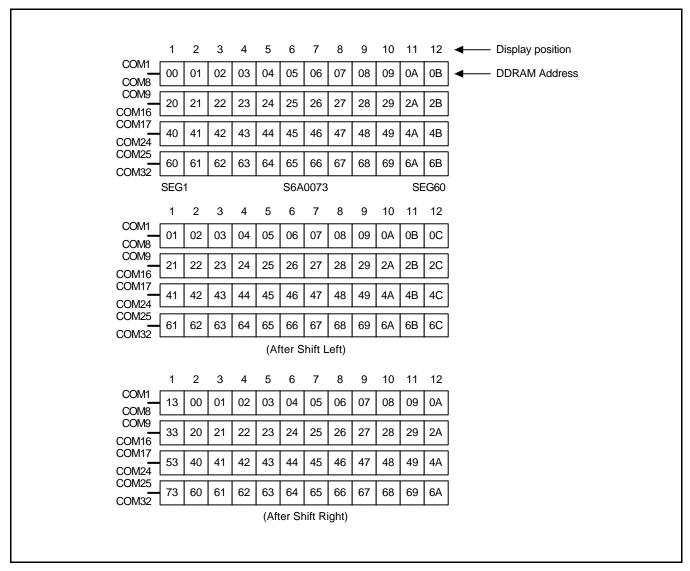

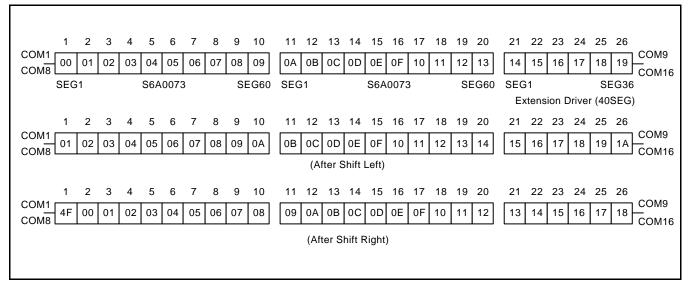

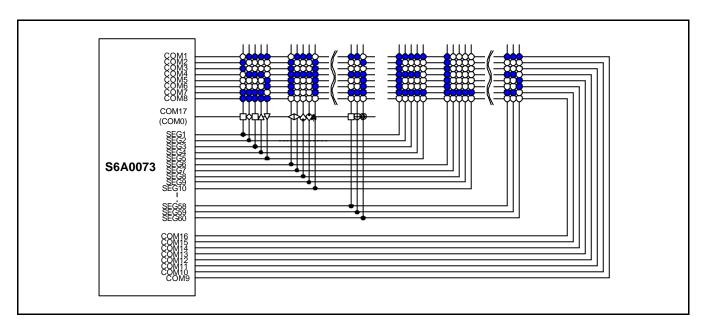

### (1) 5-dot 1-line Display

In case of 1 line display with 5-dot font, the address range of DDRAM is 00H - 4FH (refer to Figure 2). When EXT = "High", extension driver will be used. Figure 3 shows the example that 40 segment extension driver is added

Figure 2. 1-line ' 24ch. Display (5-dot font width)

Figure 3. 1-line ^ 32ch. Display with 40 SEG. extension driver (5-dot font width)

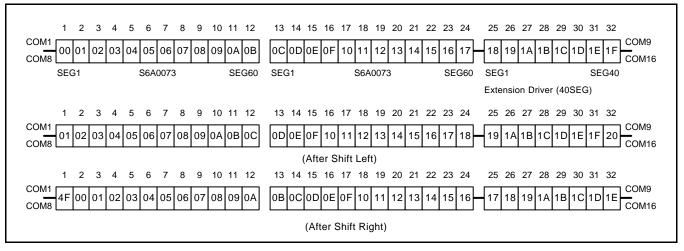

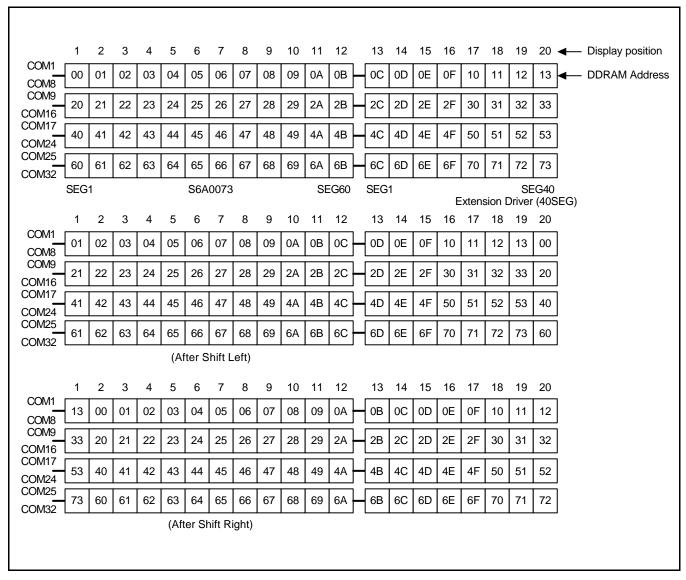

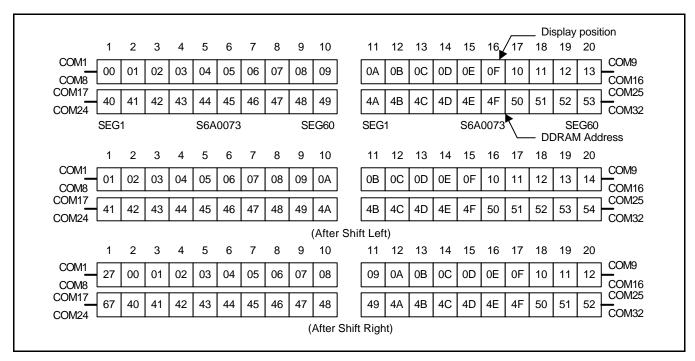

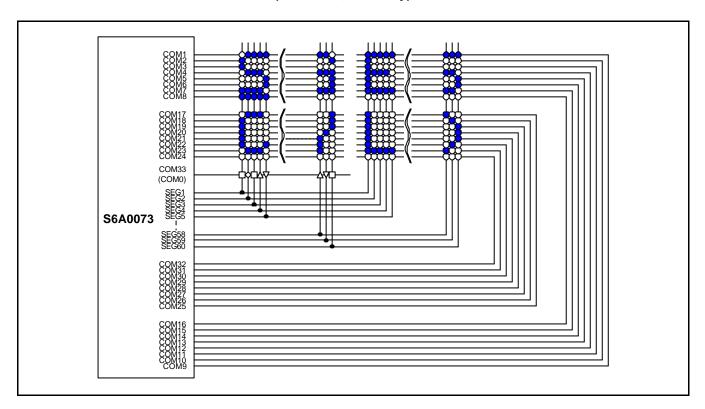

### (2) 5-dot 2-line Display

In case of 2 line display with 5-dot font, the address range of DDRAM is 00H - 27H,40H - 67H (refer to Figure 4). When EXT = "High", extension driver will be used. Figure 5 shows the example that 40 segment extension driver is added.

Figure 4. 2-line 24ch. Display (5-dot Font Width)

Figure 5. 2-line 1 32ch. Display with 40 SEG. Extension Driver (5-dot Font Width)

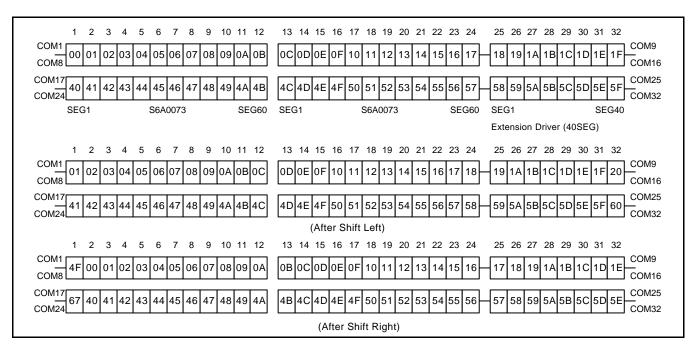

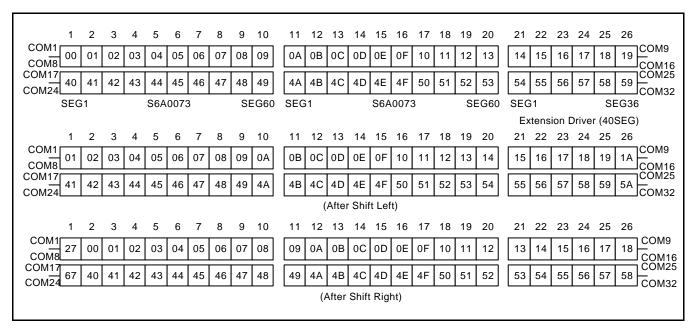

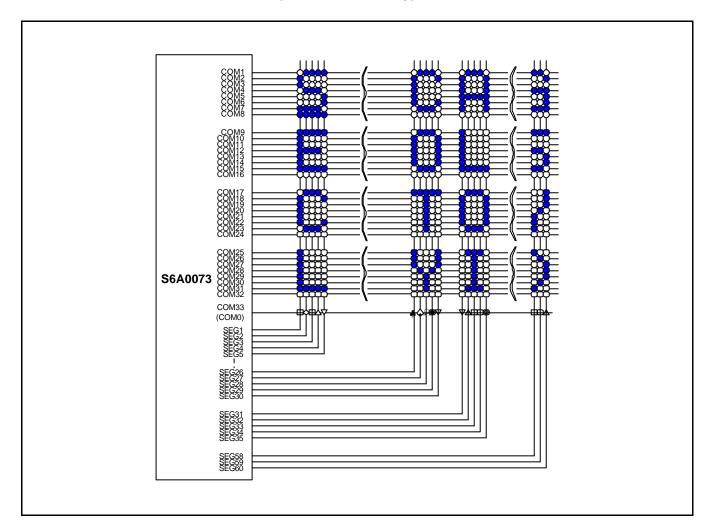

### (3) 5-dot 4-line Display

In case of 4 line display with 5-dot font, the address range of DDARM is 00H - 13H, 20H - 33H, 40H - 53H, 60H - 73H (refer to Figure 6). When EXT = "High", extension driver will be used. Figure 7 shows the example that 40 segment extension driver is added.

Figure 6. 4-line 12ch. Display (5-dot Font Width)

Figure 7. 4-line ^ 20ch. Display with 40 SEG. Extension Driver (5-dot Font Width)

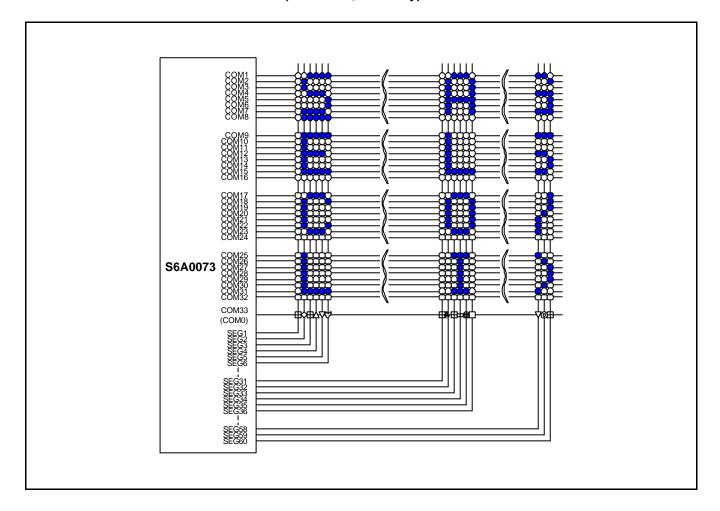

### 2) Display of 6-dot Font Width Character

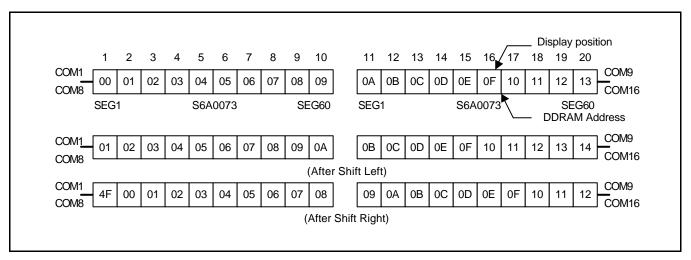

### (1) 6-dot 1-line Display

In case of 1 line display with 6-dot font, the address range of DDRAM is 00H - 4FH (refer to Figure 8). When EXT = "High", extension driver will be used. Figure 9 shows the example that 40 segment extension driver is added.

Figure 8. 1-line 20ch. Display (6-dot Font Width)

Figure 9. 1-line ^ 26ch. Display with 40 SEG. Extension Driver (6-dot Font Width)

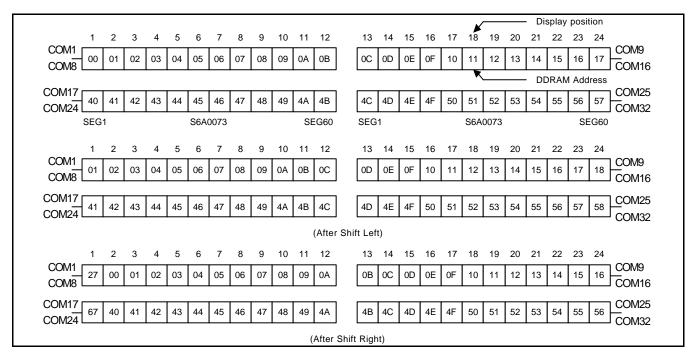

### (2) 6-dot 2-line Display

In case of 2 line display with 6-dot font, the address range of DDRAM is 00H - 27H, 40H - 67H. (refer to Figure 10) When EXT = "High", extension driver will be used. Figure 11 shows the example that 40 segment extension driver is added.

Figure 10. 2-line 20ch. Display (6-dot Font Width)

Figure 11. 2-line 1 26ch. Display with 40 SEG. Extension Driver (6-dot Font Width)

### (3) 6-dot 4-line Display

In case of 4 line display with 6-dot font, the address range of DDARM is 00H-13H, 20H-33H, 40H-53H, 60H-73H (refer to Figure 12). When EXT = "High", extension driver will be used. Figure 13 shows the example that 40 segment extension driver is added.

Figure 12. 4-line 10 ch. Display (6-dot Font Width)

Figure 13. 4-line 1 16ch. Display with 40 SEG. Driver (6-dot Font Width)

### **Timing Generation Circuit**

Timing generation circuit generates clock signals for the internal operations.

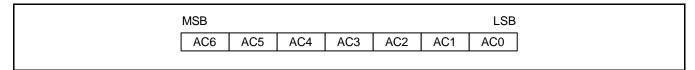

### **Address Counter (AC)**

Address Counter(AC) stores DDRAM/CGRAM/SEGRAM address, transferred from IR. After writing into (reading from) DDRAM/CGRAM/SEGRAM, AC is automatically increased (decreased) by 1. When RS = "Low" and R/W = "High", AC can be read through DB0-DB6 ports.

### **Cursor/Blink Control Circuit**

It controls cursor/blink ON/OFF and black/white inversion at cursor position.

### **LCD Driver Circuit**

LCD Driver circuit has 34 common and 60 segment signals for LCD driving. Data from SEGRAM/CGRAM/CGROM is transferred to 60-bit segment latch serially, which is then stored to a 60-bit shift latch. When each com is selected by 34-bit common register, segment data also output through segment driver from 100-bit segment latch. In case of 1-line display mode, COM0 - COM17 have a 1/17 duty ratio, and in 2-line or 4-line mode, COM0-COM33 have a 1/33 duty ratio.

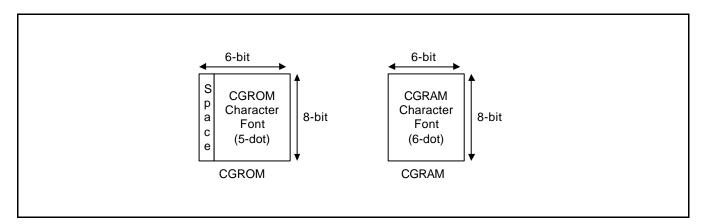

### **CGROM (Character Generator ROM)**

CGROM has 5  $\times$  8-dot 240 character pattern.

### **CGRAM (Character Generator RAM)**

CGRAM has up to  $5 \times 8$ -dot 8 characters. By writing font data to CGRAM, user defined character can be used (refer to Table 4).

Table 4. Relationship between Character Code (DDRAM) and Character Pattern (CGRAM)

### — 5 ´ 8 dots Character Pattern

| Character Code (DDRAM data) |    |    |    |    |    |    |    |    | CGR | RAM       | Add | ress       |           |    |    | CC | <b>SRAI</b> | VI Da | ta |    |    | Pattern   |

|-----------------------------|----|----|----|----|----|----|----|----|-----|-----------|-----|------------|-----------|----|----|----|-------------|-------|----|----|----|-----------|

| D7                          | D6 | D5 | D4 | D3 | D2 | D1 | D0 | A5 | A4  | <b>A3</b> | A2  | <b>A</b> 1 | <b>A0</b> | P7 | P6 | P5 | P4          | P3    | P2 | P1 | P0 | Number    |

| 0                           | 0  | 0  | 0  | Х  | 0  | 0  | 0  | 0  | 0   | 0         | 0   | 0          | 0         | В1 | В0 | Х  | 0           | 1     | 1  | 1  | 0  | Pattern 1 |

|                             |    |    |    |    |    |    |    |    |     |           | 0   | 0          | 1         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 0   | 1          | 0         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    | •   |           | 0   | 1          | 1         |    | •  |    | 1           | 1     | 1  | 1  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 1   | 0          | 0         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    | •  |    |    |    |    |     |           | 1   | 0          | 1         |    | •  |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    | ·  |    |    |    |    |    | ·   |           | 1   | 1          | 0         |    | •  |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 1   | 1          | 1         |    |    |    | 0           | 0     | 0  | 0  | 0  |           |

|                             |    |    |    |    |    |    |    |    |     |           |     |            |           |    |    |    |             |       |    |    |    |           |

|                             |    |    |    |    |    |    |    |    |     |           |     |            |           |    |    |    |             |       |    |    |    |           |

| 0                           | 0  | 0  | 0  | Х  | 1  | 1  | 1  | 1  | 1   | 1         | 0   | 0          | 0         | В1 | B0 | Х  | 1           | 0     | 0  | 0  | 1  | Pattern 8 |

|                             |    |    |    |    |    |    |    |    |     |           | 0   | 0          | 1         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 0   | 1          | 0         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    | •   |           | 0   | 1          | 1         |    | •  |    | 1           | 1     | 1  | 1  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 1   | 0          | 0         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 1   | 0          | 1         |    |    |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    | •  |    |    |    |    | •   |           | 1   | 1          | 0         |    | •  |    | 1           | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |     |           | 1   | 1          | 1         |    |    |    | 0           | 0     | 0  | 0  | 0  |           |

### 6 1 8 dots Character Pattern

| Character Code (DDRAM data) |    |    |    |    |    |    |    |    | CGF        | RAM       | Add | ress       |    |            |    | CC | RAI | VI Da | ta |    |    | Pattern   |

|-----------------------------|----|----|----|----|----|----|----|----|------------|-----------|-----|------------|----|------------|----|----|-----|-------|----|----|----|-----------|

| D7                          | D6 | D5 | D4 | D3 | D2 | D1 | D0 | A5 | <b>A</b> 4 | <b>A3</b> | A2  | <b>A</b> 1 | A0 | <b>P</b> 7 | P6 | P5 | P4  | Р3    | P2 | P1 | P0 | Number    |

| 0                           | 0  | 0  | 0  | Х  | 0  | 0  | 0  | 0  | 0          | 0         | 0   | 0          | 0  | В1         | B0 | 0  | 0   | 1     | 1  | 1  | 0  | Pattern 1 |

|                             |    |    |    |    |    |    |    |    |            |           | 0   | 0          | 1  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 0   | 1          | 0  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    | •          |           | 0   | 1          | 1  |            |    | 0  | 1   | 1     | 1  | 1  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 1   | 0          | 0  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    | :          |           | 1   | 0          | 1  |            | :  | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 1   | 1          | 0  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 1   | 1          | 1  |            |    | 0  | 0   | 0     | 0  | 0  | 0  |           |

|                             |    |    |    |    |    |    |    |    |            |           |     |            |    |            |    |    |     |       |    |    |    |           |

|                             |    |    |    | •  |    |    |    |    |            |           |     |            |    |            |    |    |     |       |    |    |    |           |

| 0                           | 0  | 0  | 0  | Х  | 1  | 1  | 1  | 1  | 1          | 1         | 0   | 0          | 0  | В1         | B0 | 0  | 1   | 0     | 0  | 0  | 1  | Pattern 8 |

|                             |    |    |    |    |    |    |    |    |            |           | 0   | 0          | 1  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 0   | 1          | 0  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 0   | 1          | 1  |            |    | 0  | 1   | 1     | 1  | 1  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 1   | 0          | 0  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    | :          |           | 1   | 0          | 1  |            | :  | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 1   | 1          | 0  |            |    | 0  | 1   | 0     | 0  | 0  | 1  |           |

|                             |    |    |    |    |    |    |    |    |            |           | 1   | 1          | 1  |            |    | 0  | 0   | 0     | 0  | 0  | 0  |           |

### NOTES:

1. When Be(Blink Enable bit) = "High", blink is controlled by B1 and B0 bit. In case of 5-dot font width, when B1 = "1", enabled dots of P0 - P4 will blink, and when B1 = "0" and B0 = "1", enabled dots in P4 will blink, when B1 = "0" and B0 = "0", blink will not happen.

In case of 6-dot font width, when B1 = "1", enabled dots of P0-P5 will blink, and when B1 = "0" and B0 = "1", enabled dots of P5 will blink, when B1 = "0" and B0 = "0", blink will not happen.

2. "X" is don't care.

### **SEGRAM (Segment Icon RAM)**

SEGRAM has segment control data and segment pattern data. During 1-line display mode, COM0(COM17) makes the data of SEGRAM enable to display icons. When used in 2/4-line display mode COM0(COM33) does that. Its higher 2-bits are blinking control data, and lower 6-bits are pattern data (refer to Table 5 and Figure 14).

Table 5. Relationship between SEGRAM Address and Display Pattern

| SEG | RAM | Add | ress |    |    |    |        |       | SE  | GRAN | l Data | Disp | lay P | attern |        |       |     |     |     |

|-----|-----|-----|------|----|----|----|--------|-------|-----|------|--------|------|-------|--------|--------|-------|-----|-----|-----|

|     |     |     |      |    |    | 5- | dot Fo | nt Wi | dth |      |        |      |       | 6-0    | dot Fo | nt Wi | dth |     |     |

| А3  | A2  | A1  | A0   | D7 | D6 | D5 | D4     | D3    | D2  | D1   | D0     | D7   | D6    | D5     | D4     | D3    | D2  | D1  | D0  |

| 0   | 0   | 0   | 0    | В1 | В0 | Χ  | S1     | S2    | S3  | S4   | S5     | B1   | В0    | S1     | S2     | S3    | S4  | S5  | S6  |

| 0   | 0   | 0   | 1    | В1 | В0 | Χ  | S6     | S7    | S8  | S9   | S10    | B1   | В0    | S7     | S8     | S9    | S10 | S11 | S12 |

| 0   | 0   | 1   | 0    | В1 | В0 | Χ  | S11    | S12   | S13 | S14  | S15    | B1   | В0    | S13    | S14    | S15   | S16 | S17 | S18 |

| 0   | 0   | 1   | 1    | В1 | В0 | Χ  | S16    | S17   | S18 | S19  | S20    | B1   | В0    | S19    | S20    | S21   | S22 | S23 | S24 |

| 0   | 1   | 0   | 0    | B1 | В0 | Χ  | S21    | S22   | S23 | S24  | S25    | B1   | В0    | S25    | S26    | S27   | S28 | S29 | S30 |

| 0   | 1   | 0   | 1    | B1 | В0 | Χ  | S26    | S27   | S28 | S29  | S30    | B1   | В0    | S31    | S32    | S33   | S34 | S35 | S36 |

| 0   | 1   | 1   | 0    | B1 | В0 | Χ  | S31    | S32   | S33 | S34  | S35    | B1   | В0    | S37    | S38    | S39   | S40 | S41 | S42 |

| 0   | 1   | 1   | 1    | B1 | В0 | Χ  | S36    | S37   | S38 | S39  | S40    | B1   | В0    | S43    | S44    | S45   | S46 | S47 | S48 |

| 1   | 0   | 0   | 0    | B1 | В0 | Χ  | S41    | S42   | S43 | S44  | S45    | B1   | В0    | S49    | S50    | S51   | S52 | S53 | S54 |

| 1   | 0   | 0   | 1    | B1 | В0 | Χ  | S46    | S47   | S48 | S49  | S50    | B1   | В0    | S55    | S56    | S57   | S58 | S59 | S60 |

| 1   | 0   | 1   | 0    | B1 | В0 | Χ  | S51    | S52   | S53 | S54  | S55    | B1   | В0    | S61    | S62    | S63   | S64 | S65 | S66 |

| 1   | 0   | 1   | 1    | B1 | В0 | Χ  | S56    | S57   | S58 | S59  | S60    | B1   | В0    | S67    | S68    | S69   | S70 | S71 | S72 |

| 1   | 1   | 0   | 0    | B1 | В0 | Χ  | S61    | S62   | S63 | S64  | S65    | B1   | В0    | S73    | S74    | S75   | S76 | S77 | S78 |

| 1   | 1   | 0   | 1    | В1 | В0 | Χ  | S66    | S67   | S68 | S69  | S70    | B1   | В0    | S79    | S80    | S81   | S82 | S83 | S84 |

| 1   | 1   | 1   | 0    | В1 | В0 | Χ  | S71    | S72   | S73 | S74  | S75    | B1   | В0    | S85    | S86    | S87   | S88 | S89 | S90 |

| 1   | 1   | 1   | 1    | B1 | B0 | Χ  | S76    | S77   | S78 | S79  | S80    | B1   | B0    | S91    | S92    | S93   | S94 | S95 | S96 |

### NOTES:

1. B1, B0 : Blinking control bit

|    | Control Bi | t  | Blinkin          | g Port           |

|----|------------|----|------------------|------------------|

| BE | B1         | В0 | 5-dot font width | 6-dot font width |

| 0  | Х          | Χ  | No blink         | No blink         |

| 1  | 0          | 0  | No blink         | No blink         |

| 1  | 0          | 1  | D4               | D5               |

| 1  | 1          | Χ  | D4 - D0          | D5 - D0          |

2. S1 - S80 : Icon pattern ON/OFF in 5-dot font width S1 - S96 : Icon pattern ON/OFF in 6-dot font width

3. "X" : don't care

Figure 14. Relationship between SEGRAM and Segment Display

### INSTRUCTION DESCRIPTION

### **OUTLINE**

To overcome the speed difference between internal clock of S6A0073 and MPU clock, S6A0073 performs internal operation by storing control information to IR or DR. The internal operation is determined according to the signal from MPU, composed of read/write and data bus. Instruction can be divided largely four kinds,

- (1) S6A0073 function set instructions (set display methods, set data length, etc.)

- (2) address set instructions to internal RAM

- (3) data transfer instructions with internal RAM

- (4) others.

The address of internal RAM is automatically increased or decreased by 1. When IE = "High", S6A0073 is operated according to Instruction Set 1 (Table 6) and when IE = "Low", S6A0073 is operated according to Instruction Set 2 (Table 10).

### **NOTE**

During internal operation, Busy Flag (DB7) is read High. Busy Flag check must be preceded the next instruction. When an MPU program with Busy Flag (DB7) checking is made, 1/2 f<sub>OSC</sub> is necessary for executing the next instruction by the falling edge of the 'E' signal after the Busy Flag (DB7) goes to "LOW".

## INSTRUCTION DESCRIPTION 1 (IE = "HIGH")

Table 6. Instruction Set 1

| Instruction                  |    |    |     |     | )   |     |     |     | Description | Execution time |     |                                                                                                                                                                                                                                                                                                                                             |                           |

|------------------------------|----|----|-----|-----|-----|-----|-----|-----|-------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                              | RE | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2         | DB1            | DB0 |                                                                                                                                                                                                                                                                                                                                             | (f <sub>OSC</sub> =70kHz) |

| Clear display                | Х  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0           | 0              | 1   | Write "20" to DDRAM, and set DDRAM address to "00H" from AC.                                                                                                                                                                                                                                                                                | 1.53ms                    |

| Return home                  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0           | 1              | х   | Set DDRAM address to "00H" from AC and return cursor to its original position if shifted. The contents of DDRAM are not changed.                                                                                                                                                                                                            | 1.53ms                    |

| Power down<br>mode           | 1  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0           | 1              | PD  | Set power down mode bit.<br>(PD = "1" : power down mode set,<br>PD = "0" : power down mode disable)                                                                                                                                                                                                                                         | 39µs                      |

| Entry mode<br>set            | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1           | I/D            | S   | Assign cursor moving direction, (I/D = "1": increment, I/D = "0": decrement, and display shift enable bit. (S = "1": make display shift of the enabled lines by the DS4-DS1 bits in the shift Enable instruction S = "0": display shift disable)                                                                                            | 39µs                      |

|                              | 1  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1           | 1              | B/D | Segment bidirectional function. (BID = "1": Seg60 →Seg1 BID = "0": Seg1 →Seg60)                                                                                                                                                                                                                                                             |                           |

| Display<br>ON/OFF<br>Control | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D           | С              | В   | Set display/cursor/blink on/off D = "1": display on, D = "0": display off, C = "1": cursor on, C = "0": cursor off, B = "1": blink on, B = "0": blink off.                                                                                                                                                                                  | 39µs                      |

| Extended function set        | 1  | 0  | 0   | 0   | 0   | 0   | 0   | 1   | FW          | B/W            | NW  | Assign font width, black/white inverting of cursor, and 4-line display mode control bit.  FW = "1" : 6-dot font width,  FW = "0" : 5-dot font width,  B/W = "1" : black/white inverting of cursor enable,  B/W = "0" : black/white inverting of cursor disable.  NW = "1" : 4-line display mode,  NW = "0" : 1-line or 2-line display mode. | 39µs                      |

**Table 6. Instruction Set 1 Continued**

| Instruction                |    |    |     | I   | nstru | ction | Code | •   |           |     |     | Description                                                                                                                                                                                                                                                                                                                                   | Execution time |

|----------------------------|----|----|-----|-----|-------|-------|------|-----|-----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                            | RE | RS | R/W | DB7 | DB6   | DB5   | DB4  | DB3 | DB2       | DB1 | DB0 |                                                                                                                                                                                                                                                                                                                                               | (fosc=70kHz)   |

| Cursor or<br>Display Shift | 0  | 0  | 0   | 0   | 0     | 0     | 1    | S/C | R/L       | X   | X   | Cursor or display shift.  S/C = "1" : display shift,  S/C = "0" : cursor shift,  R/L = "1" : shift to right,  R/L = "0" : shift to left.                                                                                                                                                                                                      | 39µs           |

| Shift Enable               | 1  | 0  | 0   | 0   | 0     | 0     | 1    | DS4 | DS3       | DS2 | DS1 | (when DH = "1")  Determine the line for display shift.  DS1 = "1/0": 1st line display shift enable/disable  DS2 = "1/0": 2nd line display shift enable/disable  DS3 = "1/0": 3rd line display shift enable/disable  DS4 = "1/0": 4th line display shift enable/disable.                                                                       | 39µs           |

| Scroll Enable              | 1  | 0  | 0   | 0   | 0     | 0     | 1    | HS4 | HS3       | HS2 | SH1 | (when DH = "0") Determine the line for horizontal smooth scroll. HS1 = "1/0" : 1st line dot scroll enable/disable HS2 = "1/0" : 2nd line dot scroll enable/disable HS3 = "1/0" : 3rd line dot scroll enable/disable HS4 = "1/0" : 4th line dot scroll enable/disable.                                                                         | 39µs           |

| Function Set               | 0  | 0  | 0   | 0   | 0     | 1     | DL   | Z   | RE (0)    | DH  | REV | Set interface data length  (DL = "1" : 8-bit, DL = "0" : 4-bit),  numbers of display line when NW = "0",  (N = "1" : 2-line, N = "0" : 1-line),  extension register, RE("0"), shift/scroll enable  DH = "1" : display shift enable  DH = "0" : dot scroll enable.  And reverse bit  REV = "1" : reverse display,  REV = "0" : normal display. | 39µs           |

|                            | 1  | 0  | 0   | 0   | 0     | 1     | DL   | Z   | RE<br>(1) | BE  | LP  | Set DL, N, RE("1") and CGRAM/SEGRAM blink enable (BE) BE = " 1/0" : CGRAM/SEGRAM blink enable/disable LP = "1" : low power mode LP = "0" : normal operation mode                                                                                                                                                                              | 39µs           |

Table 6. Instruction Set 1 continued

| Instruction                      |    |    |     | I   | nstru | ction | Code | )   |     |     |     | Description                                                                                                                                                         | Execution time    |

|----------------------------------|----|----|-----|-----|-------|-------|------|-----|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                  | RE | RS | R/W | DB7 | DB6   | DB5   | DB4  | DB3 | DB2 | DB1 | DB0 |                                                                                                                                                                     | (fosc=270kHz<br>) |

| Set CGRAM<br>Address             | 0  | 0  | 0   | 0   | 1     | AC5   | AC4  | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in address counter.                                                                                                                               | 39µs              |

| Set SEGRAM<br>Address            | 1  | 0  | 0   | 0   | 1     | Х     | Х    | AC3 | AC2 | AC1 | AC0 | Set SEGRAM address in address counter.                                                                                                                              | 39µs              |

| Set DDRAM<br>Address             | 0  | 0  | 0   | 1   | AC6   | AC5   | AC4  | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in address counter.                                                                                                                               | 39µs              |

| Set Scroll<br>Quantity           | 1  | 0  | 0   | 1   | Х     | SQ5   | SQ4  | SQ3 | SQ2 | SQ1 | SQ0 | Set the quantity of horizontal dot scroll.                                                                                                                          | 39µs              |

| Read Busy<br>flag and<br>Address | x  | 0  | 1   | BF  | AC6   | AC5   | AC4  | AC3 | AC2 | AC1 | AC0 | Can be known whether during internal operation or not by reading BF. The contents of address counter can also be read. BF = "1": busy state, BF = "0": ready state. | 0µs               |

| Write Data                       | Х  | 1  | 0   | D7  | D6    | D5    | D4   | D3  | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM/SEGRAM).                                                                                                                  | 43µs              |

| Read Data                        | Х  | 1  | 1   | D7  | D6    | D5    | D4   | D3  | D2  | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM/SEGRAM).                                                                                                                   | 43µs              |

**NOTE:** When an MPU program with Busy Flag (DB7) checking is mode, 1/2 f<sub>OSC</sub> is necessary for executing the next instruction by the falling edge of the "E" signal after the Busy Flag (DB7) goes to "low". "X" is don't care.

### **Display Clear**

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set DDRAM address to "00H" into AC (address counter). Return cursor to the original status, bring the cursor to the left edge on first line of the display. Make entry mode increment (I/D = "1").

### Return Home (RE = 0)

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Х   |

Return Home is cursor return home instruction. Set DDRAM address to "00H" into the address counter. Return cursor to its original site and return display to its original status, if shifted. Contents of DDRAM does not change.

### Power Down Mode Set (RE = 1)

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | PD  |

Power down mode enable bit set instruction. When PD = "High", it makes S6A0073 suppress current consumption except the current needed for data storage by executing next three functions.

- Make the output value of all the COM/SEG ports V<sub>DD</sub>

- Make the COM/SEG output value of extension driver V<sub>DD</sub> by setting D output to "High" and M output to "Low"

- Disable voltage converter to remove the current through the divide resistor of power supply.

This instruction can be used power sleep mode. When PD = "Low", power down mode becomes disabled.

### Entry Mode Set (RE = 0)

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |  |

Set the moving direction of cursor and display.

I/D : Increment/decrement of DDRAM address (cursor or blink)

When I/D = "High", cursor/blink moves to right and DDRAM address is increased by 1.

When I/D = "Low", cursor/blink moves to left and DDRAM address is decreased by 1.

When S = "High", after DDRAM write, the display of enabled line by DS1 - DS4 bits in the Shift Enable instruction is shifted to the right (I/D = "0") or to the left(I/D = "1"). But it will seem as if the cursor does not move.

When S = "Low", or DDRAM read, or CGRAM/SEGRAM read/write operation, shift of display as the above function is not performed.

### Entry Mode Set (RE = 1)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | BID |

Set the data shift direction of segment in the application set.

BID: Data Shift Direction of Segment

When BID = "Low", segment data shift direction is set to normal order from SEG1 to SEG100.

When BID = "High", segment data shift direction is set to reversely from SEG100 to SEG1.

By using this instruction, the efficiency of application board area can be raised.

<sup>\*</sup> CGRAM/SEGRAM operates the same as DDRAM, when read from or write to CGRAM/SEGRAM.

<sup>\*</sup> The BID setting instruction is recommended to be set at the same time level of function set instruction.

<sup>\*</sup> DB1 bit must be set to "1".

### Display ON/OFF Control (RE = 0)

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

Control display/cursor/blink ON/OFF 1 bit register.

D: Display ON/OFF control bit

When D = "High", entire display is turned on.

When D = "Low", display is turned off, but display data is remained in DDRAM.

### C: Cursor ON/OFF control bit

When C = "High", cursor is turned on.

When C = "Low", cursor is disappeared in current display, but I/D register remains its data.

### B: Cursor Blink ON/OFF control bit

When B = "High", cursor blink is on, that performs alternate between all the high data and display character at the cursor position. If fosc has frequency of 270kHz, blinking has 370 ms interval.

When B = Low, blink is off.

### Extended Function Set (RE = 1)

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 1   | F/W | B/W | NW  |

### FW: Font Width control

When FW = "High", display character font width is assigned to 6-dot and execution time becomes 6/5 times than that of 5-dot font width. The user font, specified in CGRAM, is displayed into 6-dot font width, bit-5 to bit-0,including the left most space bit of CGRAM.(refer to Figure 15)

When FW = "Low", 5-dot font width is set.

### B/W: Black/White Inversion enable bit

When B/W = "High", black/white inversion at the cursor position is set. In this case C/B bit of display ON/OFF control instruction becomes don't care condition. If fosc has frequency of 270kHz, inversion has 370 ms intervals.

### NW: 4 Line mode enable bit

When NW = "High", 4 line display mode is set. In this case N bit of function set instruction becomes don't care condition.

Figure 15. 6-dot Font Width CGROM/CGRAM

## Cursor or Display Shift (RE = 0)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 1   | S/C | R/L | -   | -   |

Shift right/left cursor position or display without writing or reading of display data. This instruction is used to correct or search display data (refer to Table 7). During 2-line mode display, cursor moves to the 2nd line after 40th digit of 1st line. In 4-line mode, cursor moves to the next line, only after every 20th digit of the current line. Note that display shift is performed simultaneously in all the line enabled by DS1 - DS4 in the Shift Enable instruction. When displayed data is shifted repeatedly, each line shifted individually. When display shift is performed, the contents of address counter are not changed. During low power consumption mode, display shift may not be performed normally.

Table 7. Shift Patterns according to S/C and R/L Bits

| S/C | R/L | Operation                                                                 |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Shift cursor to the left, ADDRESS COUNTER is decreased by 1               |

| 0   | 1   | Shift cursor to the right, ADDRESS COUNTER is increased by 1              |

| 1   | 0   | Shift all the display to the left, cursor moves according to the display  |

| 1   | 1   | Shift all the display to the right, cursor moves according to the display |

### Shift/Scroll Enable (RE = 1)

### DH = 0

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 1   | HS4 | HS3 | HS2 | HS1 |

HS: Horizontal Scroll per Line Enable. This instruction makes valid dot shift by a display line unit.

HS1, HS2, HS3 and HS4 indicate each line to be dot scrolled, and each scroll is performed individually in each line. If you want to scroll the line in 1-line display mode or the 1st line in 2-line display mode, set HS1 and HS2 to "High". If the 2nd line scroll is needed in 2-line mode, set HS3 and HS4 to "High". (refer to Table 8)

DH = 1

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 1   | DS4 | DS3 | DS2 | DS1 |

DS: Display Shift per Line Enable. This instruction selects shifting line to be shifted according to each line mode in display shift right/left instruction. DS1, DS2, DS3 and DS4 indicate each line to be shifted, and each shift is performed individually in each line. If you set DS1 and DS2 to "High" (enable) in 2 line mode, only the 1st line is shifted and the 2nd line is not shifted. When only DS1 = "High", only the half of the 1st line is shifted. If all the DS bits (DS1 to DS4) are set to "Low" (disable), no display is shifted.

Table 8. Relationship between DS and COM signal

| Enable bit | Enabled common signal during shift | Description                                          |

|------------|------------------------------------|------------------------------------------------------|

| HS1/DS1    | COM1 - COM8                        |                                                      |

| HS2/DS2    | COM9 - COM16                       | The part of display line that corresponds to enabled |

| HS3/DS3    | COM17 - COM24                      | common signal can be shifted.                        |

| HS4/DS4    | COM25 - COM32                      |                                                      |

### Function Set (RE = 0)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2   | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-------|-----|-----|

| 0  | 0   | 0   | 0   | 1   | DL  | N   | RE(0) | DH  | REV |

DL: Interface data length control bit

When DL = "High", it means 8-bit bus mode with MPU.

When DL = "Low", it means 4-bit bus mode with MPU. So to speak, DL is a signal to select 8-bit or 4-bit bus mode. In 4-bit bus mode, it needs to transfer 4-bit data by two times.

N : Display line number control bit

It is variable only when NW bit of extended function set instruction is Low.

When N = "Low", 1-line display mode is set.

When N = "High", 2-line display mode is set.

When NW = "High", N bit is invalid, it means 4-line mode independent of N bit.

RE : Extended function registers enable bit

At this instruction, RE must be "Low".

DH: Display shift enable selection bit.

When DH = "High", enables display shift per line.

When DH = "Low", enables smooth dot scroll.

This bit can be accessed only when IE pin input is "High".

REV: Reverse enable bit

When REV = "High", all the display data are reversed. i.e., all the white dots become black and black dots become white. When REV = "Low", the display mode set normal display.

### Function Set (RE = 1)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2   | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-------|-----|-----|

| 0  | 0   | 0   | 0   | 1   | DL  | N   | RE(0) | DH  | REV |

DL: Interface data length control bit

When DL = "High", it means 8-bit bus mode with MPU.

When DL = "Low", it means 4-bit bus mode with MPU. Hence, DL is a signal to select 8-bit or 4-bit bus mode. When 4-bit bus mode, it is required to transfer 4-bit data by two times.

### N: Display line number control bit

It is variable only when NW bit of extended function set instruction is Low.

When N = "Low", 1-line display mode is set.

When N = "High", 2-line display mode is set.

When NW = "High", N bit is invalid, it means 4-line mode independent of N bit.

### RE: Extended function registers enable bit

When RE = "High", extended function set registers, SEGRAM address set registers, BID bit, HS/DS bits of shift/scroll enable instruction and BE bits of function set register can be accessed.

### BE: CGRAM/SEGRAM data blink enable bit

BE = "High", makes user font of CGRAM and segment of SEGRAM blinking. The quantity of blink is assigned the highest 2 bit of CGRAM/SEGRAM.

### LP: Low power consumption mode enable bit

When EXT input is "Low" (without extension driver) and LP bit is set to "High", S6A0073 operates in low power consumption mode.

During 1-line mode S6A0073 operates on a 4-division clock, and in 2-line or 4-line mode it operates on a 2-division clock. According to this instruction, execution time becomes 4 or 2 times longer.

Note not to use display shift instruction, as it may result incorrect operation.

And the frame frequency is lower to 5/6 times lower than that of normal operation.

### Set CGRAM Address (RE = 0)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set CGRAM address to AC.

This instruction makes CGRAM data available from MPU.

### Set SEGRAM Address (RE = 1)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | Х   | Х   | AC3 | AC2 | AC1 | AC0 |

Set SEGRAM address to AC.

This instruction makes SEGRAM data available from MPU.

### Set DDRAM Address (RE = 0)

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set DDRAM address to AC.

This instruction makes DDRAM data available from MPU.

In 1-line display mode (N = 0, NW = 0), DDRAM address is from "00H" to "4FH".

In 2-line display mode (N = 1, NW = 0), DDRAM address in the 1st line is from "00H" to "27H", and DDRAM address in the 2nd line is from "40H" to "67H".

In 4-line display mode (NW = 1), DDRAM address is from "00H" to "13H" in the 1st line, from "20H" to "33H" in the 2nd line, from "40H" to "53H" in the 3rd line and from "60H" to "73H" in the 4th line.

### Set Scroll Quantity (RE = 1)

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | Х   | SQ5 | SQ4 | SQ3 | SQ2 | SQ1 | SQ0 |

As set SQ5 to SQ0, horizontal scroll quantity can be controlled in dot units. (refer to Table 9).

In this case S6A0073 can show hidden areas of DDRAM by executing smooth scroll from 1 to 48 dots.

Table 9. Scroll Quantity According to HDS bits

| SQ5 | SQ4 | SQ3 | SQ2 | SQ1 | SQ0 | Function             |

|-----|-----|-----|-----|-----|-----|----------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | No shift             |

| 0   | 0   | 0   | 0   | 0 1 |     | shift left by 1-dot  |

| 0   | 0   | 0   | 0   | 1   | 0   | shift left by 2-dot  |

| 0   | 0   | 0   | 0   | 1   | 1   | shift left by 3-dot  |

| :   | :   | •   | :   | :   | :   | :                    |

| 1   | 0   | 1   | 1   | 1   | 1   | shift left by 47-dot |

| 1   | 1   | Х   | Х   | Х   | Х   | shift left by 48-dot |

### Read Busy Flag & Address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 1   | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

This instruction shows whether S6A0073 is in internal operation or not. If the resultant BF is High, the internal operation is in progress and should wait until BF to be Low, which by then the next instruction can be performed. In this instruction the value of address can also be read.

#### Write Data to RAM

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1  | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM/CGRAM/SEGRAM.

The selection of RAM from DDRAM, CGRAM, or SEGRAM, is set by the previous address set instruction: DDRAM address set, CGRAM address set, SEGRAM address set.

RAM set instruction can also determines the AC direction to RAM.

After write operation, the address is automatically increased/decreased by 1, according to the entry mode.

#### Read Data from RAM

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM/SEGRAM.

The selection of RAM is set by the previous address set instruction. If address set instruction of RAM is not performed before this instruction, the data that read first is invalid, as the direction of AC is not determined. If RAM data read several times without RAM address set instruction before read operation, the correct RAM data can be obtained from the second, but the first data would be incorrect, as there is no time margin to transfer RAM data. In case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction: it also transfer RAM data to output data register.

After read operation address counter is automatically increased/decreased by 1 according to the entry mode. After CGRAM/SEGRAM read operation, display shift may not be executed correctly.

**NOTE:** In case of RAM write operation, AC is increased/decreased by 1 like read operation after this. In this time, AC indicates the next address position, but the previous data can only be read by instruction.

# INSTRUCTION DESCRIPTION 2 (IE = "LOW")

Table 10. Instruction Set 2

| Instruction                  | RE |    |     |     | Ins | tructi | on Co | ode |     |     |     | Description                                                                                                                                                                                                                                                                                                                               | Execution time             |

|------------------------------|----|----|-----|-----|-----|--------|-------|-----|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                              |    | RS | R/W | DB7 | DB6 | DB5    | DB4   | DB3 | DB2 | DB1 | DB0 |                                                                                                                                                                                                                                                                                                                                           | (f <sub>OSC</sub> =270kHz) |

| Clear Display                | Х  | 0  | 0   | 0   | 0   | 0      | 0     | 0   | 0   | 0   | 1   | Write "20H" to DDRAM. and set DRAM address to "00H" from AC.                                                                                                                                                                                                                                                                              | 1.53ms                     |

| Return Home                  | X  | 0  | 0   | 0   | 0   | 0      | 0     | 0   | 0   | 1   | Х   | Set DDRAM address to "00H" from AC and return cursor to its original position if shifted. The contents of DDRAM are not changed.                                                                                                                                                                                                          | 1.53ms                     |

| Entry Mode<br>Set            | X  | 0  | 0   | 0   | 0   | 0      | 0     | 0   | 1   | I/D | Ø   | Assign cursor moving direction.  I/D = "1" : increment,  I/D = "0" : decrement.  and display shift enable bit.  S = "1" :make entire display shift of all lines during DDRAM write,  S = "0":display shift disable                                                                                                                        | 39μs                       |

| Display<br>ON/OFF<br>Control | 0  | 0  | 0   | 0   | 0   | 0      | 0     | 1   | D   | С   | В   | Set display/cursor/blink on/off D = "1" : display on, D = "0" : display off, C = "1" : cursor on, C = "0" : cursor off, B = "1" : blink on, B = "0" : blink off.                                                                                                                                                                          | 39μs                       |

| Extended function set        | 1  | 0  | 0   | 0   | 0   | 0      | 0     | 1   | FW  | BW  | SW  | Assign font width, black/white inverting of cursor, and 4-line display mode control bit.  FW = "1" : 6-dot font width,  FW = "0" : 5-dot font width,  B/W = "1" : black/white inverting of cursor enable,  B/W = "0" : black/white inverting of cursor disable  NW = "1" : 4-line display mode,  NW = "0" : 1-line or 2-line display mode | 39µs                       |

| Cursor or<br>Display Shift   | 0  | 0  | 0   | 0   | 0   | 0      | 1     | S/C | R/L | Х   | Х   | Cursor or display shift. S/C = "1" : display shift, S/C = "0" : cursor shift, R/L = "1" : shift to right, R/L = "0" : shift to left                                                                                                                                                                                                       | 39µs                       |

Table 10. Instruction Set 2 (continued)

| Instruction                      | RE |    |     |     | Ins | tructi | on Co | ode |           |     |     | Description                                                                                                                                                                                                                                              | Execution time             |

|----------------------------------|----|----|-----|-----|-----|--------|-------|-----|-----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                  |    | RS | R/W | DB7 | DB6 | DB5    | DB4   | DB3 | DB2       | DB1 | DB0 |                                                                                                                                                                                                                                                          | (f <sub>OSC</sub> =270kHz) |

| Scroll Enable                    | 1  | 0  | 0   | 0   | 0   | 0      | 1     | HS4 | HS3       | HS2 | HS1 | Determine the line for horizontal smooth scroll.  HS1 = "1/0":  1st line dot scroll enable/disable  HS2 = "1/0":  2nd line dot scroll enable/disable  HS3 = "1/0":  3rd line dot scroll enable/disable  HS4 = "1/0":  4th line dot scroll enable/disable | 39µs                       |

| Function Set                     | 0  | 0  | 0   | 0   | 0   | 1      | DL    | Z   | RE<br>(0) | X   |     | Set interface data length  DL = "1" : 8-bit,  DL = "0" : 4-bit  numbers of display line when NW = "0",  N = "1" : 2-line,  N = "0" : 1-line  extension register, RE("0"),                                                                                | 39µs                       |

|                                  | 1  | 0  | 0   | 0   | 0   | 1      | DL    | Z   | RE<br>(1) | BE  |     | Set DL, N, RE("1") and CGRAM/SEGRAM blink enable (BE) BE = " 1/0" : CGRAM/SEGRAM blink enable/disable LP = "1" : low power mode LP = "0" : normal operation mode                                                                                         | 39µs                       |

| Set CGRAM<br>Address             | 0  | 0  | 0   | 0   | 1   | AC5    | AC4   | AC3 | AC2       | AC1 | AC0 | Set CGRAM address in address counter.                                                                                                                                                                                                                    | 39µs                       |

| Set SEGRAM<br>Address            | 1  | 0  | 0   | 0   | 1   | Х      | Х     | AC3 | AC2       | AC1 | AC0 | Set SEGRAM address in address counter.                                                                                                                                                                                                                   | 39µs                       |

| Set DDRAM<br>Address             | 0  | 0  | 0   | 1   | AC6 | AC5    | AC4   | AC3 | AC2       | AC1 | AC0 | Set DDRAM address in address counter.                                                                                                                                                                                                                    | 39µs                       |

| Set Scroll<br>Quantity           | 1  | 0  | 0   | 1   | Х   | SQ5    | SQ4   | SQ3 | SQ2       | SQ1 | SQ1 | Set the quantity of horizontal dot scroll.                                                                                                                                                                                                               | 39µs                       |

| Read Busy<br>flag and<br>Address | Х  | 0  | 1   | BF  | AC6 | AC5    | AC4   | AC3 | AC2       | AC1 |     | Can be known whether during internal operation or not by reading BF. The contents of address counter can also be read. BF = "1": busy state, BF = "0": ready state.                                                                                      | 0μs                        |

| Write Data                       | Х  | 1  | 0   | D7  | D6  | D5     | D4    | D3  | D2        | D1  | D0  | Write data into internal RAM<br>(DDRAM/CGRAM/SEGRAM).                                                                                                                                                                                                    | 43µs                       |

| Read Data                        | Х  | 1  | 1   | D7  | D6  | D5     | D4    | D3  | D2        | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM/SEGRAM).                                                                                                                                                                                                        | 43µs                       |

**NOTE:** When an MPU program with Busy Flag (DB7) checking is made, 1/2 f<sub>OSC</sub> (is necessary) for executing the next instruction by the falling edge of the 'E' signal after the Busy Flag (DB7) goes to "low".

### **Display Clear**

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set DDRAM address to "00H" into AC (address counter). Return cursor to the original status, namely, bring the cursor to the left edge on first line of the display. And entry mode is set to increment mode (I/D = "1").

#### **Return Home**

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Х   |

Return Home is cursor return home instruction. Set DDRAM address to "00H" into the address counter. Return cursor to its original site and return display to its original status, if shifted. Contents of DDRAM does not change.

### **Entry Mode Set**

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

Set the moving direction of cursor and display.

I/D : Increment/decrement of DDRAM address (cursor or blink)

When I/D = "High", cursor/blink moves to right and DDRAM address is increased by 1.

When I/D = "Low", cursor/blink moves to left and DDRAM address is decreased by 1.

When S = "High", after DDRAM write, the entire display of all lines is shifted to the right (I/D = "low") or to the left (I/D = "high"). But it will seem as if the cursor is not moving. When S = "Low", or DDRAM read, or CGRAM/SEGRAM read/write operation, shift of entire display is not performed.

<sup>\*</sup> CGRAM/SEGRAM operates the same as DDRAM, when read from or write to CGRAM/SEGRAM.