URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

**Preliminary**

PT6880

# **Description**

PT6880 is an OLED Driver/Controller IC utilizing CMOS Technology specially designed to display alphanumeric and Japanese kana characters as well as symbols and graphics. It can interface with either 4-bit or 8-bit Microprocessor and display up to one 8-character line or two 8-character lines.

Display RAM, Character Generator, OLED Driver as well as a wide range of instruction functions such as Display Clear, Cursor Home, Display ON/OFF, Cursor ON/OFF, Display Character Blink, Cursor Shift, Display Shift are all incorporated into a single chip having the highest performance and reliability. Pin assignments and application circuit are optimized for easy PCB layout and cost saving advantages.

### **Features**

- CMOS Technology

- Low Power Consumption

- 4-Bit or 8-Bit MPU Interface

- High Speed MPU Interface: 2MHz (VDD =5V)

- 80 x 8-Bit Display RAM (80 characters max.)

- Auto Reset Function

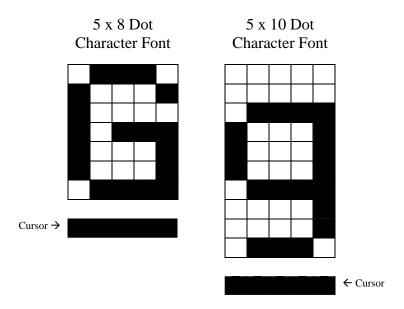

- 5 x 8 and 5 x 10 Dot Matrix

- Built-in Oscillator with External Resistors

- Programmable Duty Cycle:

- 1/8 Duty: (1 Display Line, 5 x 8 Dots with Cursor)

- 1/11 Duty: (1 Display Line, 5 x 10 Dots with Cursor)

- 1/16 Duty: (2 Display Lines, 5 x 8 Dots with Cursor)

- 9920-Bit Character Generator ROM (CGROM)

- 208 Character Fonts (5 x 8 dot matrix)

- 32 Character Fonts (5 x 10 dot matrix)

- 64 x 8-Bit Character Generator RAM (CGRAM)

- 8 Character Fonts (5 x 8 dot matrix)

- 4 Character Fonts (5 x 10 dot matrix)

- 16 Common x 40 Segment OLED Drivers

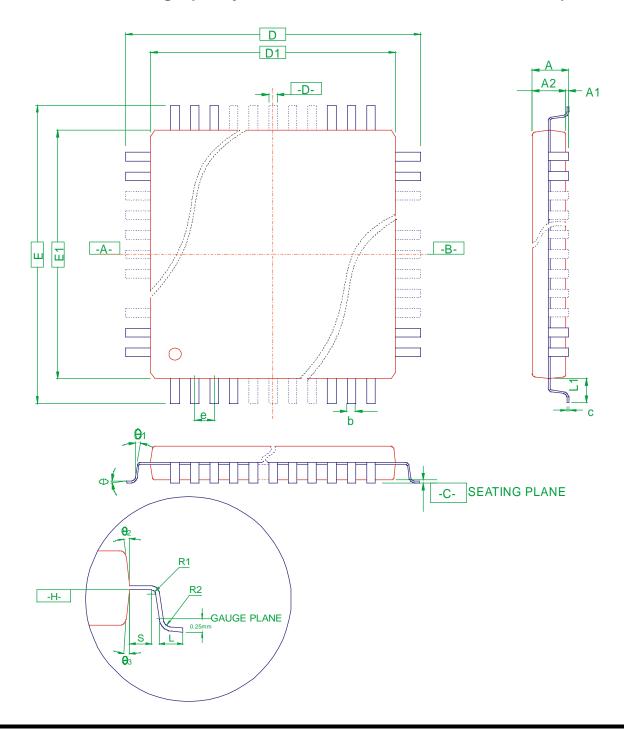

- Available in C.O.B. or QFP Package

URL: http://www.princeton.com.tw

# OLED Driver/Controller IC

**Preliminary**

PT6880

# **Applications**

- Cellular Phone

- Data Bank/Organizer

- Electronic Dictionary / Translator

- Information Appliance

- P.D.A.

- P.O.S.

- Car Audio

- Electronic Equipment with OLED Display

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

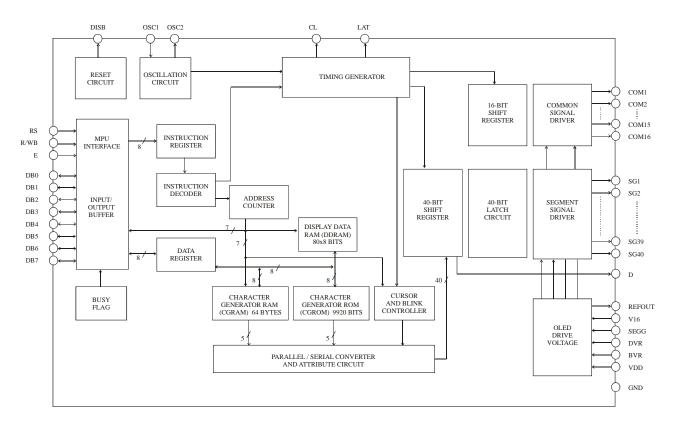

# **Block Diagram**

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

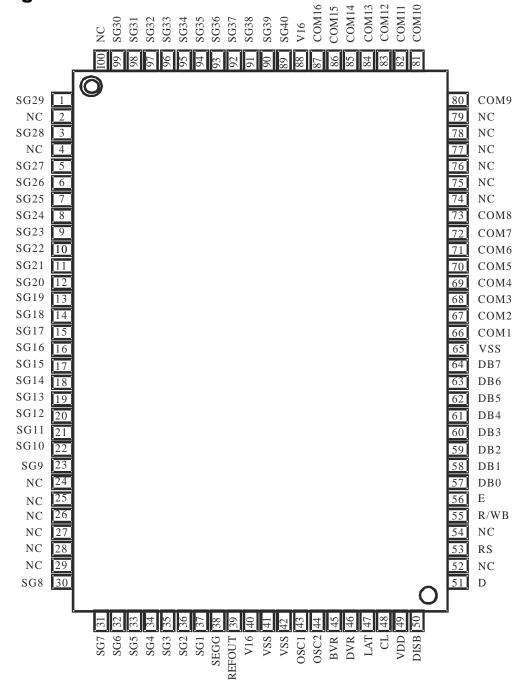

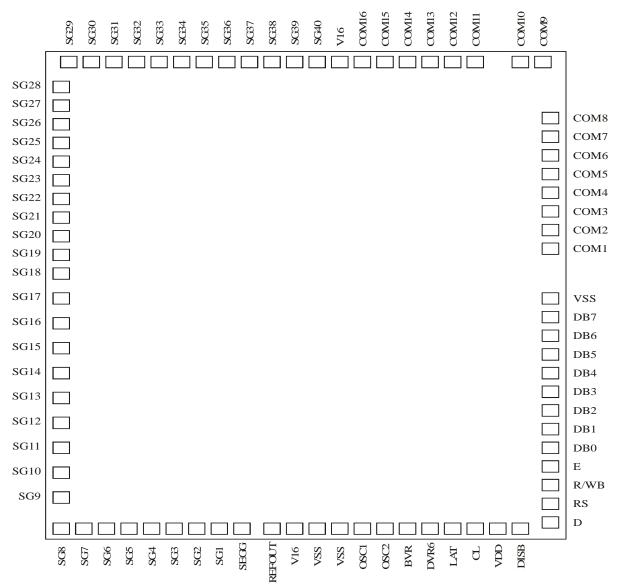

# **Pin Configuration**

# **Pin/Pad Description**

URL: http://www.princeton.com.tw

# OLED Driver/Controller IC

# **Preliminary**

PT6880

| Pin Name    | I/O                                              | Description                                         | Pad/Pin No. |  |  |  |  |  |  |

|-------------|--------------------------------------------------|-----------------------------------------------------|-------------|--|--|--|--|--|--|

| SG40 ~ SG30 |                                                  |                                                     | 89 ~ 99     |  |  |  |  |  |  |

| SG29, SG 28 |                                                  | So amont Driver Output Ding                         | 1,3         |  |  |  |  |  |  |

| SG27 ~ SG9  | О                                                | Segment Driver Output Pins                          | 5 ~ 23      |  |  |  |  |  |  |

| SG8 ~ SG1   |                                                  |                                                     | 30 ~ 37     |  |  |  |  |  |  |

| SEGG        | -                                                | OLED Drive Power Supply (0V)                        | 38          |  |  |  |  |  |  |

| REFOUT      | O                                                | Reference Current Output Pin                        | 39          |  |  |  |  |  |  |

| V16         | -                                                | 40, 88                                              |             |  |  |  |  |  |  |

| VSS         | -                                                | Ground Pin (0V)                                     | 41, 42, 65  |  |  |  |  |  |  |

| OSC1        | I                                                | Oscillator Input Pin                                | 43          |  |  |  |  |  |  |

| OSC2        | О                                                | Oscillator Output Pin                               | 44          |  |  |  |  |  |  |

| BVR         | I                                                | Brightness Control Input Pin                        | 45          |  |  |  |  |  |  |

| DVR         | I                                                | Precharge Time Control Input Pin                    | 46          |  |  |  |  |  |  |

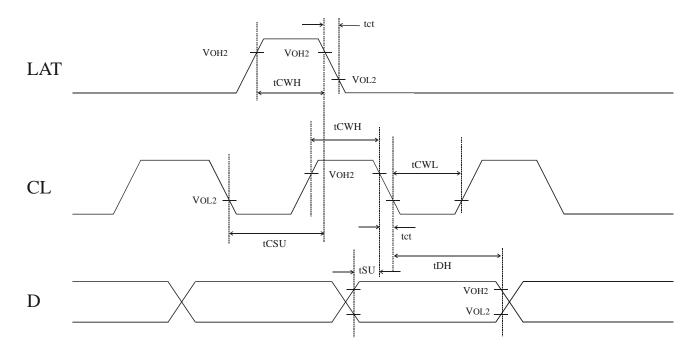

| LAT         | О                                                | Latch Clock Output Pin                              | 47          |  |  |  |  |  |  |

| CL          | О                                                | Shift Clock Output Pin                              | 48          |  |  |  |  |  |  |

| VDD         | -                                                | Power Supply (2.7V to 5.5V)                         | 49          |  |  |  |  |  |  |

| DISB        | 0                                                | Reset Signal Output Pin                             | 50          |  |  |  |  |  |  |

| D           | О                                                | Character Pattern Data Output Pin                   | 51          |  |  |  |  |  |  |

|             |                                                  | Register Select Input Pin                           |             |  |  |  |  |  |  |

|             |                                                  | When this pin is set to "0", it is used as an       |             |  |  |  |  |  |  |

| RS          | I                                                | Instruction Register.                               | 53          |  |  |  |  |  |  |

|             |                                                  | When this pin is set to "1", it is used for as the  |             |  |  |  |  |  |  |

|             |                                                  | Data Register.                                      |             |  |  |  |  |  |  |

|             |                                                  | Read/Write Control Input Pin                        |             |  |  |  |  |  |  |

|             |                                                  | This pin is used to select either the Write or the  |             |  |  |  |  |  |  |

| R/WB        | I                                                | Read Operation. If this pin is set to "0", then the | 55          |  |  |  |  |  |  |

|             | Write Function is enabled. If this pin is set to |                                                     |             |  |  |  |  |  |  |

|             | "1", then the Read function is enabled.          |                                                     |             |  |  |  |  |  |  |

| Е           | I                                                | Data Read/Write Start Control Pin                   | 56          |  |  |  |  |  |  |

|             |                                                  | Low Order Bidirectional Data I/O Pins               |             |  |  |  |  |  |  |

| DB0 ~ DB3   | I/O                                              | These pins are used for data transfer and           | 57 ~ 60     |  |  |  |  |  |  |

|             |                                                  | reception between the MPU and PT6880. These         |             |  |  |  |  |  |  |

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

|                             |      | pins are not used during a 4-bit operation.                                                                                                           |                                        |

|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| DB4~DB7                     | I/O) | High Order Bidirectional Data I/O Pins These pins are used for data transfer and reception between the MPU and PT6880. D7 can be used as a Busy Flag. | 61 ~ 64                                |

| COM1 ~ COM8<br>COM9 ~ COM16 | О    | Common Driver Output Pins (see Note 1)                                                                                                                | 66 ~ 73<br>80 ~ 87                     |

| NC                          | -    | No Connection                                                                                                                                         | 2, 4, 24 ~ 29, 52,<br>54, 74 ~ 79, 100 |

Note: 1. COM1 to COM16 are used as the Common Output Driver Pins. However, when the pins are not in used, the respective common signals are transformed into non-selection waveforms. For example, under a 1/8 Duty Factors, the Common Driver Output Pins -- COM16 are not used. Common Driver Output Pins -- COM12 to COM16 are not used during a 1/11 duty factor. Therefore, the common signals represented by aforementioned Unused Common Driver Output Pins are transformed into non-selection waveforms.

URL: http://www.princeton.com.tw

OLED Driver/Controller IC

**Preliminary**

PT6880

# **Functional Description**

### Registers

PT6880 provides two types of 8-bit registers, namely: Instruction Register (IR) and Data Register (DR). The register is selected using the RS Pin. When the RS pin is set to "0", the Instruction Register Type is selected. When RS pin is set to "1", the Data Register Type is selected. Please refer to the table below.

| RS | R/WB | Operation                                                           |

|----|------|---------------------------------------------------------------------|

| 0  | 0    | Instruction Register Write as an Internal Operation.                |

| 0  | 1    | Read Busy Flag (DB7) and Address Counter (DB0 to DB6)               |

| 1  | 0    | Data Register Write as an Internal Operation (DR to DDRAM or CGRAM) |

| 1  | 1    | Data Register Read as an Internal Operation (DDRAM or CGRAM to DR)  |

#### **INSTRUCTION REGISTER (IR)**

The Instruction Register is used to store the instruction code (i.e. Display Clear, Cursor Home and others), Display Data RAM (DDRAM) Address, and the Character Generator RAM (CGRAM) Address. Instruction register can only be written from the MPU.

#### **DATA REGISTER (DR)**

The Data Register is used as a temporary storage for data that are going to be written into the DDRAM or CGRAM as well as those data that are going to be read from the DDRAM or CGRAM.

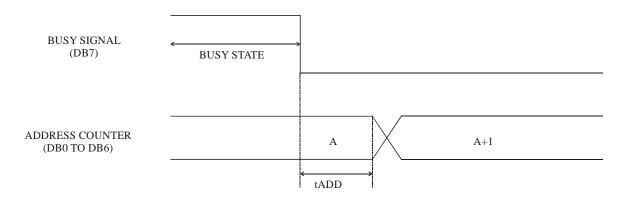

# BUSY FLAG (BF)

The Busy Flag is used to determine whether PT6880 is idle or internally operating. When PT6880 is performing some internal operations, the Busy Flag is set to "1". Under this condition, the no other instruction will not be accepted. When RS Pin is set to "0" and R/WB Pin is set to "1", the Busy Flag will be outputted to the DB7 pin.

When PT6880 is idle or has completed its previous internal operation, the Busy Flag is set to "0". The next instruction can now be processed or executed.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

**Preliminary**

PT6880

### ADDRESS COUNTER (AC)

The address counter is used to assign the Display Data RAM (DDRAM) Address and the Character Generator RAM (CGRAM) Address. When an Address information is written into the Instruction Register (IR), this Address information is sent from the Instruction Register to the Address Counter. At the same time, the nature of the Address (either CGRAM or DDRAM) is determined by the instruction. After writing into or reading from the DDRAM or CGRAM, the Address Counter is automatically increased or decreased by 1 (for Write or Read Function). It must be noted that when the RS pin is set to "0" and R/WB is set to "1", the contents of the Address Counter are outputted to the pins -- DB0 to DB6.

### DISPLAY DATA RAM (DDRAM)

The Display Data RAM (DDRAM) is used to store the Display Data which is represented as 8-bit character code. The Display Data RAM supports an extended capacity of 80 x 8-bits or 80 characters. The area in the DDRAM which are not used for display can be used as General Data RAM. For more details, please refer to the sections below.

The Display Data RAM Address (ADD) is set in the Address Counter as a hexadecimal.

|                                    | High | n Order | Bits | Low Order Bits |     |     |     |  |  |  |  |

|------------------------------------|------|---------|------|----------------|-----|-----|-----|--|--|--|--|

| Address<br>Counter<br>(hexadecimal | AC6  | AC5     | AC4  | AC3            | AC2 | AC1 | AC0 |  |  |  |  |

An example of a DDRAM Address = 4E is given below.

|     | DDRAM Address: 4E |     |     |     |     |     |  |  |  |  |  |  |  |  |

|-----|-------------------|-----|-----|-----|-----|-----|--|--|--|--|--|--|--|--|

| AC6 | AC5               | AC4 | AC3 | AC2 | AC1 | AC0 |  |  |  |  |  |  |  |  |

| 1   | 1 0 0 1 1 0       |     |     |     |     |     |  |  |  |  |  |  |  |  |

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

#### 1-LINE DISPLAY (N=0)

When the number of characters displayed is less than 80, the first character is displayed at the head position. The relationship between the DDRAM Address and position on the OLED Panel is shown below.

| Display Position (digit) | 1  | 2  | 3  | 4  | <br>78 | 79 | 80 |

|--------------------------|----|----|----|----|--------|----|----|

| DDRAM Address            | 00 | 01 | 02 | 03 | 4D     | 4E | 4F |

| (hexadecimal)            | 00 | 01 | 02 | 03 | <br>עד | TL | 71 |

For example, when only 8 characters are displayed in one Display Line, the relationship between the DDRAM Address and position on the OLED Panel is shown below.

| Display Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|------------------|----|----|----|----|----|----|----|----|

| DDRAM Address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

|                  |    |    |    |    |    |    |    |    |

| Shift Left       | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 |

|                  |    |    |    |    |    |    |    |    |

| Shift Right      | 4F | 00 | 01 | 02 | 03 | 04 | 05 | 06 |

#### 2-LINE DISPLAY (N=1)

Case 1: The Number of Characters displayed is less than 40 x 2 lines

When the number of characters displayed is less than 40 x 2 lines, then the first character of the first and second lines are displayed starting from the head. It is important to note that the first line end address and the second line start address are not consecutive. Please refer the figure below.

| Display Position | 1  | 2  | 3  | 4  | <br>37 | 38 | 39 | 40 |

|------------------|----|----|----|----|--------|----|----|----|

| DDRAM Address    | 00 | 01 | 02 | 03 | <br>24 | 25 | 26 | 27 |

| (hexadecimal)    | 40 | 41 | 42 | 43 | <br>64 | 65 | 66 | 67 |

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

To illustrate, for 2-line x 8 characters display, the relationship between the DDRAM address and position of the OLED panel is shown below.

| Display Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|------------------|----|----|----|----|----|----|----|----|

| DDRAM Address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

| DDKAW Address    | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

|                  |    |    |    |    |    |    |    |    |

| Shift Left       | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 |

| Sillit Lett      | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 |

|                  |    |    |    |    |    |    |    |    |

| Chift Dight      | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 |

| Shift Right      | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 |

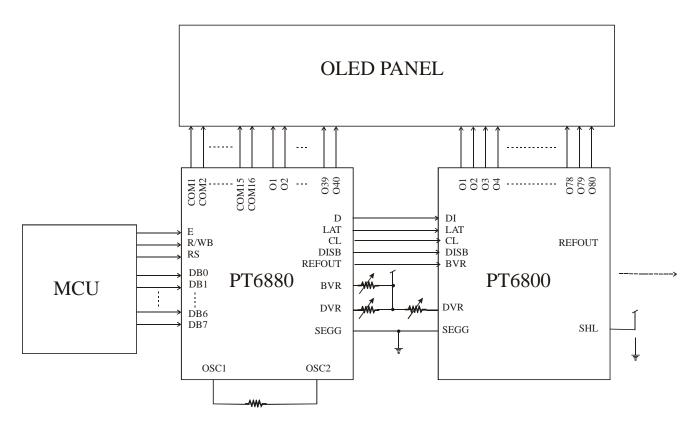

#### Case 2: 16-Character x 2 Lines Display

PT6880 can be extended to display 16 characters x 2 lines by using the 40-output extension driver. When there is a Display Shift operation, the DDRAM Address is also shifted. Please refer to the example below.

| <b>Display Position</b> | 1  | 2  | 3  | 4    | 5    | 6   | 7  | 8  | 9  | 10 | 11     | 12   | 13      | 14     | 15 | 16      |

|-------------------------|----|----|----|------|------|-----|----|----|----|----|--------|------|---------|--------|----|---------|

| DDRAM                   | 00 | 01 | 02 | 03   | 04   | 05  | 06 | 07 | 08 | 09 | 0A     | 0B   | 0C      | 0D     | 0E | 0F      |

| Address                 | 40 | 41 | 42 | 43   | 44   | 45  | 46 | 47 | 48 | 49 | 4A     | 4B   | 4C      | 4D     | 4E | 4F      |

| Address                 |    |    | PT | 6880 | Disp | lay |    |    |    | E  | xtensi | on D | river l | Displa | ay |         |

|                         |    |    |    |      |      |     |    |    |    |    |        |      |         |        |    |         |

| Shift Left              | 01 | 02 | 03 | 04   | 05   | 06  | 07 | 08 | 09 | 0A | 0B     | 0C   | 0D      | 0E     | 0F | 10      |

| Shift Left              | 41 | 42 | 43 | 44   | 45   | 46  | 47 | 48 | 49 | 4A | 4B     | 4C   | 4D      | 4E     | 4F | 50      |

|                         |    |    |    |      |      |     |    |    |    |    |        |      |         |        |    | <u></u> |

| Shift Dight             | 27 | 00 | 01 | 02   | 03   | 04  | 05 | 06 | 07 | 08 | 09     | 0A   | 0B      | 0C     | 0D | 0E      |

| Shift Right             | 67 | 40 | 41 | 42   | 43   | 44  | 45 | 46 | 47 | 48 | 49     | 4A   | 4B      | 4C     | 4D | 4E      |

URL: http://www.princeton.com.tw

OLED Driver/Controller IC

**Preliminary**

PT6880

### Character Generator ROM (CGROM)

The Character Generator ROM (CGROM) is used to generate either  $5 \times 8$  dots or  $5 \times 10$  dots character patterns from 8-bit character codes. It can generate up to two hundred eight (208)  $5 \times 8$  dot character patterns and thirty two (32)  $5 \times 10$  dot character patterns. For user-defined character patterns, please contact PTC.

# CORRESPONDENCE BETWEEN THE CHARACTER CODES AND THE CHARACTER PATTERNS

| PAL                         |                | 110 |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

|-----------------------------|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------------------------|-----|-----|

| UPPER<br>BITS<br>LOWER BITS | 0000           | 000 | 001 | 001 | 010 | 010 | 011 | 011 | 100 | 100 | 101 | 101 | 110 | 110                                          | 111 | 111 |

| 0000                        | CG<br>RAM<br>1 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0001                        | CG<br>RAM      |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0010                        | CG<br>RAM      |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0011                        | CG<br>RAM      |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0100                        | CG<br>RAM<br>E |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0101                        | CG<br>RAM      |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0110                        | CG<br>RAM<br>7 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 0111                        | CG<br>RAM<br>8 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1000                        | CG<br>RAM<br>1 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1001                        | CG<br>RAM<br>2 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1010                        | CG<br>RAM<br>3 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1011                        | CG<br>RAM<br>4 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1100                        | CG<br>RAM<br>5 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1101                        | CG<br>RAM<br>6 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1110                        | CG<br>RAM<br>7 |     |     |     |     |     |     |     |     |     |     |     |     |                                              |     |     |

| 1111                        | CG<br>RAM<br>8 |     |     |     |     |     |     |     |     |     |     |     |     | 34 35 35<br>34 35<br>34 35<br>34 35<br>34 35 |     |     |

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

**Preliminary**

PT6880

### CHARACTER Generator RAM (CGRAM)

The Character Generator RAM (CGRAM) is used to generate either 5 x 8 dot or 5 x 10 dot character patterns. It can generate eight 5 x 8 dot character patterns and four 5 x 10 dot character patterns. The character patterns generated by the CGRAM can be rewritten. User-defined character patterns for the CGRAM is supported. Areas in the CGRAM that are not used for display may be used as the General Data RAM.

# RELATIONSHIP BETWEEN CGRAM ADDRESS, DDRAM CHARACTER CODE AND CGRAM CHARACTER PATTERNS (FOR 5 X 8 DOT CHARACTER PATTERN)

|              | Char      | acter     | Codes     | s (DD     | RAM | Data | )   |     | CGRAM Address |           |    |           |                                        |     |           | (         | Chara       | cter P                                 | attern   | s (CG | RAM | Data | .)  |                     |

|--------------|-----------|-----------|-----------|-----------|-----|------|-----|-----|---------------|-----------|----|-----------|----------------------------------------|-----|-----------|-----------|-------------|----------------------------------------|----------|-------|-----|------|-----|---------------------|

| 7            | 6         | 5         | 4         | 3         | 2   | 1    | 0   |     | 5             | 4         | 3  | 2         | 1                                      | 0   |           | 7         | 6           | 5                                      | 4        | 3     | 2   | 1    | 0   |                     |

| Hi           | gh        |           |           |           |     | ]    | Low |     | Hig           | h         |    |           |                                        |     |           | Hig       | h           |                                        |          |       |     | Lov  | V   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 0                                      | 0   |           | *         | *           | *                                      | 1        | 1     | 1   | 1    | 0   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 0                                      | 1   |           | *         | *           | *                                      | 1        | 0     | 0   | 0    | 1   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 1                                      | 0   |           | *         | *           | *                                      | 1        | 0     | 0   | 0    | 1   |                     |

|              | 0         |           |           | *         |     |      |     |     |               |           |    | 0         | 1                                      | 1   |           | *         | *           | *                                      | 1        | 1     | 1   | 1    | 0   | Character Pattern 1 |

| 0            | 0         | 0         | 0         | ~         | 0   | 0    | 0   |     | 0             | 0         | 0  | 1         | 0                                      | 0   |           | *         | *           | *                                      | 1        | 0     | 1   | 0    | 0   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 1         | 0                                      | 1   |           | *         | *           | *                                      | 1        | 0     | 0   | 1    | 0   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 1         | 1                                      | 0   |           | *         | *           | *                                      | 1        | 0     | 0   | 0    | 1   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 1         | 1                                      | 1   |           | *         | *           | *                                      | 0        | 0     | 0   | 0    | 0   | Cursor Position     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 0                                      | 0   |           | *         | *           | *                                      | 1        | 0     | 0   | 0    | 1   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 0                                      | 1   |           | *         | *           | *                                      | 0        | 1     | 0   | 1    | 0   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 1                                      | 0   |           | *         | *           | *                                      | 1        | 1     | 1   | 1    | 1   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 1                                      | 1   |           | *         | *           | *                                      | 0        | 0     | 1   | 0    | 0   | Character Pattern 2 |

| 0            | 0         | 0         | 0         | *         | 0   | 0    | 1   |     | 0             | 0         | 1  | 1         | 0                                      | 0   |           | *         | *           | *                                      | 1        | 1     | 1   | 1    | Ť   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 1         | _                                      | Ť   |           | *         | *           | *                                      | 0        | 1     | 1   | 1    | 1   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | <u> </u>  | 0                                      | 0   |           | *         | *           | *                                      | 0        | 0     | 1   | 0    | 0   |                     |

|              |           |           |           |           |     |      |     |     |               |           |    |           | 1                                      | 1   |           | *         | *           | *                                      | 0        | 0     | 0   | 0    | 0   | Cursor Position     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 0                                      | 0   |           | *         | *           | *                                      | U        | U     | U   | U    | U   | Cursor Position     |

|              |           |           |           |           |     |      |     |     |               |           |    | 0         | 0                                      | 1   |           | *         | *           | *                                      |          |       |     |      |     |                     |

| $\sim$       |           |           |           |           |     |      |     | ·// | ·//           |           |    | ·//       | ww                                     | ~~~ | · · · · · | · · · · · | · · · · · · | ~~\                                    | \\\\     |       |     |      | ~~~ |                     |

| $\sim\sim$ 1 | · · · · · | · · · · · | · · · · · | · · · · · | ~~~ | ~~   | ~~~ | ~~~ | · · · · ·     | · · · · · | ~~ | <u>~~</u> | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |     | · · · · · | *         | *           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | <u> </u> |       |     |      | ~~~ |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 1 1       | 0                                      | 0   |           | *         | *           | *                                      |          |       |     |      |     |                     |

| 0            | 0         | 0         | 0         | *         | 1   | 1    | 1   |     | 1             | 1         | 1  | 1         | 1                                      | 0   |           | *         | *           | *                                      |          |       |     |      |     |                     |

|              |           |           |           |           |     |      |     |     |               |           |    | 1         | 1                                      | 1   |           | *         | *           | *                                      |          |       |     |      |     |                     |

Notes:

- 1. \* = Not Relevant

- 2. The character pattern row positions correspond to the CGRAM data bits -- 0 to 4, where bit 4 is in the left position.

- 3. Character Code Bits 0 to 2 correspond to the CGRAM Address Bits 3 to 5 (3 bits : 8 types)

- 4. If the CGRAM Data is set to "1", then the selection is displayed. If the CGRAM is set to "0", there no selection is made.

- 5. The CGRAM Address Bits 0 to 2 are used to define the character pattern line position. The 8th line is the cursor position and its display is formed by the logical OR with the cursor. The 8th line CGRAM data bits 0 to 4 must be set to "0". If any of the 8th line CGRAM data

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

- bits 0 to 4 is set to "1", the corresponding display location will light up regardless of the cursor position.

- 6. When the Character Code Bits 4 to 7 are set to "0", then the CGRAM Character Pattern is selected. It must be noted that Character Code Bit 3 is not relevant and will not have any effect on the character display. Because of this, the first Character Pattern shown above (R) can be displayed when the Character Code is 00H or 08H.

# RELATIONSHIP BETWEEN CGRAM ADDRESS, DDRAM CHARACTER CODE AND CGRAM CHARACTER PATTERNS (FOR 5 X10 DOT CHARACTER PATTERN)

|            | Chai | racter | Code   | s (DD | RAM | Data       | )            |   |             | (     | GRA | M Ad | dress |          | (         | Chara | cter P | attern | s (CG | RAM | I Data | ı) |                   |

|------------|------|--------|--------|-------|-----|------------|--------------|---|-------------|-------|-----|------|-------|----------|-----------|-------|--------|--------|-------|-----|--------|----|-------------------|

| 7          | 6    | 5      | 4      | 3     | 2   | 1          | 0            |   | 5           | 4     | 3   | 2    | 1     | 0        | 7         | 6     | 5      | 4      | 3     | 2   | 1      | 0  |                   |

| Hi         | gh   |        |        |       |     |            | Low          |   | Hig         | h     |     |      |       | Low      | Hig       | h     |        |        |       |     | Lov    | W  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 0    | 0     | 0        | *         | *     | *      | 0      | 0     | 0   | 0      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 0    | 0     | 1        | *         | *     | *      | 0      | 0     | 0   | 0      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 0    | 1     | 0        | *         | *     | *      | 1      | 0     | 1   | 1      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 0    | 1     | 1        | *         | *     | *      | 1      | 1     | 0   | 0      | 1  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 1    | 0     | 0        | *         | *     | *      | 1      | 0     | 0   | 0      | 1  | Character Pattern |

| 0          | 0    | 0      | 0      | *     | 0   | 0          | *            |   | 0           | 0     | 0   | 1    | 0     | 1        | *         | *     | *      | 1      | 0     | 0   | 0      | 1  | Character Pattern |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 1    | 1     | 0        | *         | *     | *      | 1      | 1     | 1   | 1      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 1    | 1     | 1        | *         | *     | *      | 1      | 0     | 0   | 0      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 0    | 0     | 0        | *         | *     | *      | 1      | 0     | 0   | 0      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 0    | 0     | 1        | *         | *     | *      | 1      | 0     | 0   | 0      | 0  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 0    | 1     | 0        | *         | *     | *      | 0      | 0     | 0   | 0      | 0  | Cursor Position   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 0    | 1     | 1        | <br>*     | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 0     | 0        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 0     | 1        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 1     | 0        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 1     | 1        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 0   | 0    | 0     | 0        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

| ~~         | ·~   | $\sim$ | $\sim$ | -     | -   | ·~         | · · · · ·    | M | ·           | · · · | 0   | 0    | 0     | $\sim 1$ | *         | *     | *      | *      | *     | *   | *      | *  |                   |

| ~~         |      |        |        |       |     |            |              |   |             |       |     |      |       |          |           |       |        |        |       |     |        |    |                   |

| 0          | 0    | 0      | 0      | *     | 1   | 1          | *            |   | 1           | 1     | 1   | 0    | 0     | 1        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

| . <u> </u> |      | ļ      |        | ļ     | ļ   | ļ <u>.</u> | ļ. <b></b> . | Ļ | ļ. <u> </u> | ļ     | _1  | 0_   | 11_   | 0_       | <br>*<br> | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 0    | 1     | 1        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 0     | 0        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 0     | 0        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   |             |       | 1   | 1    | 1     | 1        | *         | *     | *      | *      | *     | *   | *      | *  |                   |

|            |      |        |        |       |     |            |              |   | <u> </u>    |       | 1   | 1    | 1     | 1        | • "       |       | 7.     | -1"    | 7,    | 7,  | 7,7    |    | J                 |

Notes: 1. \*

- 1. \* = Not Relevant

- 2. The character pattern row positions correspond to the CGRAM data bits -- 0 to 4, where bit 4 is in the left position.

- 3. Character Code Bits 1 and 2 correspond to the CGRAM Address Bits -- 4 and 5 respectively (2 bits : 4 types)

- 4. If the CGRAM Data is set to "1", then the selection is displayed. If the CGRAM is set to "0", there no selection is made.

- 5. The CGRAM Address Bits 0 to 3 are used to define the character pattern line position. The 11th line is the cursor position and its display is formed by the logical OR with the cursor.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

The 11th line CGRAM data bits 0 to 4 must be set to "0". If any of the 11th line CGRAM data bits 0 to 4 is set to "1", the corresponding display location will light up regardless of the cursor position.

6. When the Character Code Bits 4 to 7 are set to "0", then the CGRAM Character Pattern is selected. It must be noted that Character Code Bit -- 0 and 3 are not relevant and will not have any effect on the character display. Because of this, the Character Pattern shown above (P) can be displayed when the Character Code is 00H, 01H, 08H or 09H.

### **Timing Generation Circuit**

The timing signals for the internal circuit operations (i.e. DDRAM, CGRAM, and CGROM) are generated by the Timing Generation Circuit. The timing signals for the MPU internal operation and the RAM Read for Display are generated separately in order to prevent one from interfering with the other. This means that, for example, when the data is being written into the DDRAM, there will be no unwanted interference such as flickering in areas other than the display area.

#### **OLED Driver Circuit**

PT6880 provides 16 Common Drivers and 40 Segment Driver Outputs. When a character font and the number of lines to be displayed have been selected, the corresponding Common Drivers output the drive waveform automatically. A non-selection waveform will be outputted by the rest of the Common Drivers.

Serial data transmission always begins with the display data character pattern corresponding to the last Display Data RAM (DDRAM) Address. The serial data is latched when the display data character pattern corresponding to the starting address enters the internal shift register. Thus, PT6880 drives from the head display.

#### Cursor / Blink Control Circuit

The cursor or character blinking is generated by the Cursor / Blink Control Circuit. The cursor or the blinking will appear with the digit located at the Display Data RAM (DDRAM) Address Set in the Address Counter (AC).

| AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 1   | 0   | 0   | 0   |

#### **CASE 1: FOR 1-LINE DISPLAY**

Example: When the Address Counter (AC) is set to 08H, the cursor position is displayed at DDRAM

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

Address 08H.

| Display Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9         | 10 | 11 |  |

|------------------|----|----|----|----|----|----|----|----|-----------|----|----|--|

| DDRAM Address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | NO.       | 09 | 0A |  |

| (hexadecimal)    | 00 | 01 | 02 | 03 | 04 | US | 00 | 07 | <u>08</u> | 09 | UA |  |

Cursor Position

Note:

The cursor or blinking appears when the Address Counter (AC) selects the Character Generator RAM (CGRAM). When the AC selects CGRAM Address, then the cursor or the blinking is displayed in a irrelevant and meaningless position.

#### **CASE 2: FOR 2-LINE DISPLAY**

Example: When the Address Counter (AC) is set to 08H, the cursor position is displayed at DDRAM Address 08H.

| Display Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9           | 10 | 11 |  |

|------------------|----|----|----|----|----|----|----|----|-------------|----|----|--|

| DDRAM Address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 108         | 09 | 0A |  |

| (hexadecimal)    | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | <b>7</b> 48 | 49 | 4A |  |

Cúrsor Position

Note:

The cursor or blinking appears when the Address Counter (AC) selects the Character Generator RAM (CGRAM). When the AC selects CGRAM Address, then the cursor or the blinking is displayed in a irrelevant and meaningless position.

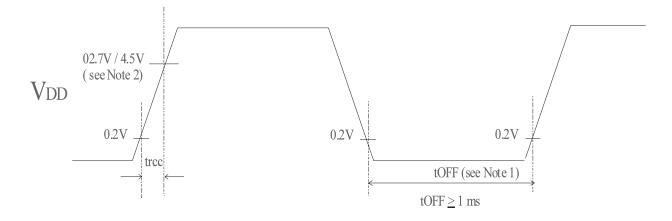

### Reset Function

#### INTERNAL RESET CIRCUIT INITIALIZATION

When power is turned ON, PT6880 is initialized automatically by an internal reset circuit. The following instructions are executed during the initialization.

1. Display Clear

2. Function Set: DL = "1" : 8-Bit Interface Data

N = "0" : 1-Line Display

$F = "0": 5 \times 8 \text{ Dot Character Font}$

3. Display ON/OFF Control: D = "0" : Display OFF

Fax: 886-2-29174598

Tel: 886-2-29162151

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

C = "0" : Cursor OFFB = "0" : Blinking OFF

I/D = "1": Increment by 1 4. Entry Mode Set:

S = "0" : No Shift

The Busy Flag (BF) is in a busy state until the initialization is completed (BF="1"). The busy state will be in effect 10 ms after the VDD rises to 4.5 Volts.

Please note that in order for the initialization by internal reset circuit to be successful, the electrical characteristic conditions listed in the Electrical Characteristics Section must be complied with. Otherwise, such initialization must be performed by instruction from the MPU.

#### Instructions

PT6880's Instruction Register (IR) and Data Register (DR) are the only registers that can be controlled by the MPU. Prior to the commencement of it internal operation, PT6880 temporarily stores the control information to its Instruction Register (IR) and Data Register (DR) in order to easily facilitate interface with various types of MPU. The internal operation of the PT6880 are determined by the signals (RS. R/WB, DB0 to DB7) that are sent from the MPU. These signals are categorized into 4 instructions types, namely:

- Function Setting Instructions (i.e. Display, Format, Data Length etc.) 1.

- **Internal RAM Address Setting Instructions**

- 3. Data Transfer with Internal RAM Instructions

- 4 Miscellaneous Function Instructions

The generally used instructions are those that execute data transfers with the internal RAM. However, when the internal RAM addresses are auto incremented/decremented by 1 after each Data Write, the program load of the MPU is lightened. The Display Shift Instruction can be executed at the same time as the Display Data Write, thereby minimizing system development time with maximum programming efficiency.

When an instruction is being executed for an internal operation, only the Busy Flag/Address Read Instruction can be performed. The other instructions are not valid. It should be noted that during the execution of an instruction, the Busy Flag is set to "1". The Busy Flag is set to "0" when the instructions are can be accepted and executed. Therefore, the Busy Flag should be checked to make certain that BF = "0" before sending another instruction from the MPU. If not, the time between the first instruction and the next instruction is longer than the time it takes to execute the instruction itself.

| Instruction | Code | Description | Max.<br>Execution |

|-------------|------|-------------|-------------------|

| mstruction  | Code | Description | Execution         |

|             |      |             | Time when         |

URL: http://www.princeton.com.tw

# OLED Driver/Controller IC

# **Preliminary**

PT6880

|                                                | R<br>S | R/WB | DB7 | DB6 | DB5 | DB4   | DB3  | DB2 | DB1 | DB0 |                                                                                                                                     | fsp or fosc = 250kHz |

|------------------------------------------------|--------|------|-----|-----|-----|-------|------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Clear<br>Display                               | 0      | 0    | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   | Clears entire display.<br>Sets DDRAM Address 0<br>into the Address Counter                                                          | ZSUKHZ               |

| Return<br>Home                                 | 0      | 0    | 0   | 0   | 0   | 0     | 0    | 0   | 1   | x   | Sets DDRAM Address 0 into the Address Counter.  Returns shifted display to original position.  DDRAM contents remain unchanged.     | 1.52ms               |

| Entry<br>Mode Set                              | 0      | 0    | 0   | 0   | 0   | 0     | 0    | 1   | I/D | S   | Sets cursor move<br>direction and specifies<br>display shift.<br>(These operations are<br>performed during data<br>write and read.) | 37us                 |

| Display<br>ON/OFF<br>Control                   | 0      | 0    | 0   | 0   | 0   | 0     | 1    | D   | С   | В   | Sets entire Display (D) ON/OFF.  Sets Cursor (C) ON/OFF.  Sets Blinking(B) of Cursor Position Character.                            | 37us                 |

| Cursor/<br>Display<br>Shift                    | 0      | 0    | 0   | 0   | 0   | 1     | S/C  | R/L | х   | X   | Moves cursor & shifts display without changing DDRAM contents.                                                                      | 37us                 |

| Function<br>Set                                | 0      | 0    | 0   | 0   | 1   | DL    | N    | F   | x   | X   | Sets interface data length (DL). Sets number of display lines (N). Sets Character Font (F).                                         | 37us                 |

| Set<br>CGRAM<br>Address                        | 0      | 0    | 0   | 1   | ACG | ACG   | ACG  | ACG | ACG | ACG | Sets CGRAM Address.<br>CGRAM data is sent and<br>received after this setting.                                                       | 37us                 |

| Set<br>DDRAM<br>Address                        | 0      | 0    | 1   | ADD | ADD | ADD   | ADD  | ADD | ADD | ADD | Sets DDRAM Address.<br>The DDRAM data Is sent<br>and received after this<br>setting.                                                | 37us                 |

| Read Busy<br>Flag &<br>Address                 | 0      | 1    | BF  | AC  | AC  | AC    | AC   | AC  | AC  | AC  | Reads Busy Flag (BF) indicating that internal operation is being performed. Reads Address Counter contents.                         | Ous                  |

| Write data<br>into the<br>CGRAM<br>or<br>DDRAM | 1      | 0    |     |     |     | Write | Data |     |     |     | Writes data into the<br>CGRAM or DDRAM                                                                                              | 37us<br>tADD=4us*    |

| Read Data<br>from the<br>CGRAM                 | 1      | 1    |     |     |     | Read  | Data |     |     |     | Read data from the<br>CGRAM or DDRAM                                                                                                | 37us<br>tADD=4us*    |

Fax: 886-2-29174598

Tel: 886-2-29162151

URL: http://www.princeton.com.tw

#### OLED Driver/Controller IC

**Preliminary**

PT6880

| _ |       |  |  |  |

|---|-------|--|--|--|

| ſ | or    |  |  |  |

|   | DDRAM |  |  |  |

| - |       |  |  |  |

Notes:

- 1. x = Not Relevant

- 2. \* = After the CGRAM/DDRAM Read or Write Instruction has been executed, the RAM Address Counter is incremented or decremented by 1. After the Busy Flag is turned OFF, the RAM Address is updated.

- 3. I/D = Increment / Decrement Bit

I/D = "1" : Increment

I/D = "0" : Decrement

- 4. S = Shift Entire Display Control Bit

- 5. BF = Busy Flag

BF = "1": Internal Operating in Progress

BF = "0": No Internal Operation is being executed, next instruction can be accepted.

6. R/L = Shift Right / Left

R/L = "1" : Shift to the Right

R/L = "0": Shift to the Left

7. S/C = Display Shift / Cursor Move

S/C = "1" : Display Shift

S/C = "0" : Cursor Move

- 8. DDRAM = Display Data RAM

- 9. CGRAM = Character Generator RAM

- 10. ACG = CGRAM Address

- 11. ADD = Address Counter Address (corresponds to cursor address)

- 12. AC = Address Counter (used for DDRAM and CGRAM Addresses)

- 13. F = Character Pattern Mode

$F = "1" : 5 \times 10 \text{ dots}$

$F = "0" : 5 \times 8 \text{ dots}$

14. N = Number of Lines Displayed

N = "1" : 2 -Line Display

N = "0" : 1-Line Display

15. \* = The time it takes to execute an instruction changes when the frequency changes. To illustrate an example: When fcp of fosc = 250 kHz, then

the execution time = 37 us x 270/250

=40us

16. tADD is the time period starting when the Busy Flag is turned OFF up to the time the Address Counter is updated. Please refer to the diagram below.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

where

1. tADD depends on the operation frequency and may be calculated using

the following equation

tADD = 1.5 / (fcp) seconds or tADD = 1.5 / (fosc) seconds

#### INSTRUCTION DESCRIPTION

#### Clear Display Instruction

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

This instruction is used to clear the Display Write Space 20H in all DDRAM Addresses. That is, the character pattern for the Character Code 20H must be a BLANK pattern. It then sets the DDRAM Address 0 into the Address Counter and reverts the display to its original state (if the display has been shifted). The display will be cleared and the cursor or blinking will go to the left edge of the display. If there are 2 lines displayed, the cursor or blinking will go to the first line 's left edge of the display. Under the Entry Mode, this instruction also sets the I/D to 1 (Increment Mode). The S Bit of the Entry Mode does not change.

#### Return Home Instruction

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | *   |

Note: \* = Not Relevant

This instruction is used to set the DDRAM Address 0 into the Address Counter and revert the display to its original status (if the display has been shifted). The DDRAM contents do not change. The cursor or blinking will go to the left edge of the display. If there are 2 lines displayed, the cursor or blinking will go to the first line 's left edge of the display.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

**Preliminary**

PT6880

#### **Entry Mode Set Instruction**

The Entry Mode Set Instruction has two controlling bits: I/D and S. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

#### I/D is the Increment / Decrement Bit.

When I/D is set to "1". the DDRAM Address is incremented by "1" when a character code is written into or read from the DDRAM. An increment of 1 will move the cursor or blinking one step to the right.

When the I/D is set to "0", the DDRAM is decremented by 1 when a character code is written into or read from the DDRAM. An decrement of 1 will move the cursor or blinking one step to the left.

#### S: Shift Entire Display Control Bit

This bit is used to shift the entire display. When S is set to "1", the entire display is shifted to the right (when I/D = "0") or left (when I/D = "1"). The display does not shift when reading from the DDRAM, writing into or reading from the CGRAM. When S is set to "0", the display is not shifted.

#### Display ON / OFF Control Instruction

The Display On / OFF Instruction is used to turn the display ON or OFF. The controlling bits are D, C and B.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 0   | 0   | D   | C   | В   |

#### D: Display ON /OFF Bit

When D is set to "1", the display is turned ON. When D is set to "0", the display is turned OFF and the display data is stored in the DDRAM. The display data can be instantly displayed by setting D to "1".

#### C: Cursor Display Control Bit

When C is set to "1", the cursor is displayed. In a  $5 \times 8$  dot character font, the cursor is displayed via the 5 dots in the 8th line. In a  $5 \times 10$  dot character font, it is displayed via 5 dots in the 11th line.

When C is set to "0", the cursor display is disabled.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

During a Display Data Write, the function of the I/D and others will not be altered even if the cursor is not present. Please refer to the figure below.

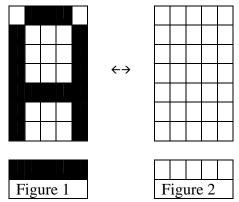

### **B**: Blinking Control Bit

When B is set to '1", the character specified by the cursor blinks. The blinking feature is displayed by switching between the blank dots and the displayed character at a speed of 409.6ms intervals when the fcp or fosc is 250kHz. Please refer to the figure below.

Note: Figure 1 and 2 are alternately displayed

The cursor and the blinking can be set to display at the same time. The blinking frequency depends on the fosc or the reciprocal of fcp.

To illustrate, when fcp =270kHz, then, the blinking frequency =  $409.6 \times 250/270 = 379.2$ ms *Cursor / Display Shift Instruction*

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

This instruction is used to shift the cursor or display position to the left or right without writing or reading the Display Data. This function is used to correct or search the display. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2         | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|-------------|-----|-----|

| 0  | 0    | 0   | 0   | 0   | 1   | S/C | <b>R</b> /L | *   | *   |

| S/C | R/L | Shift Function                                                                |

|-----|-----|-------------------------------------------------------------------------------|

| 0   | 0   | Shifts the cursor position to the left. (AC is decremented by 1).             |

| 0   | 1   | Shifts cursor position to the right. (AC incremented by 1).                   |

| 1   | 0   | Shifts entire display to the left. The cursor follows the display shift.      |

| 1   | 1   | Shifts the entire display to the right. The cursor follows the display shift. |

In a 2-line Display, the cursor moves to the second line when it passes the 40th digit of the first line. The first and second line displays will shift at the same time.

When the displayed data is shifted repeatedly, each line moves only horizontally. The second line display does not shift into the first line position.

The Address Counter (AC) contents will not change if the only action performed is a Display Shift.

#### Function Set Instruction

The Function Set Instruction has three controlling 3 bits, namely: DL, N and F. Please refer to the table below.

| RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2          | DB1 | DB0 |

|----|------|-----|-----|-----|-----|-----|--------------|-----|-----|

| 0  | 0    | 0   | 0   | 1   | DL  | N   | $\mathbf{F}$ | *   | *   |

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

#### **DL**: Interface Data Length Control Bit

This is used to set the interface data length. When DL is set to "1", the data is sent or received in 8-bit length via the DB0 to DB7 (for an 8-Bit Data Transfer). When DL is set to "0", the data is sent or received in 4-bit length via DB4 to DB7 (for a 4-Bit Data Transfer). When the 4-bit data length is selected, the data must be sent or received twice.

#### N: Number of Display Line

This is used to set the number of display lines. When N="1", the 2-line display is selected. When N is set to "0", the 1-line display is selected.

#### F: Character Font Set

This is used to set the character font set. When F is set to "0", the  $5 \times 8$  dot character font is selected. When F is set to "1", the  $5 \times 10$  dot character font is selected.

It must be noted that the character font setting must be performed at the head of the program before executing any instructions other than the Busy Flag and Address Instruction. Otherwise, the Function Set Instruction cannot be executed unless the interface data length is changed.

#### Set CGRAM Address Instruction

This instruction is used to set the CGRAM Address binary AAAAA into the Address Counter. Data is then written to or read from the MPU for CGRAM.

| ] | RS | R/WB | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|------|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0    | 0   | 0   | ACG | ACG | ACG | ACG | ACG | ACG |

Note: ACG is the CGRAM Address

#### Set DDRAM Address Instruction

This instruction is used to set the DDRAM Address binary AAAAAA into the Address Counter. The data is written to or read from the MPU for the DDRAM. If 1-line display is selected (N="0"), then AAAAAAA can be 00H to 4FH. When the 2-line display is selected, then AAAAAAA can be 00H to 27H for the first line and 40H to 67H for the second line.

| RS | R/WB | DB7 | DB6  | DB5     | DB4     | DB3 | DB2   | DB1     | DB0                  |

|----|------|-----|------|---------|---------|-----|-------|---------|----------------------|

| 0  | 0    | 1   | ADD  | ADD     | ADD     | ADD | ADD   | ADD     | ADD                  |

|    |      |     | ←Hig | her Ord | er Bits |     | Lower | r Order | Bits <del>&gt;</del> |

Note: ADD = DDRAM Address

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

#### Read Busy Flag and Address Instruction

This instruction is used to read the Busy Flag (BF) to indicate if PT6880 is internally operating on a previously received instruction. If BF is set to "1", then the internal operation is in progress and the next instruction will not be accepted. If the BF is set to "0", then the previously received instruction has been executed and the next instruction can be accepted and processed. It is important to check the BF status before proceeding to the next write operation. The value of the Address Counter in binary AAAAAA is simultaneously read out. This Address Counter is used by both the CGRAM and the DDRAM and its value is determined by the previous instruction. The contents of the address are the same as for the instructions -- Set CGRAM Address and Set DDRAM Address.

| RS | R/WB | DB7 | DB6          | DB5     | DB4     | DB3 | DB2   | DB1     | DB0    |

|----|------|-----|--------------|---------|---------|-----|-------|---------|--------|

| 0  | 1    | BF  | AC           | AC      | AC      | AC  | AC    | AC      | AC     |

|    |      |     | <b>←</b> Hig | her Ord | er Bits |     | Lower | Order 1 | Bits → |

Notes: 1. BF= Busy Flag

2. AC = Address Counter

#### Write Data to CGRAM / DDRAM Instruction

This instruction writes 8-bit binary data -- DDDDDDDD to the CGRAM or the DDRAM. The previous CGRAM or DDRAM Address setting determines whether a data is to be written into the CGRAM or the DDRAM. After the write process is completed, the address is automatically incremented or decremented by 1 in accordance with the Entry Mode instruction. It must be noted that the Entry Mode instruction also determines the Display Shift.

| RS | R/WB | DB7  | DB6    | DB5     | DB4 | DB3 | DB2 | DB1       | DB0      |

|----|------|------|--------|---------|-----|-----|-----|-----------|----------|

| 1  | 0    | D    | D      | D       | D   | D   | D   | D         | D        |

|    |      | ←Hig | her Or | der Bit | S   |     | Lov | wer Order | r Bits → |

#### Read Data from the CGRAM or DDRAM Instruction

This instructions reads the 8-bit binary data -- DDDDDDDD from the CGRAM or the DDRAM. The Set CGRAM Address or Set DDRAM Address Set Instruction must be executed before this instruction can be performed, otherwise, the first Read Data will not be valid.

| RS | R/WB | DB7  | DB6     | DB5     | DB4 | DB3 | DB2 | DB1       | DB0      |

|----|------|------|---------|---------|-----|-----|-----|-----------|----------|

| 1  | 1    | D    | D       | D       | D   | D   | D   | D         | D        |

|    |      | ←Hig | gher Or | der Bit | S   |     | Lov | wer Order | r Bits → |

When the Read Instruction is executed in series, the next address data is normally read from the Second Read. There is no need for the Address Set Instruction to be performed before this Read

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

instruction when using the Cursor Shift Instruction to shift the cursor (Reading the DDRAM). The Cursor Shift Instruction has the same operation as that of the Set the DDRAM Address Instruction.

After a Read instruction has been executed, the Entry Mode is automatically incremented or decremented by 1. It must be noted that regardless of the Entry Mode, the Display Shift is not executed.

After the Write instructions to either the CGRAM or DDRAM has been performed, the Address Counter is automatically increased or decreased by 1. The RAM data selected by the Address Counter cannot be read out at this time even if the Read Instructions are executed. Therefore, in order to correctly read the data, the following procedure has suggested:

- 1. Execute the Address Set or Cursor Shift (only with DDRAM) Instruction

- 2. Just before reading the desired data, execute the Read Instruction from the second time the Read Instruction has been sent.

#### MPU Interface

PT6880 can be configured to interface with either the 4-bit or 8-bit MPU via the DB0 to DB7 pins.

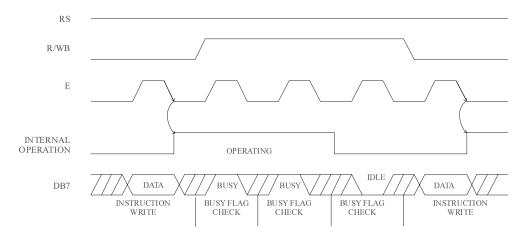

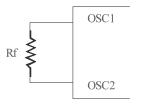

#### 8-BIT MPU INTERFACE

When PT6880 interfaces with an 8-bit MPU, DB0 to DB7 are used. The 8-bit data transfer starts from the four high order bits --DB4 to DB7 followed by the four low order bits -- DB0 to DB3. An example of a Busy Flag Check Timing in an 8-Bit MPU Interface is given in the diagram below.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

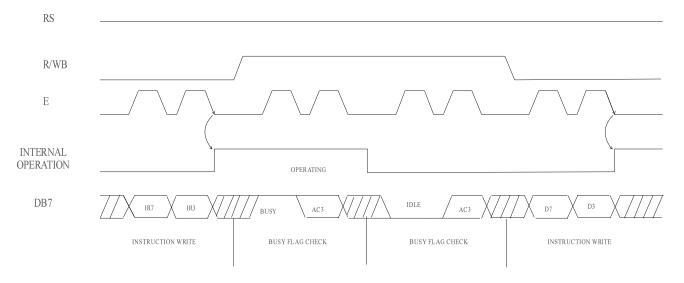

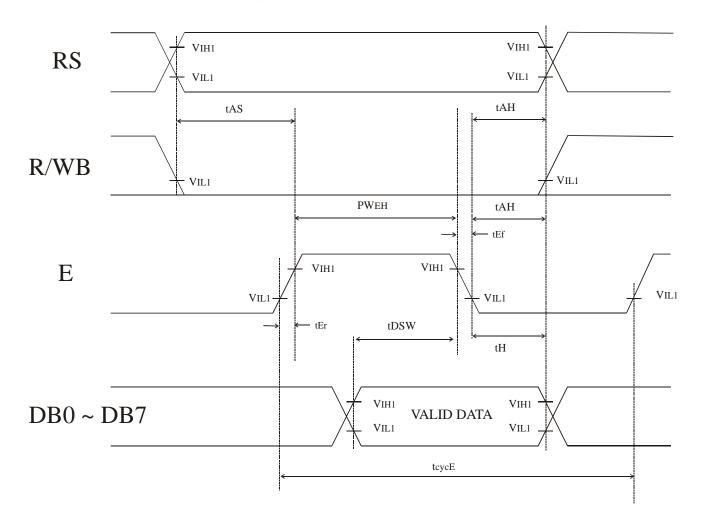

#### 4-BIT MPU INTERFACE

PT6880 can be configured to interface with a 4-bit MPU and is selected via a program. If the I/O port of the 4-Bit MPU from which PT6880 is connected to, is capable of transferring 8 bits, then an 8-bit data transfer operation is executed. Otherwise, two 4-bit data transfer operations are needed to satisfy one complete data transfer.

Under the 4-bit data transfer, DB4 to DB7 are used as bus lines. DB0 to DB3 are disabled. The data transfer between PT6880 and MPU is completed after two 4-bit data have been transferred. The Busy Flag must be checked (one instruction) after completion of the data transfer (that is, 4-bit data has been transferred twice.). The Busy Flag must be checked after two 4-bits data transfer has been completed. Please refer to the diagram below for a 4-bit data transfer timing sequence.

Where:

- 1. IR7 = Instruction Bit 7

- 2. IR3 = Instruction Bit 3

- 3. AC3 = Address Counter 3

From the above timing diagram, it is important to note that the Busy Flag Check and the data transfer are both executed twice.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

#### **OLED Interface**

PT6880 supports two display types, namely:  $5 \times 8$  dots and  $5 \times 10$  dots character fonts. Each of these type includes a cursor display. Up to 2 lines may be displayed in a  $5 \times 8$  dot character font type and 1 line for a  $5 \times 10$  dots character font type. The number of lines that can be displayed as well as the type of font can be selected by using the software program. Please refer to the table below

| Number of Display Line | Character Font Type  | Number of Common<br>Signals | Duty Factor |

|------------------------|----------------------|-----------------------------|-------------|

| 1                      | 5 x 8 dots + cursor  | 8                           | 1/8         |

| 1                      | 5 x 10 dots + cursor | 11                          | 1/11        |

| 2                      | 5 x 8 dots + cursor  | 16                          | 1/16        |

As shown in the table above, three types of common signals are available. An example of each configuration is shown in the examples below. It should be noted that every 5 segment signal lines can display one digit, therefore, PT6880 can display up to 8 digits in a 1-line display and 16 digits in a 2-line display.

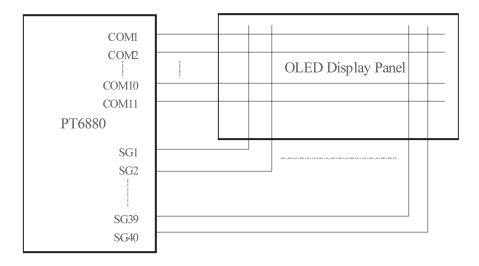

Example 1: An OLED and PT6880 interface with a 5 x 10 dot, 8-character x 1-line display at 1/11 duty cycle is given below.

URL: http://www.princeton.com.tw

# OLED Driver/Controller IC

# **Preliminary**

PT6880

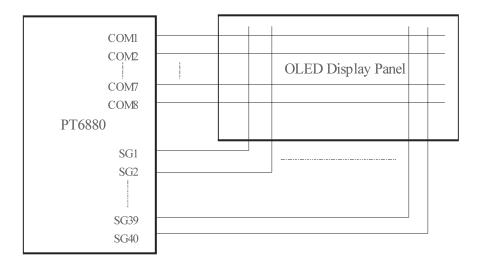

Example 2: OLED and PT6880 connection with 5 x 8 dots, 8-character x 1-line display, at 1/8 duty cycle.

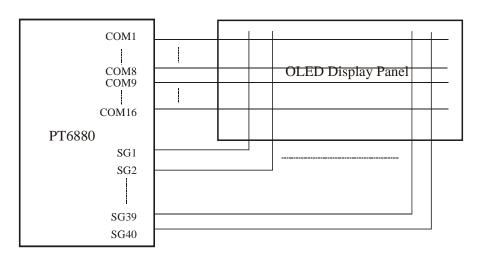

Example 3: OLED and PT6880 Connection when  $5 \times 8$  dots, 8-character  $\times$  2-line display at 1/16 duty cycle.

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

**Preliminary**

PT6880

# **Absolute Maximum Rating**

(Unless otherwise stated, Ta=25 °C)

| Parameter              | Symbol    | Rating          | Unit |

|------------------------|-----------|-----------------|------|

| Power Supply Voltage 1 | VDD-GND   | -0.3 to +5.5    | V    |

| Power Supply Voltage 2 | V16 -SEGG | -0.3 to +18.0   | V    |

| Input Voltage          | Vt        | -0.3 to VDD+0.3 | V    |

| Operating Temperature  | Topr      | -30 to +85      | °C   |

| Storage Temperature    | Tstg      | -55 to +125     | °C   |

### **DC Electrical Characteristics**

(Unless otherwise stated, Ta=25°C, V16=16V)

| Parameter                     | Symbol | Condition                                                   | Min.     | Тур. | Max.    | Unit |

|-------------------------------|--------|-------------------------------------------------------------|----------|------|---------|------|

|                               |        | All input pins and I/O pins except                          |          |      | Vdd     |      |

| High I and Imput              |        | OSC1<br>VDD=3V                                              | 0.7Vdd   | -    | VDD     | V    |

| High Level Input<br>Voltage 1 | VIH1   | All input pins and I/O pins except                          |          |      |         |      |

| voltage 1                     |        | OSC1                                                        | 2.2      | _    | Vdd     | V    |

|                               |        | VDD=5V                                                      | 2.2      |      | Vdd     | •    |

|                               |        | All input pins and I/O pins except                          |          |      |         |      |

|                               |        | OSC1                                                        | -0.3     | -    | 0.55    | V    |

| Low Level Input               | VIL1   | VDD=3V                                                      |          |      |         |      |

| Voltage 1                     | V IL1  | All input pins and I/O pins except                          |          |      |         |      |

|                               |        | OSC1                                                        | -0.3     | -    | 0.60    | V    |

|                               |        | VDD=5V                                                      |          |      |         |      |

|                               |        | OSC1                                                        | 0.7VDD   | _    | VDD     | V    |

| High Level Input              | VIH2   | VDD=3V                                                      | 0.7 VDD  | _    | V DD    | •    |

| Voltage 2                     | V 1112 | OSC1                                                        | VDD -1.0 | _    | VDD     | V    |

|                               |        | VDD=5V                                                      | VDD -1.0 | _    | V DD    | •    |

|                               |        | OSC1                                                        |          |      | 0.2 VDD | V    |

| Low Level Input               | VIL2   | VDD=3V                                                      | _        | _    | 0.2 100 | •    |

| Voltage 2                     | VIL2   | OSC1                                                        | _        | _    | 1.0     | V    |

|                               |        | VDD=5V                                                      | _        | _    | 1.0     | •    |

| High Level                    | Vou    | Applies to I/O Pins, DB0 to DB7, VDD=3V, IOH=-0.1mA         | 0.75VDD  | -    | -       | V    |

| Output Voltage 1              | VOH1   | Applies to I/O Pins, DB0 to DB7, VDD=4.5-5.5V, IOH=-0.205mA | 2.4      | -    | -       | V    |

URL: http://www.princeton.com.tw

# OLED Driver/Controller IC

# **Preliminary**

PT6880

| Ī-                                          |        |                                                                |        |     |            |    |

|---------------------------------------------|--------|----------------------------------------------------------------|--------|-----|------------|----|

| Low Level                                   | Vora   | Applies to I/O Pins, DB0 to DB7<br>VDD=3V, IOL=0.1mA           | -      | -   | 0.2VDD     | V  |

| Output Voltage 1                            | VOL1   | Applies to I/O Pins, DB0 to DB7<br>VDD=4.5-5.5V, IOL=1.2mA     | -      | -   | 0.1VDD     | V  |

| High Level                                  | Maria  | All Output Pins except DB0 to DB7.<br>VDD=3V, IOH=0.04mA       | 0.8VDD | -   | -          | V  |

| Output Voltage 2                            | VOH2   | All Output Pins except DB0 to DB7.<br>VDD=4.5-5.5V, IOH=0.04mA | 0.9VDD | -   | -          | V  |

| Low Level                                   | Vora   | All Output Pins except DB0 to DB7. VDD=3V, IOL=0.04mA          | -      | -   | 0.2VDD     | V  |

| Output Voltage 2                            | VOL2   | All Output Pins except DB0 to DB7.<br>VDD=4.5-5.5V, IOL=0.04mA | -      | -   | 0.1VDD     | V  |

| Input Leakage<br>Current                    | ILI    | VDD=3V, VIN= 0 to VDD                                          | -1     | ı   | 1          | uA |

| (see Note 1)                                | ILI    | VDD=5V, VIN= 0 to VDD                                          | -1     | -   | 1          | uA |

| Pull-up MOS                                 | I.a    | DB0 to DB7, RS, R/WB VIN=3.0V                                  | 10     | 50  | 120        | uA |

| Current                                     | -Ip    | DB0 to DB7, RS, R/WB VIN=5.0V                                  | 50     | 125 | 250        | uA |

| Operating                                   | T      | Rf Oscillation, External Clock<br>VDD=3V, fosc=270kHz          | -      | -   | 1          | mA |

| Current (see Notes 2)                       | Icc    | Rf Oscillation, External Clock<br>VDD=5V, fosc=270kHz          | -      | -   | 1          | mA |

| OLED William                                | Volum  | V16 - SEGG<br>VDD=3V                                           | 9.0    | -   | 16.0       | V  |

| OLED Voltage                                | VOLED  | V16 - SEGG<br>VDD=5V                                           | 9.0    | -   | 16.0       | V  |

| High Level Segment Output Current           | ISEGOH | VSEGOH=14V                                                     | -30    | -   | -300       | uA |

| High Level Segment Output Current Tolerance | ITOL1* | ISEGOH=-300uA                                                  | -      | -   | ±5         | %  |

| High Level Segment Output Current Tolerance | ITOL2* | ISEGOH=-300uA                                                  | -      | -   | <u>+</u> 1 | %  |

| Low level<br>Common<br>Sink Current         | Ісомоц | VCOMOL=0.4V                                                    | 15     | -   | -          | mA |

URL: http://www.princeton.com.tw

### OLED Driver/Controller IC

# **Preliminary**

PT6880

Notes:

- 1. Current flowing through pull-up MOSs, excluding output drive MOS.

- 2. Input/Output current is not included. When the input is at an intermediate level with the CMOS, the excessive current flows through the input circuit to the power supply. To avoid this from happening, the input level must be fixed high or low.

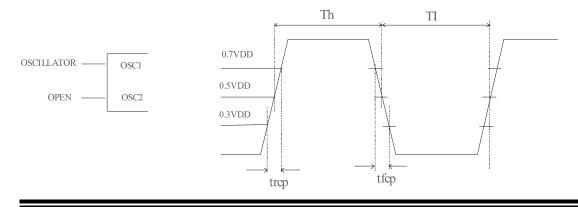

# **AC Electrical Characteristics**

(Unless otherwise specified,  $Ta = 25^{\circ}C$ , V16=16V)

| Parameter                      | Symbol | Condition                                                      |     | Тур. | Max. | Unit |

|--------------------------------|--------|----------------------------------------------------------------|-----|------|------|------|

| External Clock<br>Frequency    | fcp    | Applies only to external clock operation. (see Note 1), VDD=3V |     | 250  | 350  | kHz  |

|                                |        | Applies only to external clock operation. (see Note 1), VDD=5V | 125 | 250  | 350  | kHz  |

| External Clock Rise<br>Time    | tran   | Applies only to external clock operation. (see Note 1), VDD=3V | 1   | 1    | 0.2  | us   |

|                                | trcp   | Applies only to external clock operation. (see Note 1), VDD=5V | -   | -    | 0.2  | us   |