# INTEGRATED CIRCUITS

# DATA SHEET

# PCF2119x-2 LCD controllers/drivers

Product specification

File under Integrated Circuits, IC12

28. August 2000

| CONTEN      | тѕ                                                                    | 9                      | EXTENDED FUNCTION SET                                |

|-------------|-----------------------------------------------------------------------|------------------------|------------------------------------------------------|

| 1           | FEATURES                                                              |                        | INSTRUCTIONS AND FEATURES                            |

| 1.1         | Note                                                                  | 9.1                    | New instructions                                     |

|             |                                                                       | 9.2                    | Icon control                                         |

| 2           | APPLICATIONS                                                          | 9.3<br>9.4             | IM<br>IB                                             |

| 3           | GENERAL DESCRIPTION                                                   | 9. <del>4</del><br>9.5 | Normal/icon mode operation                           |

| 4           | ORDERING INFORMATION                                                  | 9.6                    | Screen configuration                                 |

| 5           | BLOCK DIAGRAM                                                         | 9.7                    | Display configuration                                |

| 6           | PAD INFORMATION                                                       | 9.8                    | TC1 and TC2                                          |

| 6.1         | Pad functions                                                         | 9.9<br>9.10            | Set V <sub>LCD</sub> Reducing current consumption    |

| 7           | FUNCTIONAL DESCRIPTION                                                | 10                     | INTERFACES TO MPU                                    |

| 7.1         | LCD supply voltage generator                                          |                        |                                                      |

| 7.2         | Programming ranges                                                    | 10.1                   | Parallel interface                                   |

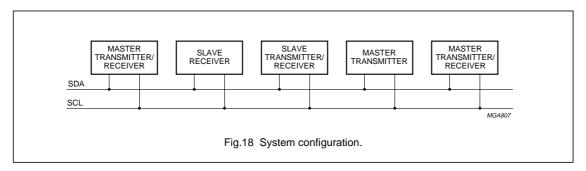

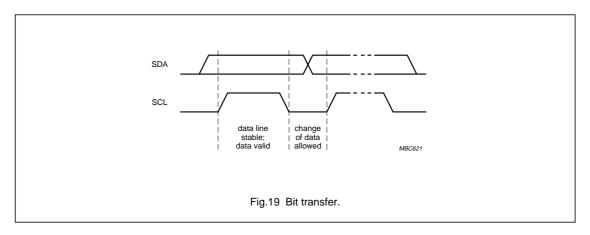

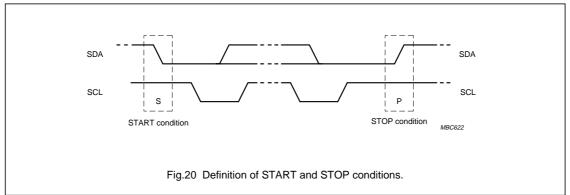

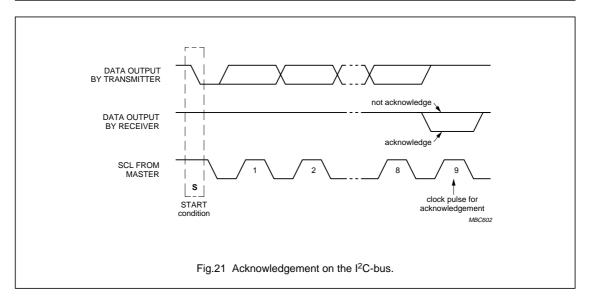

| 7.3         | LCD bias voltage generator                                            | 10.2                   | I <sup>2</sup> C-bus interface                       |

| 7.4         | Oscillator                                                            | 11                     | LIMITING VALUES                                      |

| 7.5         | External clock                                                        | 12                     | HANDLING                                             |

| 7.6         | Power-on reset                                                        | 13                     | DC CHARACTERISTICS                                   |

| 7.7         | Power-down mode                                                       | 14                     | AC CHARACTERISTICS                                   |

| 7.8         | Registers                                                             | 15                     | TIMING CHARACTERISTICS                               |

| 7.9<br>7.10 | Busy flag<br>Address Counter (AC)                                     |                        |                                                      |

| 7.10        | Display Data RAM (DDRAM)                                              | 16                     | APPLICATION INFORMATION                              |

| 7.12        | Character Generator ROM (CGROM)                                       | 16.1                   | General Application Information                      |

| 7.13        | Character Generator RAM (CGRAM)                                       | 16.2                   | 8-bit operation, 1-line display using external       |

| 7.14        | Cursor control circuit                                                | 16.3                   | reset 4-bit operation, 1-line display using external |

| 7.15        | Timing generator                                                      | 10.5                   | reset                                                |

| 7.16        | LCD row and column drivers                                            | 16.4                   | 8-bit operation, 2-line display                      |

| 7.17        | Reset function                                                        | 16.5                   | I <sup>2</sup> C-bus operation, 1-line display       |

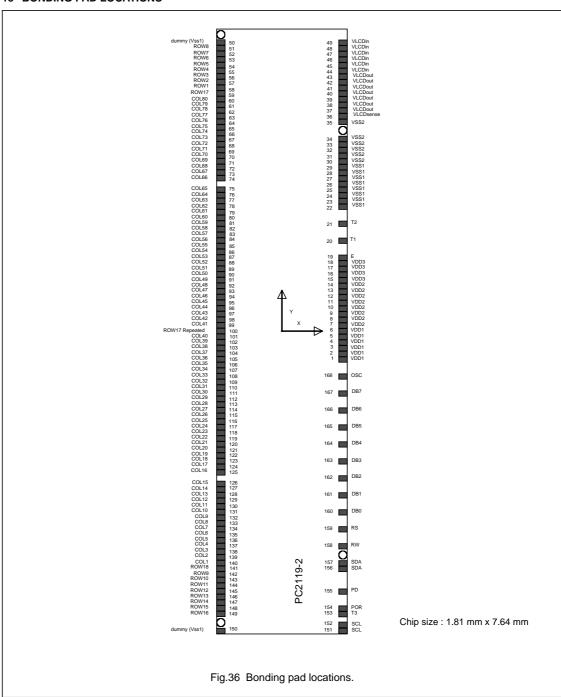

| 8           | INSTRUCTIONS                                                          | 17                     | BONDING PAD LOCATIONS                                |

| 8.1         | Clear display                                                         | 18                     | DEFINITIONS                                          |

| 8.2         | Return home                                                           | 19                     | LIFE SUPPORT APPLICATIONS                            |

| 8.3         | Entry mode set                                                        | -                      |                                                      |

| 8.4<br>8.5  | Display control (and partial power-down mode) Cursor or display shift | 20                     | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS      |

| 8.6         | Function set                                                          |                        |                                                      |

| 8.7         | Set CGRAM address                                                     |                        |                                                      |

| 8.8         | Set DDRAM address                                                     |                        |                                                      |

| 8.9         | Read busy flag and read address                                       |                        |                                                      |

| 8.10        | Write data to CGRAM or DDRAM                                          |                        |                                                      |

| 8.11        | Read data from CGRAM or DDRAM                                         |                        |                                                      |

### PCF2119x-2

#### 1 FEATURES

- Single-chip LCD controller/driver

- 2-line display of up to 16 characters + 160 icons, or 1-line display of up to 32 characters + 160 icons

- 5 x 7 character format plus cursor; 5 x 8 for kana (Japanese) and user defined symbols

- Icon mode: reduced current consumption while displaying icons only

- · Icon blink function

- · On-chip:

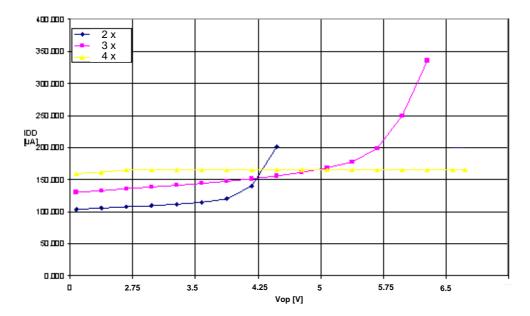

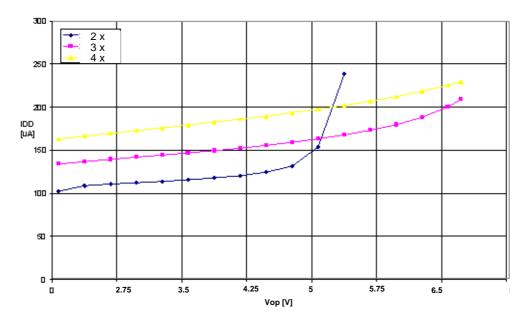

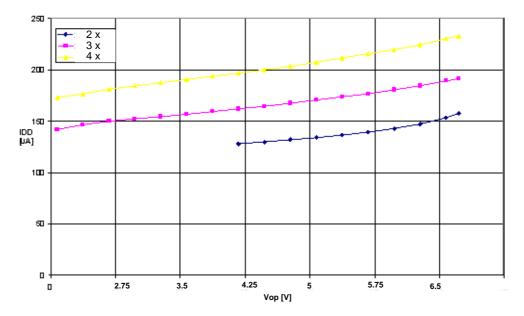

- Configurable 4 (3, 2) \* voltage multiplier generating LCD supply voltage, independent of V<sub>DD</sub>, programmable by instruction (external supply also possible)

- Temperature compensation of on-chip generated V<sub>LCD</sub>: -0.16 to -0.24 %/K (programmable by instruction)

- Generation of intermediate LCD bias voltages

- Oscillator requires no external components (external clock also possible).

- Display Data RAM: 80 characters

- Character Generator ROM: 240, 5 × 8 characters

- Character Generator RAM: 16, 5 × 8 characters;

4 characters used to drive 160 icons, 8 characters used if icon blink feature is used in application

- 4 or 8-bit parallel bus and 2-wire I2C-bus interface

- CMOS compatible

- 18 row and 80 column outputs

- Multiplex rates 1:18 (for normal operation), 1:9 (for single line operation) and 1:2 (for icon only mode)

- Uses common 11 code instruction set (extended)

- Logic supply voltage range, V<sub>DD1</sub> V<sub>SS</sub> = 1.5 to 5.5 V (chip may be driven with two battery cells)

- HVgen supply voltage range,  $V_{DD2,3} V_{SS} = 2.2$  to 4.0V

- Display supply voltage range, V<sub>LCD</sub> V<sub>SS</sub> = 2.2 to 6.5 V

- Direct mode to save current consumption for icon mode and Mux 1:9 (depending on V<sub>DD2</sub> value and LCD liquid properties)

- Very low current consumption (20 to 200 μA):

- Icon mode: <25 μA</li>

- Power-down mode: <2  $\mu$ A.

#### 1.1 Note

Icon mode is used to save current. When only icons are displayed, a much lower operating voltage  $V_{LCD}$  can be used and the switching frequency of the LCD outputs is reduced. In most applications it is possible to use  $V_{DD}$  as  $V_{LCD}$ .

### 2 APPLICATIONS

- · Telecom equipment

- · Portable instruments

- · Point-of-sale terminals.

### 3 GENERAL DESCRIPTION

The PCF2119x is a low power CMOS LCD controller and driver, designed to drive a dot matrix LCD display of 2-line by 16 or 1-line by 32 characters with  $5\times 8$  dot format. All necessary functions for the display are provided in a single chip, including on-chip generation of LCD bias voltages, resulting in a minimum of external components and lower system current consumption. The PCF2119x interfaces to most microcontrollers via a 4 or 8-bit bus or via the 2-wire  $I^2$ C-bus. The chip contains a character generator and displays alphanumeric and kana (Japanese) characters. The letter 'x' in PCF2119x characterizes the built-in character set. Various character sets can be manufactured on request.

### 4 ORDERING INFORMATION

| TYPE       |      | PACKAGE                 |         |

|------------|------|-------------------------|---------|

| NUMBER     | NAME | DESCRIPTION             | VERSION |

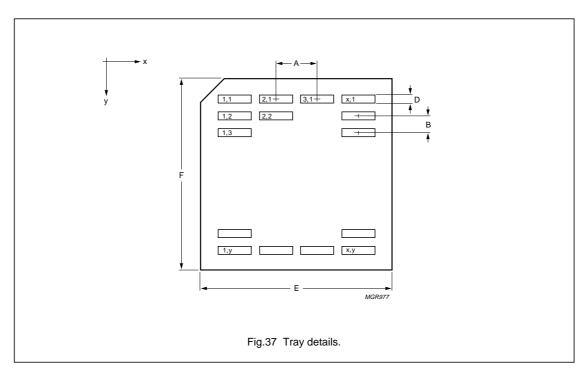

| PC2119RU/2 | -    | chip with bumps in tray | -       |

| PC2119SU/2 | _    | chip with bumps in tray | _       |

| PC2119VU/2 | _    | chip with bumps in tray | _       |

### PCF2119x-2

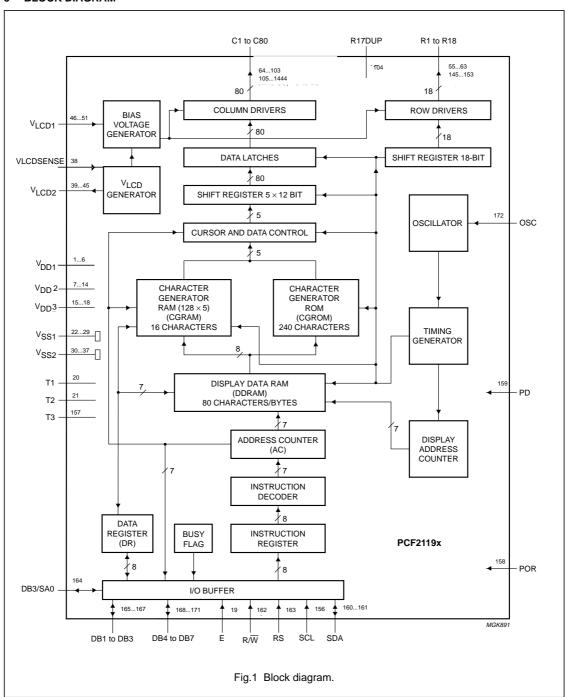

### 5 BLOCK DIAGRAM

### LCD controllers/drivers

PCF2119x-2

### 6 PAD INFORMATION

The identification of each pad and its location is given in Chapter 18.

### 6.1 Pad functions

Table 1 Pad function description

| SYMBOL                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

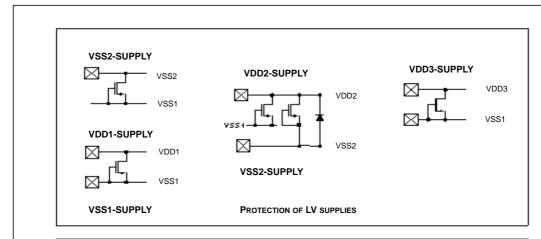

| V <sub>DD1</sub>      | Logic supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>DD2,3</sub>    | High voltage generator supply voltages (always put V <sub>DD2</sub> = V <sub>DD3</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SS1</sub>      | This is the ground pad for all except the high voltage generator.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SS2</sub>      | This is the ground pad for the high voltage generator.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>LCD1</sub>     | This input is used for the generation of the LCD bias levels.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>LCD2</sub>     | This is the $V_{LCD}$ output pad if $V_{LCD}$ is generated internally. This pad must be connected to $V_{LCD1}$ .                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>LCDSENSE</sub> | This input ( $V_{LCD}$ ) is used for the voltage multiplier's regulation circuitry. This pad must be connected to $V_{LCD2}$ .                                                                                                                                                                                                                                                                                                                                                                |

| E                     | The data bus clock input is set HIGH to signal the start of a read or write operation; data is clocked in or out of the chip on the negative edge of the clock; note 1.                                                                                                                                                                                                                                                                                                                       |

| T1                    | These are three test pads. T1 and T2 must be connected to V <sub>SS1</sub> ; T3 is left open-circuit and is not user                                                                                                                                                                                                                                                                                                                                                                          |

| T2                    | accessible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| T3                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| R1 to R18;<br>R17DUP  | LCD row driver outputs R1 to R18; these pads output the row select waveforms to the display; R17 and R18 drive the icons. R17 has two pads R17 and R17DUP.                                                                                                                                                                                                                                                                                                                                    |

| C1 to C80             | LCD column driver outputs C1 to C80.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SCL                   | I <sup>2</sup> C-bus serial clock input; note 1.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| POR                   | External power-on reset input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PD                    | PD selects the chip power-down mode; for normal operation PD = 0.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDA                   | I <sup>2</sup> C-bus serial data input/output; note 1.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R/W                   | This is the read/write input. $R/\overline{W}$ selects either the read $(R/\overline{W} = 1)$ or write $(R/\overline{W} = 0)$ operation. This pad has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                           |

| RS                    | The RS input selects the register to be accessed for read and write. RS = 0, selects the instruction register for write and the busy flag and address counter for read. RS = 1, selects the data register for both read and write. This pad has an internal pull-up resistor.                                                                                                                                                                                                                 |

| DB0 to DB7            | The 8-bit bidirectional data bus (3-state) transfers data between the system controller and the PCF2119x. DB7 may be used as the busy flag, signalling that internal operations are not yet completed. In 4-bit operations the 4 higher order lines DB7 to DB4 are used; DB3 to DB0 must be left open-circuit. Data bus line DB3 has an alternative function (SA0), when selected this is the I <sup>2</sup> C-bus address pad. Each data line has its own internal pull-up resistor; note 1. |

| OSC                   | Oscillator or external clock input. When the on-chip oscillator is used this pad must be connected to $V_{DD1}$ .                                                                                                                                                                                                                                                                                                                                                                             |

#### Note

- When the I<sup>2</sup>C-bus is used, the parallel interface pad E must be at logic 0. In the I<sup>2</sup>C-bus read mode DB0 DB2 and DB3 - DB7 should be connected to V<sub>DD1</sub> or left open-circuit.

- a) When the parallel bus is used, pads SCL and SDA must be connected to V<sub>SS1</sub> or V<sub>DD1</sub>; they must not be left open-circuit.

- b) If the 4-bit interface is used without reading out from the PCF2119x (i.e.  $R/\overline{W}$  is set permanently to logic 0), the unused ports DB0 to DB4 can either be set to  $V_{SS1}$  or  $V_{DD1}$  instead of leaving them open-circuit.

PCF2119x-2

### 7 FUNCTIONAL DESCRIPTION

### 7.1 LCD supply voltage generator

The LCD supply voltage may be generated on-chip. The voltage generator is controlled by two internal 6-bit registers:  $V_A$  and  $V_B$ . The nominal LCD operating voltage at room temperature is given by the relationship:

$V_{OP(nom)} = (integer value of register \times 0.08) + 1.82$

#### 7.2 Programming ranges

Programmed value: 1 to 63. Voltage: 1.90 to 6.86 V.  $T_{\text{ref}}$  = 27  $^{\circ}\text{C}$  .

Values producing more than 6.5 V at operating temperature are not allowed. Operation above this voltage may damage the device. When programming the operating voltage the  $V_{LCD}$  temperature coefficient must be taken into account.

Values below 2.2 V are below the specified operating range of the chip and are therefore not allowed.

Value 0 for  $V_A$  and  $V_B$  switches the generator off (i.e.  $V_A = 0$  in character mode,  $V_B = 0$  in icon mode).

Usually register  $V_A$  is programmed with the voltage for character mode and register  $V_B$  with the voltage for icon mode.

When  $V_{LCD}$  is generated on-chip the  $V_{LCD}$  pads should be decoupled to  $V_{SS}$  with a suitable capacitor. The generated  $V_{LCD}$  is independent of  $V_{DD}$  and is temperature compensated. When the voltage generator and the direct mode are switched off, an external voltage may be supplied at connected pads  $V_{LCD1,2}$ .  $V_{LCD1,2}$  may be higher or lower than  $V_{DD}$ .

During direct mode (program DM register bit) the internal voltage generator is turned off and the  $V_{LCD}$  output voltage is directly connected to  $V_{DD2}$ . This reduces the current consumption during icon mode and Mux 1 : 9 (depending on  $V_{DD2}$  value and LCD liquid properties).

The LCD supply voltage generator ensures that, as long as  $V_{DD}$  is in the valid range (2.2 to 4 V), the required peak voltage  $V_{OP} = 6.5$  V can be generated at any time.

### 7.3 LCD bias voltage generator

The intermediate bias voltages for the LCD display are also generated on-chip. This removes the need for an external resistive bias chain and significantly reduces the system current consumption. The optimum value of  $V_{LCD}$  depends on the multiplex rate, the LCD threshold voltage  $(V_{th})$  and the number of bias levels. Using a 5-level bias scheme for 1 : 18 maximum rate allows  $V_{LCD} < 5 \ V$  for most LCD liquids. The intermediate bias levels for the different multiplex rates are shown in Table 2. These bias levels are automatically set to the given values when switching to the corresponding multiplex rate.

Table 2 Bias levels as a function of multiplex rate

| MULTIPLEX<br>RATE | NUMBER<br>OF LEVELS | V <sub>1</sub>  | V <sub>2</sub>     | V <sub>3</sub> | V <sub>4</sub> | V <sub>5</sub> | V <sub>6</sub>  |

|-------------------|---------------------|-----------------|--------------------|----------------|----------------|----------------|-----------------|

| 1 : 18            | 5                   | V <sub>op</sub> | 3/4 <sup>(1)</sup> | 1/2            | 1/2            | 1/4            | V <sub>ss</sub> |

| 1:9               | 5                   | V <sub>op</sub> | 3/4                | 1/2            | 1/2            | 1/4            | V <sub>ss</sub> |

| 1:2               | 4                   | V <sub>op</sub> | 2/3                | 2/3            | 1/3            | 1/3            | V <sub>ss</sub> |

#### Note

1. The values in the above table are given relative to  $V_{op} - V_{ss}$ , e.g. 3/4 means  $3/4 \times (V_{op} - V_{ss})$ .

### PCF2119x-2

### 7.4 Oscillator

The on-chip oscillator provides the clock signal for the display system. No external components are required and the OSC pad must be connected to  $V_{DD}$ .

#### 7.5 External clock

If an external clock is to be used this is input at the OSC pad. The resulting display frame frequency is given by:

$$f_{frame} \, = \, \frac{f_{OSC}}{3\,072}$$

Only in the power-down state is the clock allowed to be stopped (OSC connected to  $V_{SS}$ ), otherwise the LCD is frozen in a DC state.

#### 7.6 Power-on reset

The PC2119x must be reset externally. This is an internal synchronous reset that requires 3 OSC cycles to be executed after release of the external reset signal. If no external reset is performed, the chip might start-up in an unwanted state. The external reset is active high.

#### 7.7 Power-down mode

The chip can be put into power-down mode by applying an external active high level to the PD pad. In power-down mode all static currents are switched off (no internal oscillator, no bias level generation and all LCD outputs are internally connected to  $V_{SS}$ ).

During power-down, information in the RAMs and the chip state are preserved. Instruction execution during power-down is possible when pad OSC is externally clocked.

### 7.8 Registers

The PCF2119x has two 8-bit registers, an Instruction Register (IR) and a Data Register (DR). The Register Select signal (RS) determines which register will be accessed. The instruction register stores instruction codes such as 'display clear' and 'cursor shift', and address information for the Display Data RAM (DDRAM) and Character Generator RAM (CGRAM).

The instruction register can be written to but not read from by the system controller. The data register temporarily stores data to be read from the DDRAM and CGRAM. When reading, data from the DDRAM or CGRAM corresponding to the address in the instruction register is written to the data register prior to being read by the 'read data' instruction.

#### 7.9 Busy flag

The busy flag indicates the internal status of the PCF2119x. A logic 1 indicates that the chip is busy and further instructions will not be accepted. The busy flag is output to pad DB7 when RS = 0 and  $R/\overline{W}$  = 1. Instructions should only be written after checking that the busy flag is at logic 0 or waiting for the required number of cycles.

### 7.10 Address Counter (AC)

The address counter assigns addresses to the DDRAM and CGRAM for reading and writing and is set by the commands 'set CGRAM address' and 'set DDRAM address'. After a read/write operation the address counter is automatically incremented or decremented by 1. The address counter contents are output to the bus (DB6 to DB0) when RS = 0 and  $R/\overline{W}$  = 1.

### 7.11 Display Data RAM (DDRAM)

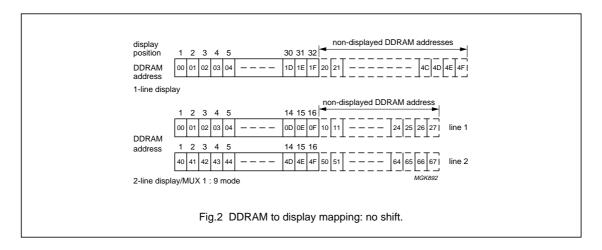

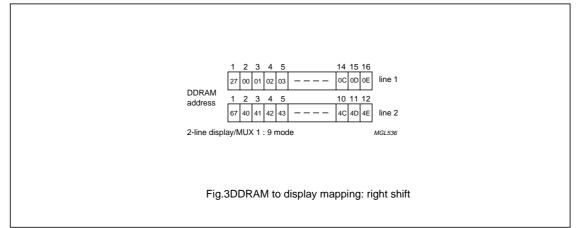

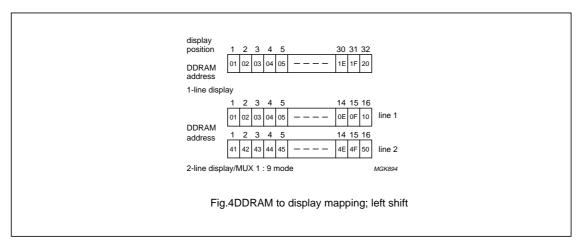

The DDRAM stores up to 80 characters of display data represented by 8-bit character codes. RAM locations which are not used for storing display data can be used as general purpose RAM. The basic RAM to display addressing scheme is shown in Fig.2. With no display shift the characters represented by the codes in the first 32 RAM locations starting at address 00H in line 1 are displayed. Figures 3 and 4 show the display mapping for right and left shift respectively.

When data is written to or read from the DDRAM wrap-around occurs from the end of one line to the start of the next line. When the display is shifted each line wraps around within itself, independently of the others. Thus all lines are shifted and wrapped around together.

The address ranges and wrap-around operations for the various modes are shown in Table 3.

Table 3 Address space and wrap-around operation

| MODE                                          | 1 × 32   | 2×16               | 1 × 9    |

|-----------------------------------------------|----------|--------------------|----------|

| Address space                                 | 00 to 4F | 00 to 27; 40 to 67 | 00 to 27 |

| Read/write wrap-around (moves to next line)   | 4F to 00 | 27 to 40; 67 to 00 | 27 to 00 |

| Display shift wrap-around (stays within line) | 4F to 00 | 27 to 00; 67 to 40 | 27 to 00 |

### LCD controllers/drivers

PCF2119x-2

#### 7.12 Character Generator ROM (CGROM)

The Character Generator ROM generates 240 character patterns in a  $5\times 8$  dot format from 8-bit character codes. Figure 6 to 8 show the character sets that are currently implemented.

#### 7.13 Character Generator RAM (CGRAM)

Up to 16 user defined characters may be stored in the Character Generator RAM. Some CGRAM characters (see Fig.17) are also used to drive icons (6 if icons blink and both icon rows are used in the application; 3 if no blink but both icon rows are used in the application; 0 if no icons are driven by the icon rows). The CGROM and CGRAM use a common address space, of which the first column is reserved for the CGRAM (see Fig.6). Figure 9 shows the addressing principle for the CGRAM.

#### 7.14 Cursor control circuit

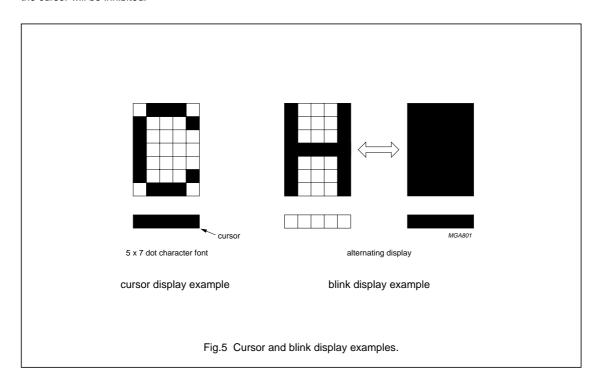

The cursor control circuit generates the cursor (underline and/or cursor blink as shown in Fig.5 at the DDRAM address contained in the address counter.

When the address counter contains the CGRAM address the cursor will be inhibited.

### 7.15 Timing generator

The timing generator produces the various signals required to drive the internal circuitry. Internal chip operation is not disturbed by operations on the data buses.

### 7.16 LCD row and column drivers

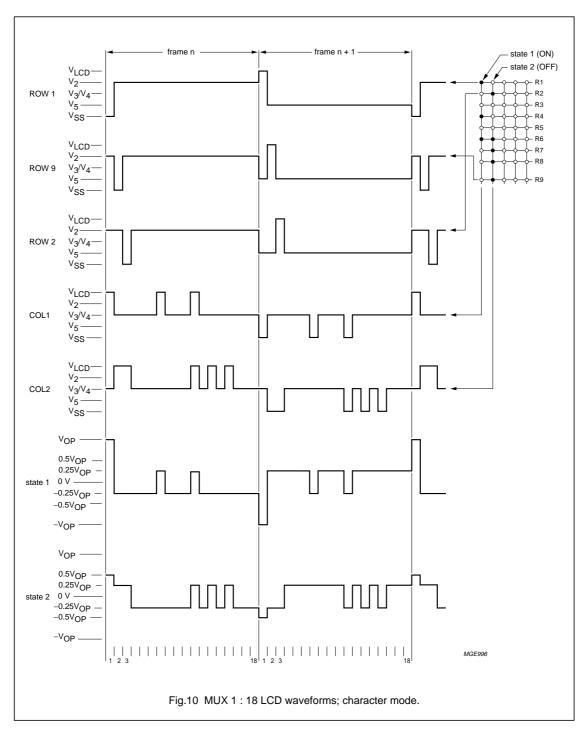

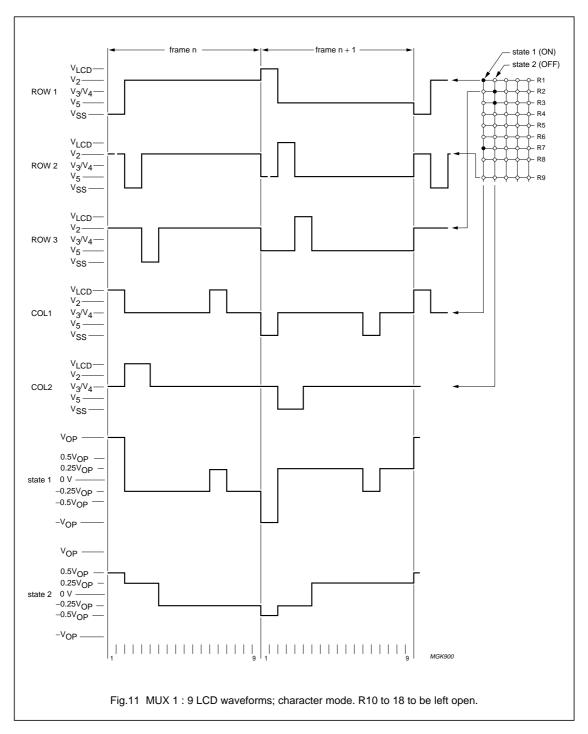

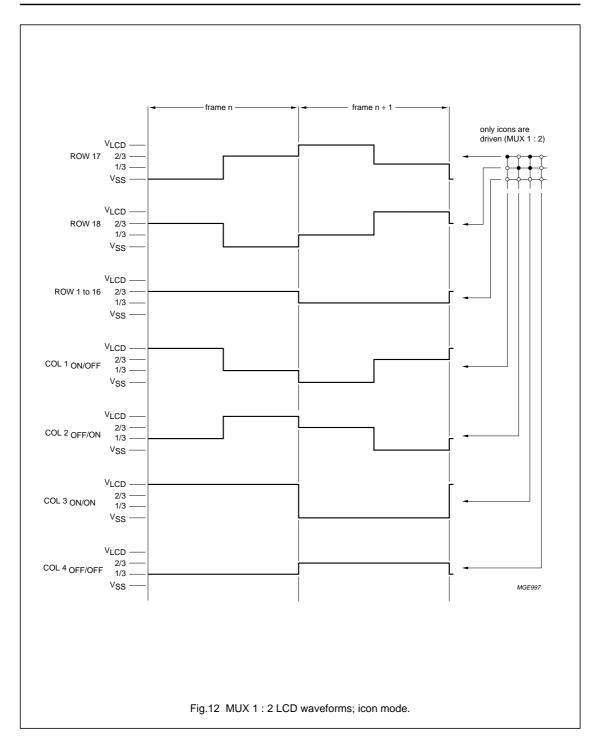

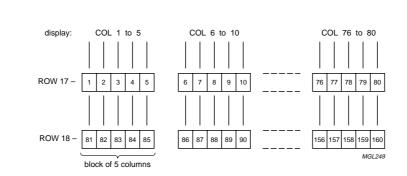

The PCF2119x contains 18 row and 80 column drivers, which connect the appropriate LCD bias voltages in sequence to the display in accordance with the data to be displayed. R17 and R18 drive the icon rows.

The bias voltages and the timing are selected automatically when the number of lines in the display is selected. Figures 10 to 13 show typical waveforms. Unused outputs should be left unconnected.

| lower<br>4 bits | upper<br>4 bits | 0000 | 0001         | 0010        | 0011     | 0100          | 0101 | 0110    | 0111         | 1000 | 1001      | 1010         | 1011 | 1100    | 1101 | 1110        | 11     |

|-----------------|-----------------|------|--------------|-------------|----------|---------------|------|---------|--------------|------|-----------|--------------|------|---------|------|-------------|--------|

| xxxx            | 0000            | 1    | -∰           | ₽           | -::      | •             |      |         |              |      |           |              |      |         |      | <u>:</u>    | j::    |

| xxxx            | 0001            | 2    |              |             |          |               |      | ===     |              |      |           | i            |      |         |      | -==         | ·::    |

| xxxx            | 0010            | 3    | <b>.:::.</b> |             | i.       |               | 1.   |         | <b></b>      |      |           | ::           |      |         |      | <u>:</u>    | ₽.     |

| xxxx            | 0011            | 4    |              |             | 1        |               |      | ===     | :::          |      |           |              | :    |         | :    | : <u></u> . | ::     |

| xxxx            | 0100            | 5    | -==          | ::::-       |          |               |      |         |              |      |           |              | :    |         |      |             | ÷      |

| xxxx            | 0101            | 6    |              | 1           | :        |               |      |         |              |      |           | #.: <u>.</u> |      |         |      |             | į      |

| xxxx            | 0110            | 7    | ===          | i           |          |               |      | ₽       | ij           |      |           |              |      | <b></b> | ij   | #*·         | ١.     |

| xxxx            | 0111            | 8    | #            | ::::-       | <b>:</b> |               |      |         | ii           | 1    | -         | :            | ···· |         |      | -:::        |        |

| xxxx            | 1000            | 9    | :-: <u>:</u> |             | ä        |               |      |         | $\mathbb{X}$ |      | :         |              |      |         | ×    | ŀ;          |        |

| xxxx            | 1001            | 10   |              | :           |          |               | 1    |         | <b></b>      | :::: |           |              | -    | II.     | Ŧ    | <u>:</u>    | ٠.     |

| xxxx            | 1010            | 11   | <u>:</u>     |             |          |               |      |         | :::::        | Ĭ.   | •••       | :‡:          | #    |         | :::  |             | :      |

| xxxx            | 1011            | 12   |              |             |          | :::           |      | E.      |              |      |           |              | ::   | E.      |      | Ŀ:          |        |

| xxxx            | 1100            | 13   |              | #.:         | ::       |               |      |         |              |      |           | :=           |      | <u></u> |      | 1           | Ė      |

| xxxx            | 1101            | 14   | :            |             | *:-      |               |      |         |              |      |           |              |      |         |      |             |        |

| xxxx            | 1110            | 15   |              | <u>::</u> . |          | . <b>ii</b> . |      | <b></b> |              |      | <b></b> : | ::           |      | : :     |      | <b>!</b> ": | :<br>: |

| xxxx            | 1111            | 16   |              |             |          |               |      |         | -            |      |           |              | •    |         |      | ::::        | .:     |

Fig.6 Character set 'R' in CGROM.

| lower<br>4 bits | upper<br>4 bits | 0000 | 0001         | 0010  | 0011       | 0100 | 0101     | 0110         | 0111         | 1000    | 1001     | 1010     | 1011 | 1100 | 1101 | 1110        | 11 |

|-----------------|-----------------|------|--------------|-------|------------|------|----------|--------------|--------------|---------|----------|----------|------|------|------|-------------|----|

| xxxx            | 0000            | 1    | <b></b>      |       |            |      |          |              |              |         |          |          |      |      |      | €           | Ë  |

| xxxx            | 0001            | 2    | :            |       |            |      |          |              |              |         |          | i        |      |      |      | -==         | :: |

| xxxx            | 0010            | 3    |              | -#    | <b>i</b> - |      | 1.       | <b>:</b>     | <b>.</b>     | :       |          | ::       |      |      |      |             | ·· |

| xxxx            | 0011            | 4    |              | -     |            |      | ::::     | •            |              |         |          |          | :    |      |      | : <u></u> . | :: |

| xxxx            | 0100            | 5    | -==          | ::::- | :::::      |      | ::::·    |              |              | <u></u> |          | ::::     | ii.  |      |      |             | ŧ  |

| xxxx            | 0101            | 6    |              | 1     | ::::       |      | :        | <b>"</b>     | · <u>···</u> | <b></b> |          | <b>:</b> |      |      |      |             | i  |

| xxxx            | 0110            | 7    |              | i     |            |      |          |              | <u>.</u>     |         |          |          |      | =    | ij   | ‡           | ١. |

| xxxx            | 0111            | 8    |              | ::::  | <b>.</b>   | H    | :#:      | <u></u>      | <u></u>      | 1       | ₩        | :        |      |      |      |             | ij |

| xxxx            | 1000            | 9    | rii.         |       | ř          |      | ::::     |              | ::::         |         | <u>:</u> |          |      |      | ×    |             |    |

| xxxx            | 1001            | 10   |              | i     |            | M    | <b>.</b> |              | H            | ::::    |          | 7        | -    | I    | -    | 1           | :  |

| xxxx            | 1010            | 11   | : <u>:</u> . |       |            |      |          |              | •==          | Ĭ.      | ••••     | :‡:      | ##   |      |      |             |    |

| xxxx            | 1011            | 12   |              |       |            | ."   |          | <b>:::</b> : | <b>!:</b> :: |         |          |          | ::   |      |      | k:          |    |

| xxxx            | 1100            | 13   |              | ₩.:   | ::         |      | -::-     | ···          |              |         |          | :=       |      |      |      | 1           |    |

| xxxx            | 1101            | 14   | : <u></u> .  |       | †;·        |      | <b></b>  | <b>!</b>     |              |         |          |          |      |      |      |             | Ë  |

| xxxx            | 1110            | 15   |              | .≝.   |            |      | ٠        |              | ::::         |         |          | ::       | :    | : :  |      | <b>!</b> ": | Ė. |

| xxxx            | 1111            | 16   |              |       |            |      |          |              | •••••        |         |          |          |      |      |      | ::::        |    |

Fig.7 Character set 'S' in CGROM.

| lower<br>4 bits | upper<br>4 bits | 0000 | 0001     | 0010        | 0011     | 0100 | 0101 | 0110     | 0111       | 1000 | 1001       | 1010                                       | 1011 | 1100    | 1101 | 1110  | 1  |

|-----------------|-----------------|------|----------|-------------|----------|------|------|----------|------------|------|------------|--------------------------------------------|------|---------|------|-------|----|

| xxxx            | 0000            | 1    | -#       | <b>#</b> -  |          | •    |      | :: ::    |            |      |            |                                            |      |         |      | €     | Ë  |

| xxxx            | 0001            | 2    |          |             |          |      |      |          |            |      | ÷          | i                                          | 1    |         |      | -:::  | :  |

| xxxx            | 0010            | 3    |          |             |          |      | 1.   |          |            | #    |            | ::                                         |      |         |      |       | ŀ  |

| xxxx            | 0011            | 4    |          |             | 1        |      |      |          | ٠٠.        | ¥    |            |                                            |      |         | :    | £     | :  |

| xxxx            | 0100            | 5    |          | ::::-       |          |      |      | .i.      | ٠.         |      |            |                                            |      |         |      |       | -  |

| xxxx            | 0101            | 6    |          | 1.          | :::      |      |      |          | $\approx$  |      |            | #.:<br>::::::::::::::::::::::::::::::::::: |      |         |      | ===   |    |

| xxxx            | 0110            | 7    | -        | :           |          | •••• |      |          | ::::       |      |            |                                            |      |         | ¥    | #"    | ŧ. |

| xxxx            | 0111            | 8    | 1        | ::::        | <b>.</b> |      | Į.,  |          | :::        |      | W          | :                                          | ï    |         |      |       | ŧ. |

| xxxx            | 1000            | 9    |          |             | F        | #    |      | <b>.</b> | <b>:::</b> |      |            |                                            |      |         | ×    | ŀ     |    |

| xxxx            | 1001            | 10   |          | :           |          |      |      |          |            | ===  |            |                                            | •    |         | 1    | 1     | :  |

| xxxx            | 1010            | 11   | ≝.       |             |          |      |      |          | <b></b>    | Ĭ.   |            | :4::                                       | ::   |         | :::  |       | .: |

| xxxx            | 1011            | 12   | :::      |             |          | :::: |      |          |            |      | ===        |                                            | ::   |         |      |       |    |

| xxxx            | 1100            | 13   |          |             |          | -    |      | ░        |            |      |            | :                                          |      | <b></b> |      |       |    |

| xxxx            | 1101            | 14   | <u>.</u> |             | <b>.</b> |      |      |          |            |      |            |                                            |      |         |      |       | :  |

| xxxx            | 1110            | 15   |          | <u>::</u> . |          |      |      |          |            |      | <b>:::</b> | :::                                        | :    |         |      | l'''i | i  |

| xxxx            | 1111            | 16   |          | ::::        |          |      |      |          | *          |      |            |                                            | •    |         |      | ::::  |    |

Fig.8 Character set 'V' in CGROM.

### LCD controllers/drivers

### PCF2119x-2

|   |                           |    | racte<br>DRA |   |   |                            |   |   |                           |    | GRA<br>ddre |                                 |                                      |                                 |            |                  |                       |   | pat<br>M da  |           |                  |                                              |                                      | chara<br>CGF                    |                                      |                                 |     |

|---|---------------------------|----|--------------|---|---|----------------------------|---|---|---------------------------|----|-------------|---------------------------------|--------------------------------------|---------------------------------|------------|------------------|-----------------------|---|--------------|-----------|------------------|----------------------------------------------|--------------------------------------|---------------------------------|--------------------------------------|---------------------------------|-----|

|   | 6<br>high<br>ordo<br>bits | er | 4            | 3 | 0 | 1<br>ower<br>order<br>bits |   |   | 5<br>high<br>orde<br>bits | er | 3           | (                               | 1<br>owe<br>order<br>bits            |                                 | higher<br> | 4                | 3                     |   | lowe<br>orde | er<br>er_ |                  |                                              | 4                                    | 3                               | 2                                    | 1                               | C   |

| 0 | 0                         | 0  | 0            | 0 | 0 | 0                          | 0 | 0 | 0                         | 0  | 0           | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 |            | 0                | 0<br>0<br>0<br>0<br>0 |   |              |           | 0<br>0<br>0<br>0 | character pattern example 1  cursor position | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>0 | 1<br>0<br>0<br>1<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1<br>0<br>0      | 1<br>0<br>0<br>1<br>0<br>1<br>0 | (   |

| 0 | 0                         | 0  | 0            | 0 | 0 | 0                          | 1 | 0 | 0                         | 0  | 1           | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 |            | 0<br>0<br>0<br>0 | 0 0 0                 | C |              |           | 0<br>0<br>0<br>0 | character<br>pattern<br>example 2            | 1<br>0<br>1<br>0<br>1<br>0<br>0      | 0<br>1<br>1<br>0<br>1<br>0<br>0 | 0<br>0<br>1<br>1<br>1<br>1<br>1<br>0 | 0<br>1<br>1<br>0<br>1<br>0<br>0 | (   |

| 0 | 0                         | 0  | 0            | 0 | 0 | 1                          | 0 | 0 | 0                         | 1  | 0           | 0                               | 0                                    | 0                               |            |                  |                       |   |              |           |                  |                                              |                                      |                                 |                                      | МС                              | E9. |

Character code bits 0 to 3 correspond to CGRAM address bits 3 to 6.

CGRAM address bits 0 to 2 designate the character pattern line position. The 8th line is the cursor position and display is performed by logical OR with the cursor. Data in the 8th position will appear in the cursor position.

Character pattern column positions correspond to CGRAM data bits 0 to 4, as shown in Fig.6.

As shown in Figs 6 and 7, CGRAM character patterns are selected when character code bits 4 to 7 are all logic 0. CGRAM data = logic 1 corresponds to selection for display.

Only bits 0 to 5 of the CGRAM address are set by the 'set CGRAM address' command. Bit 6 can be set using the 'set DDRAM address' command in the valid address range or by using the auto-increment feature during CGRAM write. All bits 0 to 6 can be read using the 'read busy flag and address counter' command.

Fig.9 Relationship between CGRAM addresses, data and display patterns.

### LCD controllers/drivers

PCF2119x-2

### 7.17 Reset function

The PCF2119x must be reset externally when power is turned on. The reset executes a 'clear display', requiring 165 oscillator cycles. After the reset the chip has the state shown in Table 4.

Table 4 State after reset

| STEP | FUNCTION                                 | CONTROL BIT STATE                                                     | CONDITION                                               |

|------|------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------|

| 1    | clear display                            | •                                                                     |                                                         |

| 2    | entry mode set                           | I/D = 1                                                               | +1 (increment)                                          |

|      |                                          | S = 0                                                                 | no shift                                                |

| 3    | display control                          | D = 0                                                                 | display off                                             |

|      |                                          | C = 0                                                                 | cursor off                                              |

|      |                                          | B = 0                                                                 | cursor character blink off                              |

| 4    | function set                             | DL = 1                                                                | 8-bit interface                                         |

|      |                                          | M = 0                                                                 | 1-line display                                          |

|      |                                          | H = 0                                                                 | normal instruction set                                  |

|      |                                          | SL = 0                                                                | MUX 1 : 18 mode                                         |

| 5    | •                                        | AM; the Busy Flag (BF) indicates the lasts 2 ms; the chip may also be | , ,                                                     |

| 6    | icon control                             | IM, IB, DM = 000                                                      | icons, icon blink and direct mode disabled              |

| 7    | display/screen configuration             | L = 0; P = 0; Q = 0                                                   | default configurations                                  |

| 8    | V <sub>LCD</sub> temperature coefficient | TC1 = 0; TC2 = 0                                                      | default temperature coefficient                         |

| 9    | set V <sub>LCD</sub>                     | $V_A = 0$ ; $V_B = 0$ ( $V_{LCD}$ generator                           | off)                                                    |

| 10   | I <sup>2</sup> C-bus interface reset     | •                                                                     |                                                         |

| 11   | Set HVgen stages                         | S1, S0 = 10                                                           | HVgen set to 3 internal stages (4 * voltage multiplier) |

### LCD controllers/drivers

PCF2119x-2

#### 8 INSTRUCTIONS

Only two PCF2119x registers, the Instruction Register (IR) and the Data Register (DR) can be directly controlled by the MPU. Before internal operation, control information is stored temporarily in these registers, to allow interfacing to various types of MPUs which operate at different speeds or to allow interface to peripheral control ICs.

The PCF2119x operation is controlled by the instructions shown in Table 6 together with their execution time. Details are explained in subsequent sections.

Instructions are of 4 types, those that:

- Designate PCF2119x functions such as display format, data length, etc.

- 2. Set internal RAM addresses

- 3. Perform data transfer with internal RAM

- 4. Others.

In normal use, category 3 instructions are used most frequently. However, automatic incrementing by 1 (or decrementing by 1) of internal RAM addresses after each data write lessens the MPU program load. The display shift in particular can be performed concurrently with display data write, enabling the designer to develop systems in minimum time with maximum programming efficiency.

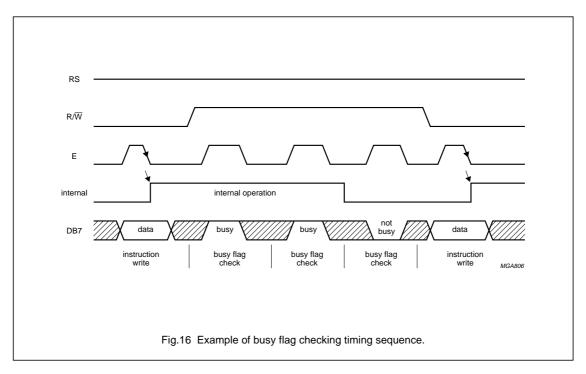

During internal operation, no instructions other than the 'read busy flag' and 'read address' instructions will be executed. Because the busy flag is set to a logic 1 while an instruction is being executed, check to ensure it is a logic 0 before sending the next instruction or wait for the maximum instruction execution time, as given in Table 6. An instruction sent while the busy flag is logic 1 will not be executed.

**Table 5** Instruction set for I<sup>2</sup>C-bus commands

|    |    | CO | NTRO | DL B | YTE |   |   |     |     | CC  | MMA | ND BY | TE  |     |     | I <sup>2</sup> C-BUS COMMANDS |

|----|----|----|------|------|-----|---|---|-----|-----|-----|-----|-------|-----|-----|-----|-------------------------------|

| Co | RS | 0  | 0    | 0    | 0   | 0 | 0 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2 | DB1 | DB0 | note 1                        |

### Note

1.  $R/\overline{W}$  is set together with the slave address.

Table 6

Instruction set with parallel bus commands; note 1

| r | Ċ | ٥ |  |

|---|---|---|--|

| Ċ | - | 5 |  |

| 7 | Ī |   |  |

|   |   |   |  |

| INSTRUCTION                              | RS | R/W | DB7 | DB6 | DB5                                                                                                                         | DB4 | DB3             | DB2 | DB1 | DB0                             | DESCRIPTION                                                                                                                                          | REQUIRED<br>CLOCK<br>CYCLES |

|------------------------------------------|----|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|-----|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| H = 0 or 1                               |    |     |     |     |                                                                                                                             |     |                 |     |     |                                 |                                                                                                                                                      |                             |

| NOP                                      | 0  | 0   | 0   | 0   | 0                                                                                                                           | 0   | 0               | 0   | 0   | 0                               | no operation                                                                                                                                         | 3                           |

| Function set                             | 0  | 0   | 0   | 0   | 1                                                                                                                           | DL  | 0               | М   | SL  | Н                               | sets interface Data Length (DL) and number of<br>display lines (M); single line/MUX 1 : 9 (SL),<br>extended instruction set control (H)              | 3                           |

| Read busy flag<br>and address<br>counter | 0  | 1   | BF  |     | A <sub>C</sub> reads the Busy Flag (BF) indicating internal operating is being performed and reads address counter contents |     | 0               |     |     |                                 |                                                                                                                                                      |                             |

| Read data                                | 1  | 1   |     |     | read data                                                                                                                   |     |                 |     |     | reads data from CGRAM or DDRAM  | 3                                                                                                                                                    |                             |

| Write data                               | 1  | 0   |     |     | write data                                                                                                                  |     |                 |     |     | writes data from CGRAM or DDRAM | 3                                                                                                                                                    |                             |

| H = 0                                    |    |     |     |     |                                                                                                                             |     |                 |     |     |                                 |                                                                                                                                                      |                             |

| Clear display                            | 0  | 0   | 0   | 0   | 0                                                                                                                           | 0   | 0               | 0   | 0   | 1                               | clears entire display and sets DDRAM address 0 in address counter                                                                                    | 165                         |

| Return home                              | 0  | 0   | 0   | 0   | 0                                                                                                                           | 0   | 0               | 0   | 1   | 0                               | sets DDRAM address 0 in address counter; also returns shifted display to original position; DDRAM contents remain unchanged                          | 3                           |

| Entry mode set                           | 0  | 0   | 0   | 0   | 0                                                                                                                           | 0   | 0               | 1   | I/D | S                               | sets cursor move direction and specifies shift of display; these operations are performed during data write and read                                 | 3                           |

| Display control                          | 0  | 0   | 0   | 0   | 0                                                                                                                           | 0   | 1               | D   | С   | В                               | sets entire display on/off (D), cursor on/off (C) and blink of cursor position character (B); D = 0 (display off) puts chip into the power-down mode | 3                           |

| Cursor/display shift                     | 0  | 0   | 0   | 0   | 0                                                                                                                           | 1   | S/C             | R/L | 0   | 0                               | moves cursor and shifts display without changing DDRAM contents                                                                                      | 3                           |

| Set CGRAM<br>address                     | 0  | 0   | 0   | 1   |                                                                                                                             |     | A               | CG  | •   |                                 | sets CGRAM address; bit 6 is to be set by the command 'set DDRAM address'; look at the description of the commands                                   | 3                           |

| Set DDRAM<br>address                     | 0  | 0   | 1   |     |                                                                                                                             |     | A <sub>DD</sub> |     |     |                                 | sets DDRAM address                                                                                                                                   | 3                           |

| INSTRUCTION           | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3  | DB2 | DB1 | DB0 | DESCRIPTION                                                             | REQUIRED<br>CLOCK<br>CYCLES |

|-----------------------|----|-----|-----|-----|-----|-----|------|-----|-----|-----|-------------------------------------------------------------------------|-----------------------------|

| H = 1                 |    |     |     |     |     |     |      |     |     |     |                                                                         |                             |

| Reserved              | 0  | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 0   | 1   | do not use                                                              | -                           |

| Screen configuration  | 0  | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 1   | L   | set screen configuration                                                | 3                           |

| Display configuration | 0  | 0   | 0   | 0   | 0   | 0   | 0    | 1   | Р   | Q   | set display configuration                                               | 3                           |

| Icon control          | 0  | 0   | 0   | 0   | 0   | 0   | 1    | IM  | IB  | DM  | set icon mode (IM), icon blink (IB), direct mode(DM)                    | 3                           |

| Temperature control   | 0  | 0   | 0   | 0   | 0   | 1   | 0    | 0   | TC1 | TC2 | set temperature coefficient (TCx)                                       | 3                           |

| Set HVgen stages      | 0  | 0   | 0   | 1   | 0   | 0   | 0    | 0   | S1  | S0  | set internal HVgen stages (S1,S0 = 11 not allowed)                      | 3                           |

| Set V <sub>LCD</sub>  | 0  | 0   | 1   | V   |     |     | volt | age |     |     | store V <sub>LCD</sub> in register V <sub>A</sub> or V <sub>B</sub> (V) | 3                           |

### Note

1. X = don't care.

# LCD controllers/drivers

Table 7 Explanations of symbols used in Table 6

| DIT                               | STA                                                                                                                 | STATE                                                                                         |  |  |  |  |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| BIT                               | LOGIC 0                                                                                                             | LOGIC 1                                                                                       |  |  |  |  |  |  |  |  |  |

| I/D                               | decrement                                                                                                           | increment                                                                                     |  |  |  |  |  |  |  |  |  |

| S                                 | display freeze                                                                                                      | display shift                                                                                 |  |  |  |  |  |  |  |  |  |

| D                                 | display off                                                                                                         | display on                                                                                    |  |  |  |  |  |  |  |  |  |

| С                                 | cursor off                                                                                                          | cursor on                                                                                     |  |  |  |  |  |  |  |  |  |

| В                                 | cursor character blink off: character at cursor position does not blink                                             | cursor character blink on: character at cursor position blinks                                |  |  |  |  |  |  |  |  |  |

| S/C                               | cursor move                                                                                                         | display shift                                                                                 |  |  |  |  |  |  |  |  |  |

| R/L                               | left shift                                                                                                          | right shift                                                                                   |  |  |  |  |  |  |  |  |  |

| DL                                | 4 bits                                                                                                              | 8 bits                                                                                        |  |  |  |  |  |  |  |  |  |

| Н                                 | use basic instruction set                                                                                           | use extended instruction set                                                                  |  |  |  |  |  |  |  |  |  |

| L (no impact, if M = 1 or SL = 1) | left/right screen: standard connection (as in PCF2114)                                                              | left/right screen: mirrored connection (as in PCF2116)                                        |  |  |  |  |  |  |  |  |  |

|                                   | 1st 16 characters of 32: columns are from 1 to 80                                                                   | 1st 16 characters of 32: columns are from 1 to 80                                             |  |  |  |  |  |  |  |  |  |

|                                   | 2nd 16 characters of 32: columns are from 1 to 80                                                                   | 2nd 16 characters of 32: columns are from 80 to 1                                             |  |  |  |  |  |  |  |  |  |

| Р                                 | column data: left to right (as in PCF2116); column data is displayed from 1 to 80                                   | column data: right to left; column data is displayed from 80 to 1                             |  |  |  |  |  |  |  |  |  |

| Q                                 | row data: top to bottom (as in PCF2116); row data is<br>displayed from 1 to 16 and icon row data is in<br>17 and 18 | row data: bottom to top; row data is displayed from 16 to 1 and icon row data is in 18 and 17 |  |  |  |  |  |  |  |  |  |

| IM                                | character mode; full display                                                                                        | icon mode; only icons displayed                                                               |  |  |  |  |  |  |  |  |  |

| IB                                | icon blink disabled                                                                                                 | icon blink enabled                                                                            |  |  |  |  |  |  |  |  |  |

| DM                                | direct mode disabled                                                                                                | direct mode enabled                                                                           |  |  |  |  |  |  |  |  |  |

| V                                 | set V <sub>A</sub>                                                                                                  | set V <sub>B</sub>                                                                            |  |  |  |  |  |  |  |  |  |

| M (no impact, if SL = 1)          | 1-line by 32 display                                                                                                | 2-line by 16 display                                                                          |  |  |  |  |  |  |  |  |  |

| SL                                | MUX 1: 18 (1 × 32 or 2 × 16 character display)                                                                      | MUX 1:9 (1 × 16 character display)                                                            |  |  |  |  |  |  |  |  |  |

| C <sub>0</sub>                    | last control byte; see Table 5                                                                                      | another control byte follows after data/command                                               |  |  |  |  |  |  |  |  |  |

Table 8 Explanation of TC1 and TC2 used in Table 6

| TC1 | TC2 | DESCRIPTION                                                                  |

|-----|-----|------------------------------------------------------------------------------|

| 0   | 0   | V <sub>LCD</sub> temperature coefficient 0                                   |

| 1   | 0   | V <sub>LCD</sub> temperature coefficient 1                                   |

| 0   | 1   | V <sub>LCD</sub> temperature coefficient 2                                   |

| 1   | 1   | V <sub>LCD</sub> temperature coefficient 3; for ranges for TC see Chapter 13 |

Table 9 Explanation of S1 and S0 used in Table 6

| S1 | S0 | DESCRIPTION                                             |

|----|----|---------------------------------------------------------|

| 0  | 0  | set internal HVgen stages to 1 (2 * voltage multiplier) |

| 0  | 1  | set internal HVgen stages to 2 (3 * voltage multiplier) |

| 1  | 0  | set internal HVgen stages to 3 (4 * voltage multiplier) |

| 1  | 1  | do not use                                              |

### PCF2119x-2

### 8.1 Clear display

'Clear display' writes character code 20H into all DDRAM addresses (the character pattern for character code 20H must be a blank pattern), sets the DDRAM address counter to logic 0 and returns the display to its original position, if it was shifted. Thus, the display disappears and the cursor or blink position goes to the left edge of the display. Sets entry mode I/D = 1 (increment mode). S of entry mode does not change.

The instruction 'clear display' requires extra execution time. This may be allowed by checking the Busy Flag (BF) or by waiting until the 165 clock cycles have elapsed. The latter must be applied where no read-back options are foreseen, as in some Chip-On-Glass (COG) applications.

### 8.2 Return home

'Return home' sets the DDRAM address counter to logic 0 and returns the display to its original position if it was shifted. DDRAM contents do not change. The cursor or blink position goes to the left of the first display line. I/D and S of entry mode do not change.

### 8.3 Entry mode set

### 8.3.1 I/D

When I/D = 1 (0) the DDRAM or CGRAM address increments (decrements) by 1 when data is written into or read from the DDRAM or CGRAM. The cursor or blink position moves to the right when incremented and to the left when decremented. The cursor underline and cursor character blink are inhibited when the CGRAM is accessed.

### 8.3.2

When S = 1, the entire display shifts either to the right (I/D=0) or to the left (I/D=1) during a DDRAM write. Thus it appears as if the cursor stands still and the display moves. The display does not shift when reading from the DDRAM, or when writing to or reading from the CGRAM. When S = 0, the display does not shift.

PCF2119x-2

#### 8.4 Display control (and partial power-down mode)

#### 8.4.1 D

The display is on when D=1 and off when D=0. Display data in the DDRAM is not affected and can be displayed immediately by setting D to a logic 1.

When the display is off (D = 0) the chip is in partial power-down mode:

- The LCD outputs are connected to V<sub>SS</sub>

- The LCD generator and bias generator are turned off.

Three oscillator cycles are required after sending the 'display off' instruction to ensure all outputs are at  $V_{SS}$ , afterwards OSC can be stopped. If the oscillator is running during partial power-down mode ('display off') the chip can still execute instructions. Even lower current consumption is obtained by inhibiting the oscillator (OSC =  $V_{SS}$ ).

To ensure  $I_{DD}$  <1  $\mu A$ , the parallel bus pads DB7 to DB0 should be connected to  $V_{DD};$  RS and  $R/\overline{W}$  to  $V_{DD}$  or left open-circuit and PD to  $V_{DD}.$  Recovery from power-down mode: PD back to logic 0, if necessary OSC back to  $V_{DD}$  and send a 'display control' instruction with D = 1.

### 8.4.2 C

The cursor is displayed when C=1 and inhibited when C=0. Even if the cursor disappears, the display functions I/D, etc. remain in operation during display data write. The cursor is displayed using 5 dots in the 8th line (see Fig.5).

#### 8.4.3 B

The character indicated by the cursor blinks when B=1. The cursor character blink is displayed by switching between display characters and all dots on with a period of

approximately 1 second, with

$$f_{blink} = \frac{f_{OSC}}{52224}$$

The cursor underline and the cursor character blink can be set to display simultaneously.

#### 8.5 Cursor or display shift

'Cursor/display shift' moves the cursor position or the display to the right or left without writing or reading display data. This function is used to correct a character or move the cursor through the display. In 2-line displays, the cursor moves to the next line when it passes the last position (40) of the line. When the displayed data is shifted repeatedly all lines shift at the same time; displayed characters do not shift into the next line.

The Address Counter (AC) content does not change if the only action performed is shift display, but increments or decrements with the 'cursor shift'.

#### 8.6 Function set

#### 8.6.1 DL (PARALLEL MODE ONLY)

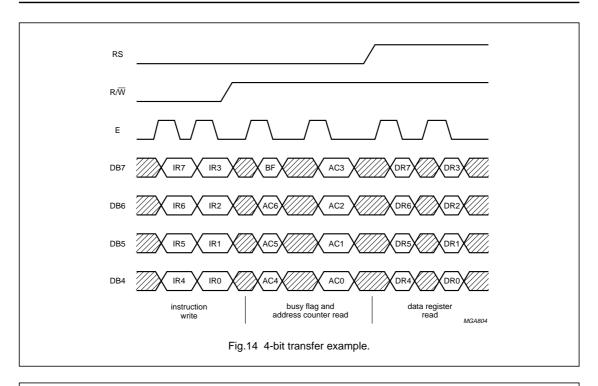

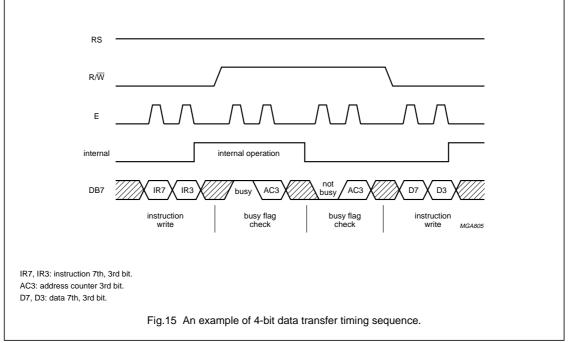

Sets interface data width. Data is sent or received in bytes (DB7 to DB0) when DL = 1 or in two nibbles (DB7 to DB4) when DL = 0. When 4-bit width is selected, data is transmitted in two cycles using the parallel bus. In a 4-bit application DB3 to DB0 should be left open-circuit (internal pull-ups). Hence in the first 'function set' instruction after power-on M, SL and H are set to logic 1. A second 'function set' must then be sent (2 nibbles) to set M, SL and H to their required values.

'Function set' from the I<sup>2</sup>C-bus interface sets the DL bit to logic 1.

#### 8.6.2 M

Selects either 1-line by 32 display (M = 0) or 2-line by 16 display (M = 1).

#### 8.6.3 SL

Selects MUX 1: 9, 1-line by 16 display (independent of M and L). Only rows 1 to 8 and 17 are to be used. All other rows must be left open-circuit. The DDRAM map is the same as in the 2-line by 16 display mode, however, the second line is not displayable.

PCF2119x-2

#### 8.6.4 H

When H = 0 the chip can be programmed via the standard 11 instruction codes used in the PCF2116 and other LCD controllers

When H = 1 the extended range of instructions will be used. These are mainly for controlling the display configuration and the icons.

#### 8.7 Set CGRAM address

'Set CGRAM address' sets bits 5 to 0 of the CGRAM address  $A_{CG}$  into the address counter (binary A5 to A0). Data can then be written to or read from the CGRAM.

Attention: the CGRAM address uses the same address register as the DDRAM address and consists of 7 bits (binary A6 to A0). With the 'set CGRAM address' command, only bits 5 to 0 are set. Bit 6 can be set using the 'set DDRAM address' command first, or by using the auto-increment feature during CGRAM write. All bits 6 to 0 can be read using the 'read busy flag' and 'read address' command.

When writing to the lower part of the CGRAM, ensure that bit 6 of the address is not set (e.g. by an earlier DDRAM write or read action).

### 8.8 Set DDRAM address

'Set DDRAM address' sets the DDRAM address  $A_{DD}$  into the address counter (binary A6 to A0). Data can then be written to or read from the DDRAM.

### 8.9 Read busy flag and read address

'Read busy flag' and 'read address' read the Busy Flag (BF) and Address Counter (AC). BF = 1 indicates that an internal operation is in progress. The next instruction will not be executed until BF = 0. It is recommended that the BF status is checked before the next write operation is executed.

At the same time, the value of the address counter expressed in binary A6 to A0 is read out. The address counter is used by both CGRAM and DDRAM, and its value is determined by the previous instruction.

### 8.10 Write data to CGRAM or DDRAM

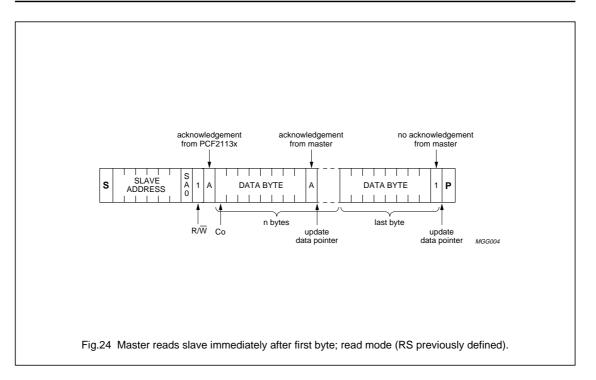

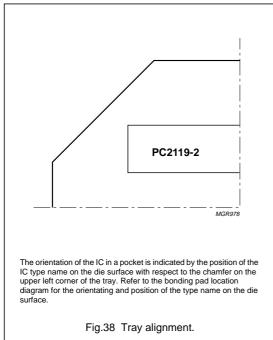

'Write data' writes binary 8-bit data D7 to D0 to the CGRAM or the DDRAM.