# ST20P64

**PRELIMINARY**

# 8 BIT Microcontroller with 64K bytes PROM(OTP)

Notice: Sitronix Technology Corp. reserves the right to change the contents in this document without prior notice. This is not a final specification. Some parameters are subject to change.

## 1. FEATURES

- 8-bit static pipeline CPU

- ROM: 64K x 8-bit PROM(OTP)

- RAM: 2432 x 8-bit

- Stack: Up to 128-level deep

- Operation voltage:

- DC-DC Converter Enable: 2.7V ~ 3.6V DC-DC Converter Disable: 2.7V ~ 5.5V

- Built-in double DC-DC voltage converter for LCD driver

- I/O ports

- 24 CMOS bidirectional bit programmable I/O pins, sixteen (Port-B/C) are shared with LCD drives

- 8 open drain output pins are shared with LCD drives

- 2 CMOS output pins are shared with PSG drives

- Bit programmable pull-up for input pins

- Hardware de-bounce option for Port-A

- Low voltage detector

- Timer/Counter:

- Two 8-bit timer/16-bit event counter

- One 8-bit Base timer

- 6 hardware interrupts with dedicated exception vectors

- External interrupt (edge triggered)

- Timer0 interrupt

- Timer1 interrupt

- Base timer interrupt

- Port-A[7~0] interrupt (transition triggered)

- DAC reload interrupt

- Dual clock sources with warm-up timer

- Low frequency crystal oscillator

|                |   | <br> | <br> | 3    | 2768 | Hz |

|----------------|---|------|------|------|------|----|

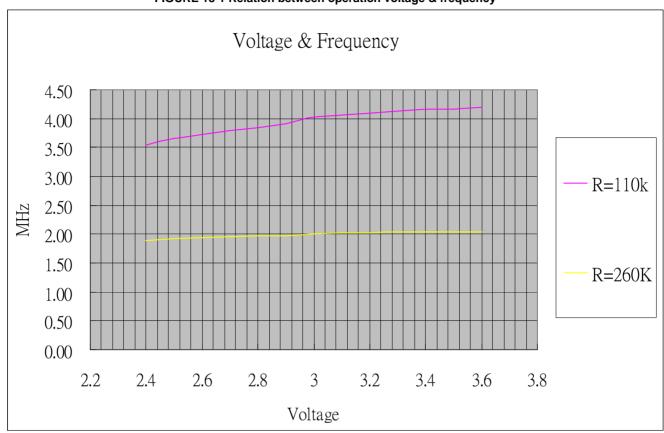

| - RC oscillato | r | <br> | <br> | 500K | ~ 4M | Hz |

| CPU clock      |   | <br> | <br> | 250K | ~ 2M | Hz |

- LCD controller/driver

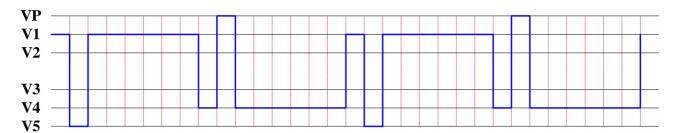

- Resolution: 32x8 ~ 48x16, maximum 768 dots

- Two clock source options: RC and resonator oscillator

- Internal bias resistors (1/5 bias/1/4 bias) with 16-level driving strength control

- Up to 16-level contrast control

- Keyboard scan function supported on 16 shared segment drives

- Programmable sound generator (PSG)

- Two channels with three playing modes

- Tone/noise generator

- 16-level volume control

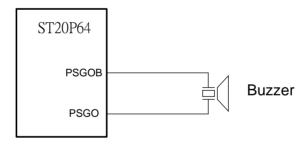

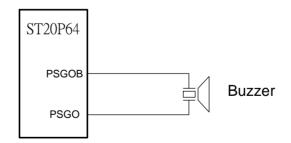

- Dedicated outputs for directly connection to buzzer

- PWM DAC: Three modes up to 8-bit resolution

- Three power down modes:

- WAI0 mode

- WAI1 mode

- STP mode

# 2. GENERAL DESCRIPTION

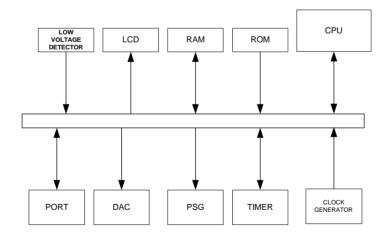

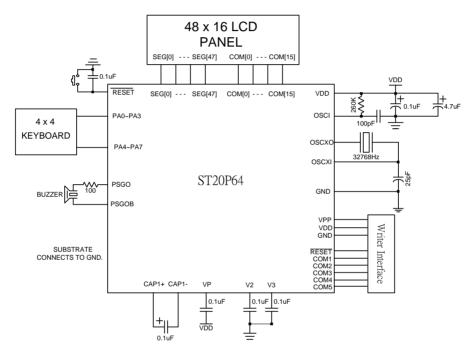

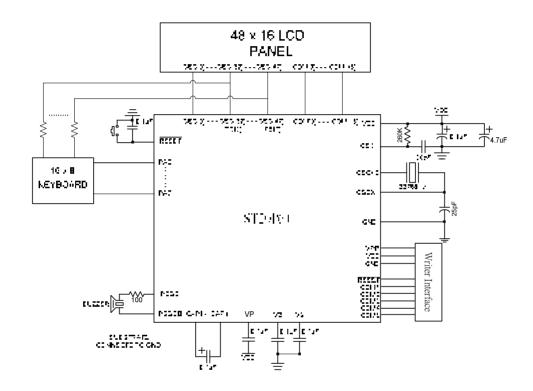

The ST20P64 is a 8-bit intergrated microcontroller designed with CMOS silicon gate technology. This single chip microcontroller is useful for translator, databank and other consumer applications. It integrates with SRAM, Programming

ROM(OTP), LCD controller/driver, DC-DC voltage converter, I/O ports, timers, PSG and PWM DAC. This chip also builds in dual oscillators for the chip performance enhancement.

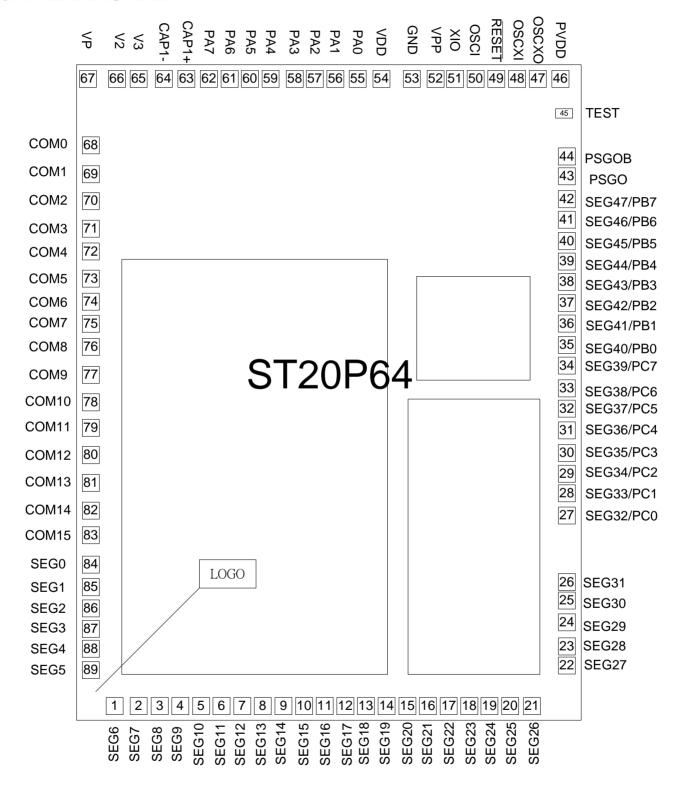

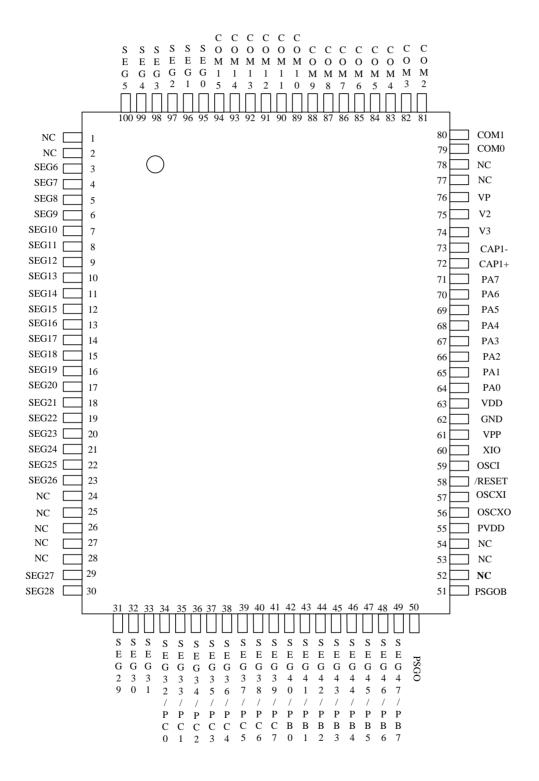

# 3. PAD DIAGRAM

# 4. PAD CENTER COORDINATES

■ Chip size: 2670µm X3470 µm

■ Coordinate: Pad center (µm)

■ Origin: Chip center

■ Origin: Chip center

■ Pad pitch: 110µm, 120µm

■ Substrate connection: GND

Unit: µm

| PAD NO. | NAME      | Х       | Υ       | PAD NO. | NAME      | Х      | Υ      |

|---------|-----------|---------|---------|---------|-----------|--------|--------|

| 1       | SEG6      | -1133.5 | -1660   | 31      | SEG36/PC4 | 1260   | -200.5 |

| 2       | SEG7      | -1006.6 | -1660   | 32      | SEG37/PC5 | 1260   | -86.1  |

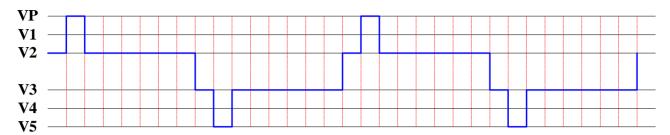

| 3       | SEG8      | -894.9  | -1660   | 33      | SEG38/PC6 | 1260   | 22.2   |

| 4       | SEG9      | -785.9  | -1660   | 34      | SEG39/PC7 | 1260   | 142.4  |

| 5       | SEG10     | -676.1  | -1660   | 35      | SEG40/PB0 | 1260   | 251.6  |

| 6       | SEG11     | -567.8  | -1660   | 36      | SEG41/PB1 | 1260   | 364.5  |

| 7       | SEG12     | -458.2  | -1660   | 37      | SEG42/PB2 | 1260   | 473.6  |

| 8       | SEG13     | -349.8  | -1660   | 38      | SEG43/PB3 | 1260   | 585.1  |

| 9       | SEG14     | -239.9  | -1660   | 39      | SEG44/PB4 | 1260   | 693.2  |

| 10      | SEG15     | -130.8  | -1660   | 40      | SEG45/PB5 | 1260   | 801.8  |

| 11      | SEG16     | -21.4   | -1660   | 41      | SEG46/PB6 | 1260   | 913.9  |

| 12      | SEG17     | 87.4    | -1660   | 42      | SEG47/PB7 | 1260   | 1023.9 |

| 13      | SEG18     | 196.4   | -1660   | 43      | PSGO      | 1260   | 1144.5 |

| 14      | SEG19     | 305.9   | -1660   | 44      | PSGOB     | 1260   | 1249.3 |

| 15      | SEG20     | 415.8   | -1660   | 45      | TEST      | 1256.1 | 1477.4 |

| 16      | SEG21     | 524.4   | -1660   | 46      | PVDD      | 1225.6 | 1660   |

| 17      | SEG22     | 634.7   | -1660   | 47      | oscxo     | 1106.6 | 1660   |

| 18      | SEG23     | 743.3   | -1660   | 48      | OSCXI     | 996.6  | 1660   |

| 19      | SEG24     | 849.8   | -1660   | 49      | RESET     | 886.3  | 1660   |

| 20      | SEG25     | 960.1   | -1660   | 50      | OSCI      | 777.1  | 1660   |

| 21      | SEG26     | 1075.1  | -1660   | 51      | XIO       | 668.1  | 1660   |

| 22      | SEG27     | 1260    | -1445.2 | 52      | VPP       | 565    | 1660   |

| 23      | SEG28     | 1260    | -1343.9 | 53      | GND       | 439.8  | 1660   |

| 24      | SEG29     | 1260    | -1216.4 | 54      | VDD       | 278.5  | 1660   |

| 25      | SEG30     | 1260    | -1101.3 | 55      | PA0       | 152.9  | 1660   |

| 26      | SEG31     | 1260    | -1003.7 | 56      | PA1       | 34.7   | 1660   |

| 27      | SEG32/PC0 | 1260    | -651.2  | 57      | PA2       | -74.3  | 1660   |

| 28      | SEG33/PC1 | 1260    | -533.2  | 58      | PA3       | -179.9 | 1660   |

| 29      | SEG34/PC2 | 1260    | -430.5  | 59      | PA4       | -308.2 | 1660   |

| 30      | SEG35/PC3 | 1260    | -320.5  | 60      | PA5       | -417.8 | 1660   |

| PAD NO. | NAME  | Х       | Υ      | PAD NO. | NAME  | Х     | Υ       |

|---------|-------|---------|--------|---------|-------|-------|---------|

| 61      | PA6   | -524.6  | 1660   | 76      | COM8  | -1260 | 241.4   |

| 62      | PA7   | -634.7  | 1660   | 77      | СОМ9  | -1260 | 93      |

| 63      | CAP1+ | -753.5  | 1660   | 78      | COM10 | -1260 | -51.6   |

| 64      | CAP1- | -873.3  | 1660   | 79      | COM11 | -1260 | -187.9  |

| 65      | V3    | -1006.4 | 1660   |         | COM12 | -1260 | -331.2  |

| 66      | V2    | -1121.4 | 1660   |         | COM13 | -1260 | -479.2  |

| 67      | VP    | -1274.9 | 1660   |         | COM14 | -1260 | -625.7  |

| 68      | СОМО  | -1260   | 1307.9 | 83      | COM15 | -1260 | -755.6  |

| 69      | COM1  | -1260   | 1155.4 | 84      | SEG0  | -1260 | -911.3  |

| 70      | COM2  | -1260   | 1013.4 | 85      | SEG1  | -1260 | -1030.3 |

| 71      | СОМЗ  | -1260   | 866.3  | 86      | SEG2  | -1260 | -1142.7 |

| 72      | COM4  | -1260   | 746.1  | 87      | SEG3  | -1260 | -1251.8 |

| 73      | COM5  | -1260   | 601.9  |         | SEG4  | -1260 | -1357   |

| 74      | COM6  | -1260   | 480.4  | 89      | SEG5  | -1260 | -1469.5 |

| 75      | COM7  | -1260   | 363.2  |         |       |       |         |

# **5. BLOCK DIAGRAM**

# 6. PAD DESCRIPTION

| Pin No.        | Designation                          | I/O           | Description                                                                                                                                                                        |

|----------------|--------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70~73          | COM2/SCK COM3/SS COM4/MOSI COM5/MISO | I/O           | LCD common drive output pins, drives 2~5 SPI interface for OTP programming.                                                                                                        |

| 68, 69, 74, 75 | COM0,1, 6, 7                         | 0             | LCD common drive output pins, drives 0, 1, 6, 7                                                                                                                                    |

| 76~83          | COM8~15                              | 0             | LCD common drive output pins, drives 8~15 Common open drain output port.                                                                                                           |

| 84~89, 1~26    | SEG0~31                              | 0             | LCD segment drive output pins, drives 0~31                                                                                                                                         |

| 55             | PA0 / INTX                           | I/O<br>I<br>I | <ul> <li>Port-A bit programmable I/O</li> <li>Edge-trigger Interrupt.</li> <li>Transition-trigger Interrupt</li> <li>Programmable Timer1 clock source</li> </ul>                   |

| 56~62          | PA1~7                                | I/O<br>I      | - Port-A bit programmable I/O - Transition-trigger Interrupt                                                                                                                       |

| 35~42          | SEG40/PB0~<br>SEG47/PB7              | I/O<br>O      | - Port-B bit programmable I/O - LCD segment drives 40~47                                                                                                                           |

| 27~34          | SEG32/PC0~<br>SEG39/PC7              | I/O<br>O      | - Port-C bit programmable I/O - LCD segment drives 32~39                                                                                                                           |

| 46             | PVDD                                 | Р             | PSG Power supply pin                                                                                                                                                               |

| 44, 43         | PSGOB,PSGO                           | 0             | PSG/ PWM DAC Outputs                                                                                                                                                               |

| 47, 48         | OSCXO, OSCXI                         | I/O           | Low frequency crystal oscillator I/O pins. Connect to external 32768 Hz crystal.                                                                                                   |

| 49             | RESET                                | I             | Reset signal input (low active)                                                                                                                                                    |

| 50             | OSCI                                 | I<br>I        | <ul> <li>RC oscillator input pin. Connected to external resistor</li> <li>High frequency crystal/resonator oscillator input pin. Connect to external crystal/resonator.</li> </ul> |

| 51             | XIO                                  | 0             | - NC     - High frequency crystal/resonator oscillator output pin. Connect to external crystal/resonator.                                                                          |

| 53             | GND                                  | Р             | Ground pin                                                                                                                                                                         |

| 54             | VDD                                  | Р             | Power supply pin                                                                                                                                                                   |

| 63             | CAP1+                                | I/O           | Connect to booster capacitor positive(+) terminal                                                                                                                                  |

| 64             | CAP1-                                | I/O           | Connect to booster capacitor negative(-) terminal                                                                                                                                  |

| 66, 65         | V2, V3                               | Р             | Multi-level power supply for the liquid crystal drive                                                                                                                              |

| 67             | VP                                   | 0             | Voltage output of booster circuit                                                                                                                                                  |

| 45             | TEST                                 | I             | Chip test function. Leave it open.                                                                                                                                                 |

Note: I = input, O = output, I/O = input/output, P = power.

## 7. CPU

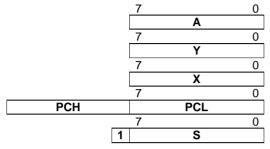

#### **Register Model**

#### Accumulator (A)

The Accumulator is a general-purpose 8-bit register that stores the results of most arithmetic and logic operations. In addition, the accumulator usually contains one of the two data which used in these operations.

#### Index Registers (X,Y)

There are two 8-bit Index Registers (X and Y), which may be used to count program steps or to provide and index value to be used in generating an effective address. When executing an instruction, which specifies indexed addressing, the CPU fetches the OP code and the base address, and modifies the address by adding the index register to it prior to performing the desired operation. Pre or post-indexing of indirect addresses is possible.

#### Stack Pointer (S)

The Stack Pointer is an 8-bit register, which is used to control the addressing of the variable-length stack. It's range from 100H to 1FFH total for 256 bytes (128 level deep). The stack pointer is automatically increment and decrement under control of the microprocessor to perform stack manipulations under

Accumulator A

Index Register Y

Index Register X

Program Counter PC

Stack Pointer S

direction of either the program or interrupts (IRQ). The stack allows simple implementation of nested subroutines and multiple level interrupts. The stack pointer is initialized by the user's software.

#### **Program Counter (PC)**

The 16-bit Program Counter register provides the address, which step the microprocessor through sequential program instructions. Each time the microprocessor fetches and instruction from program memory, the lower byte of the program counter (PCL) is placed on the low-order bits of the address bus and the higher byte of the program counter (PCH) is placed on the high-order 8 bits. The counter is increment each time an instruction or data is fetched from program memory.

#### Status Register (P)

The 8-bit Processor Status Register contains seven status flags. Some of these flags are controlled by program; others may be controlled both by the program and the CPU. The instruction set contains a member of conditional branch instructions that are designed to allow testing of these flags. Refer to TABLE 7-1

TABLE 7-1 Status Register (P)

| Bit 7 | Bit 6                    | Bit 5               | Bit 4 | Bit 3                 | Bit 2              | Bit 1     | Bit 0 |  |  |

|-------|--------------------------|---------------------|-------|-----------------------|--------------------|-----------|-------|--|--|

| N     | V                        | 1                   | В     | D                     | I                  | Z         | С     |  |  |

| Bit 7 | : N: Signed flag         | by arithmetic       |       | Bit 3:                | D: Decimal me      | ode flag  |       |  |  |

| 1 =   | Negative                 |                     |       | 1 = 0                 | Decimal mode       |           |       |  |  |

| 0 =   | Positive                 |                     |       | 0 = E                 | Binary mode        |           |       |  |  |

| Bit 6 | : V: Overflow o          | f signed Arithmetic | flag  | Bit 2:                | : I: Interrupt dis | able flag |       |  |  |

| 1 =   | Negative                 |                     |       | 1 = Interrupt disable |                    |           |       |  |  |

| 0 =   | Positive                 |                     |       | 0 = Interrupt enable  |                    |           |       |  |  |

|       |                          |                     |       | Bit 1: Z: Zero flag   |                    |           |       |  |  |

|       |                          |                     |       | 1 = Zero              |                    |           |       |  |  |

|       |                          |                     |       | 0 = N                 | lon zero           |           |       |  |  |

| Bit 4 | : B:BRK interr           | upt flag            |       | Bit 0: C: Carry flag  |                    |           |       |  |  |

| 1 =   | BRK interrupt occu       | ır                  |       | 1 = Carry             |                    |           |       |  |  |

| 0 =   | Non <b>BRK</b> interrupt | occur               |       | 0 = Non carry         |                    |           |       |  |  |

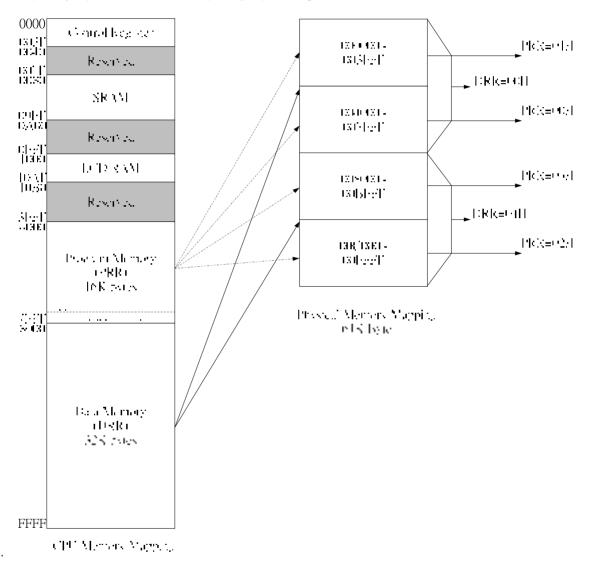

# 8. MEMORY CONFIGURATION

# 8.1 Memory map

ST20P64 builds in 64K bytes PROM and 2432 bytes RAM. The internal ROM can be used as data memory or program memory. PRR is the Program ROM Bank Register and DRR is the Data ROM Bank Register. The logical program ROM address is from \$4000 to \$7FFF(16K bytes), and \$8000 to \$FFFF (32K bytes) is for logical data ROM address.

# 8.2 **ROM**

### 8.2.1 Bank Description

Setting corresponding value to register PRR (program memory) or DRR (data memory) when user wants uses different memory bank.

FIGURE 8-1 ROM Bank Selection Registers (\$31~\$32)

|         |          |     |      |      |      |      | (+ +/ |      |      |      |

|---------|----------|-----|------|------|------|------|-------|------|------|------|

| Address | Register | R/W | Bit7 | Bit6 | Bit5 | Bit4 | Bit3  | Bit2 | Bit1 | Bit0 |

| PRR     | \$31     | RW  | -    | -    | -    | -    | -     | -    | PRR1 | PRR0 |

| DRR     | \$32     | RW  | -    | -    | -    | -    | -     | -    | -    | DRR0 |

# 8.3 **RAM**

Internal static RAM is for control registers, data RAM, stack RAM and the LCD frame buffer.

#### 8.3.1 Control Registers

| Address      | Name  | R/W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0         | Default    |

|--------------|-------|-----|---------|---------|---------|---------|----------|----------|---------|---------------|------------|

| \$000        | PA    | R/W | PA[7]   | PA[6]   | PA[5]   | PA[4]   | PA[3]    | PA[2]    | PA[1]   | PA[0]         | 1111 1111  |

| \$001        | РВ    | R/W | PB[7]   | PB[6]   | PB[5]   | PB[4]   | PB[3]    | PB[2]    | PB[1]   | PB[0]         | 1111 1111  |

| \$002        | PC    | R/W | PC[7]   | PC[6]   | PC[5]   | PC[4]   | PC[3]    | PC[2]    | PC[1]   | PC[0]         | 1111 1111  |

| \$008        | PCA   | R/W | PCA[7]  | PCA[6]  | PCA[5]  | PCA[4]  | PCA[3]   | PCA[2]   | PCA[1]  | PCA[0]        | 0000 0000  |

| \$009        | PCB   | R/W | PCB[7]  | PCB[6]  | PCB[5]  | PCB[4]  | PCB[3]   | PCB[2]   | PCB[1]  | PCB[0]        | 0000 0000  |

| \$00A        | PCC   | R/W | PCC[7]  | PCC[6]  | PCC[5]  | PCC[4]  | PCC[3]   | PCC[2]   | PCC[1]  | PCC[0]        | 0000 0000  |

| \$00E        | PAK   | R/W | PAK[7]  | PAK[6]  | PAK[5]  | PAK[4]  | PAK[3]   | PAK[2]   | PAK[1]  | PAK[0]        | 0000 0000  |

| \$00F        | PMCR  | R/W | PULL    | PDBN    | INTEG   | -       | TEST     | -        | -       | -             | 100 - 0    |

| \$010        | PSG0L | R/W | PSG0[7] | PSG0[6] | PSG0[5] | PSG0[4] | PSG0[3]  | PSG0[2]  | PSG0[1] | PSG0[0]       | 0000 0000  |

| \$011        | PSG0H | R/W | -       | -       | -       | -       | PSG0[11] | PSG0[10] | PSG0[9] | PSG0[8]       | 0000       |

| \$012        | PSG1L | R/W | PSG1[7] | PSG1[6] | PSG1[5] | PSG1[4] | PSG1[3]  | PSG1[2]  | PSG1[1] | PSG1[0]       | 0000 0000  |

| \$013        | PSG1H | R/W | -       | -       | -       | -       | PSG1[11] | PSG1[10] | PSG1[9] | PSG1[8]       | 0000       |

| \$014        | DAC   | R/W | DAC[7]  | DAC[6]  | DAC[5]  | DAC[4]  | DAC[3]   | DAC[2]   | DAC[1]  | DAC[0]        | 0000 0000  |

| \$015        | PSGC2 | R/W | -       | •       | •       | •       | PSGOD    | PSGOBD   | PSGOE   | <b>PSGOBE</b> | 1111       |

| \$016        | PSGC  | R/W | -       | PCK[2]  | PCK[1]  | PCK[0]  | PRBS     | C1EN     | C0EN    | DACE=0        | -000 0000  |

| \$010        | rage  | R/W | -       | PCK[2]  | PCK[1]  | PCK[0]  | DMD[1]   | DMD[0]   | INH     | DACE=1        | -000 0000  |

| \$017        | VOL   | R/W | VOL1[3] | VOL1[2] | VOL1[1] | VOL1[0] | VOL0[3]  | VOL0[2]  | VOL0[1] | VOL0[0]       | 0000 0000  |

| \$021        | BTM   | R/W | -       | -       | -       | -       | BTM[3]   | BTM[2]   | BTM[1]  | BTM[0]        | 0000       |

| \$023        | PRS   | R   | PRS[7]  | PRS[6]  | PRS[5]  | PRS[4]  | PRS[3]   | PRS[2]   | PRS[1]  | PRS[0]        | 0000 0000  |

| <b>\$023</b> | 1110  | W   | SRES    | SENA    | SENT    | -       | -        | -        | -       | -             | 000        |

| \$024        | T0M   | R/W | -       | -       | T0M[5]  | T0M[4]  | -        | T0M[2]   | T0M[1]  | T0M[0]        | 00 -000    |

| \$025        | T0C   | R/W | T0C[7]  | T0C[6]  | T0C[5]  | T0C[4]  | T0C[3]   | T0C[2]   | T0C[1]  | T0C[0]        | 0000 0000  |

| \$026        | T1M   | R/W | -       | -       | -       | T1M[4]  | T1M[3]   | T1M[2]   | T1M[1]  | T1M[0]        | 0 0000     |

| \$027        | T1C   | R/W | T1C[7]  | T1C[6]  | T1C[5]  | T1C[4]  | T1C[3]   | T1C[2]   | T1C[1]  | T1C[0]        | 0000 0000  |

| \$030        | SYS   | R/W | XSEL    | OSTP    | XSTP    | TEST    | WSKP     | WAIT     | -       | LVDET         | 0000 00 -0 |

| \$031        | PRR   | R/W | -       | -       | -       | -       | -        | -        | PRR[1]  | PRR[0]        | 00         |

| \$032        | DRR   | R/W | -       | -       | -       | -       | -        | -        | -       | DRR[0]        | 0          |

| \$036        | COM   | R/W | COM[7]  | COM[6]  | COM[5]  | COM[4]  | COM[3]   | COM[2]   | COM[1]  | COM[0]        | ???? ????  |

| \$039        | LSEL  | R/W | DUTY[1] | DUTY[0] | BIAS4   | LSEL[4] | LSEL[3]  | LSEL[2]  | LSEL[1] | LSEL[0]       | 0001 1111  |

| \$03A        | LCTL  | R/W | LPWR    | BLANK   | REV     | SCAN    | CTR[3]   | CTR[2]   | CTR[1]  | CTR[0]        | 1000 0000  |

| \$03B        | LCK   | R/W | DRV[3]  | DRV[2]  | DRV[1]  | DRV[0]  | PUMPB    | LCK[2]   | LCK[1]  | LCK[0]        | 1111 0000  |

| \$03C        | IREQ  | R/W | -       | -       | IRBT    | IRPT    | IRT1     | IRT0     | IRDAC   | IRX           | 00 0000    |

| \$03E        | IENA  | R/W | -       | -       | IEBT    | IEPT    | IET1     | IET0     | IEDAC   | IEX           | 00 0000    |

Note: 1. Undefined bytes and bits should not be used.

### 8.3.2 Data RAM (\$0080~\$09FF)

Data RAM are organized in 2432 bytes from \$0080~\$09FF.

#### 8.3.3 Stack RAM (\$0100~\$01FF)

Stack RAM is organized in 256 bytes. It provides for a maximum of 128-level subroutine stacks and can be used as data memory.

## 8.3.4 LCD Frame Buffer (\$1000~\$10AF)

LCD frame buffer is accessible by both read/write instructions and LCD controller. Note that this area can also be used as data memory. Each pixel of LCD panel is directly mapped into this area. Refer to section 15.3 for the detail mapping.

<sup>2.</sup> Do not use bit modification instructions for write-only registers, such as RMBx, SMBx.

# 9. INTERRUPTS

# 9.1 Interrupt description

#### Brk

Instruction 'BRK' will cause software interrupt when interrupt disable flag (I) is cleared. Hardware will <u>push 'PC', 'P' Register to stack and set interrupt disable flag (I)</u>. Program counter then will be loaded with the BRK vector from locations \$7FFE and \$7FFF.

#### Reset

A positive transition of RESET pin will then cause an initialization sequence to begin. After the system has been operating, a low on this line at least of two clock cycles will cease ST20P64 activity. When a positive edge is detected, there is an initialization sequence lasting six clock cycles. Then the interrupt mask flag is set, the decimal mode is cleared and the program counter will loaded with the restart vector from locations \$7FFC (low byte) and \$7FFD (high byte). This is the start location for program control. This input should be high in normal operation.

#### **INTX Interrupt**

The IRX (INTX interrupt request) flag will be set while INTX edge signal occurs. The INTX interrupt will be active once IEX (INTX interrupt enable) is set, and interrupt mask flag is cleared. Hardware will <u>push 'PC', 'P' Register to stack and set interrupt mask flag (I)</u>. Program counter will be loaded with the INTX vector from locations \$7FF8 and \$7FF9.

#### **DAC Interrupt**

The IRDAC (DAC interrupt request) flag will be set while reload signal of DAC occurs. Then the DAC interrupt will be executed when IEDAC (DAC interrupt enable) is set, and interrupt mask flag is cleared. Hardware will <u>push 'PC', 'P' Register to stack and set interrupt mask flag (I)</u>. Program counter will be loaded with the DAC vector from locations <u>\$7FF6 and \$7FF7</u>.

#### **T0** Interrupt

The IRT0 (TIMER0 interrupt request) flag will be set while T0 overflows. With IET0 (TIMER0 interrupt enable) being set, the T0 interrupt will execute, and interrupt mask flag will be cleared. Hardware will push 'PC', 'P' Register to stack and set interrupt mask flag (I). Program counter will be loaded with the T0 vector from locations \$7FF4 and \$7FF5.

#### T1 Interrupt

The IRT1 (TIMER1 interrupt request) flag will be set while T1 overflows. With IET1 (TIMER1 interrupt enable) being set, the T1 interrupt will execute, and interrupt mask flag will be cleared. Hardware will push 'PC', 'P' Register to stack and set interrupt mask flag (I). Program counter will be loaded with the T1 vector from locations \$7FF2 and \$7FF3.

#### PT Interrupt

The IRPT (Port-A interrupt request) flag will be set while Port-A transition signal occurs. With IEPT (PT interrupt enable) being set, the PT interrupt will be execute, and interrupt mask flag will be cleared. Hardware will <u>push 'PC', 'P' Register to stack and set interrupt mask flag (I)</u>. Program counter will be loaded with the PT vector from locations <u>\$7FF0 and \$7FF1</u>.

#### **BT Interrupt**

The IRBT (Base timer interrupt request) flag will be set when Base Timer overflows. The BT interrupt will be executed once the IEBT (BT interrupt enable) is set and the interrupt mask flag is cleared. Hardware will <u>push 'PC', 'P' Register to stack and set interrupt mask flag (I)</u>. Program counter will be loaded with the BT vector from locations \$7FEE and \$7FEF.

All interrupt vectors are listed in TABLE 9-1.

**TABLE 9-1 Interrupt Vectors**

| Name  | Signal   | Vector address | Priority | Comment                       |

|-------|----------|----------------|----------|-------------------------------|

| BRK   | Internal | \$7FFF,\$7FFE  | 8        | Software BRK operation vector |

| RESET | External | \$7FFD,\$7FFC  | 1        | Reset vector                  |

| -     | -        | \$7FFB,\$7FFA  | -        | Reserved                      |

| INTX  | External | \$7FF9,\$7FF8  | 2        | PA0 edge interrupt            |

| DAC   | Internal | \$7FF7,\$7FF6  | 3        | Reload DAC data interrupt     |

| T0    | INT/EXT  | \$7FF5,\$7FF4  | 4        | Timer0 interrupt              |

| T1    | INT/EXT  | \$7FF3,\$7FF2  | 5        | Timer1 interrupt              |

| PT    | External | \$7FF1,\$7FF0  | 6        | Port-A transition interrupt   |

| ВТ    | Internal | \$7FEF,\$7FEE  | 7        | Base Timer interrupt          |

# 9.2 Interrupt Request Flag

Interrupt request flag can be cleared by two methods. One is to write "0" to IREQ, the other is to initiate the interrupt service

routine when interrupt occurs. Hardware will automatically clear the Interrupt flag.

**TABLE 9-2 Interrupt Request Register (IREQ)**

| Address                                                                      | Name                                                                    | R/W          | Bit 7       | Bit 6       | Bit 5 | Bit 4                                   | Bit 3     | Bit 2       | Bit 1       | Bit 0       | Default |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|-------------|-------------|-------|-----------------------------------------|-----------|-------------|-------------|-------------|---------|--|

| \$03C                                                                        | IREQ                                                                    | R/W          | -           | -           | IRBT  | IRPT                                    | IRT1      | IRT0        | IRDAC       | IRX         | 00 0000 |  |

| Bit 5:                                                                       | IRBT: B                                                                 | ase Timer    | Interrupt F | Request bi  | it    | Bit 2:                                  | IRT0: Tin | ner0 Interr | upt Reque   | est bit     |         |  |

|                                                                              | 1 = Time base interrupt occurs<br>0 = Time base interrupt doesn't occur |              |             |             |       |                                         |           |             | w interrup  |             |         |  |

|                                                                              | 0 = Tim                                                                 | ne base in   | terrupt doe | esn't occui | r     |                                         | 0 = Time  | er0 overflo | w interrup  | t doesn't d | occur   |  |

| Bit 4: IRPT: Port-A Interrupt Request bit Bit 1: IRDAC: DAC reload Interrupt |                                                                         |              |             |             |       |                                         |           |             |             |             |         |  |

| Bit 4:                                                                       | IRPT: P                                                                 | ort-A Inter  | rupt Reque  | est bit     |       | Bit 1:                                  | IRDAC:    | DAC reloa   | d Interrupt | Request     | bit     |  |

|                                                                              | 1 = Poi                                                                 | rt-A transit | ion interru | pt occurs   |       |                                         | 1 = DAC   | time out    | interrupt o | ccurs       |         |  |

|                                                                              | 0 = Poi                                                                 | rt-A transit | ion interru | pt doesn't  | occur |                                         | 0 = DAC   | time out    | interrupt d | oesn't occ  | cur     |  |

|                                                                              |                                                                         |              |             |             |       |                                         |           |             |             |             |         |  |

| Bit 3:                                                                       | IRT1: Ti                                                                | mer1 Inter   | rupt Requ   | est bit     |       | Bit 0:                                  | IRX: INT  | X Interrupt | t Request   | bit         |         |  |

|                                                                              | 1 = Tim                                                                 | ner1 overfl  | ow interru  | ot occurs   |       |                                         | 1 = INT   | X edge inte | errupt occi | urs         |         |  |

|                                                                              | 0 = Tim                                                                 | ner1 overfl  | ow interru  | ot doesn't  | occur | r 0 = INTX edge interrupt doesn't occur |           |             |             |             |         |  |

|                                                                              |                                                                         |              |             |             |       |                                         |           |             |             |             |         |  |

**TABLE 9-3 Interrupt Enable Register (IENA)**

|                                          | TABLE 9 9 Interrupt Enable Register (IEIA)   |             |              |             |       |                                       |                                          |              |              |            |         |

|------------------------------------------|----------------------------------------------|-------------|--------------|-------------|-------|---------------------------------------|------------------------------------------|--------------|--------------|------------|---------|

| Address                                  | Name                                         | R/W         | Bit 7        | Bit 6       | Bit 5 | Bit 4                                 | Bit 3                                    | Bit 2        | Bit 1        | Bit 0      | Default |

| \$03E                                    | IENA                                         | *R/W        | -            | -           | IEBT  | IEPT                                  | IET1                                     | IET0         | IEDAC        | IEX        | 00 0000 |

| Bit 5:                                   | Bit 5: IEBT: Base Timer Interrupt Enable bit |             |              |             |       |                                       | Bit 2: IET0: Timer0 Interrupt Enable bit |              |              |            |         |

| 1 = Time base interrupt enable           |                                              |             |              |             |       |                                       | 1 = Ti                                   | mer0 over    | flow interr  | upt enable | )       |

| 0 = Time base interrupt disable          |                                              |             |              |             |       | 0 = Timer0 overflow interrupt disable |                                          |              |              |            | Э       |

| Bit 4:                                   | IEPT: Po                                     | ort-A Inter | rupt Enabl   | e bit       |       | Bit 1:                                | IEDAC: [                                 | DAC reloa    | d Interrupt  | Enable bi  | t       |

|                                          | 1 = F                                        | Port-A tran | sition inter | rrupt enab  | le    |                                       | 1 = D                                    | AC time o    | ut interrup  | t enable   |         |

|                                          | 0 = F                                        | Port-A tran | sition inter | rrupt disab | le    |                                       | 0 = D                                    | AC time o    | ut interrup  | t disable  |         |

| Bit 3: IET1: Timer1 Interrupt Enable bit |                                              |             |              |             |       | Bit 0: IEX: INTX Interrupt Enable bit |                                          |              |              |            |         |

| 1 = Timer1 overflow interrupt enable 1 = |                                              |             |              |             |       | 1 = IN                                | ITX edge i                               | interrupt ei | nable        |            |         |

|                                          | 0 = 7                                        | imer1 ove   | erflow inter | rupt disab  | le    |                                       | 0 = IN                                   | ITX edge i   | interrupt di | sable      |         |

# **10. I/O PORTS**

# 10.1 Description

ST20P64 can supply total 24 GPIOs divided into three I/O ports, Port-A, Port-B, and Port-C. Besides I/O function, Port-B/C can also be used as LCD segment drives. For detail pin assignment, please refer to TABLE 10-1

NOTE: all of unused input pins should be pulled up to minimize standby current

**TABLE 10-1 I/O Description**

| PORT NAME      | PAD NAME  | PAD NUMBER | PIN TYPE | FEATURE                            |  |  |  |  |  |

|----------------|-----------|------------|----------|------------------------------------|--|--|--|--|--|

| . Sitt itruite | PA0/INTX  | 55         | 1/0      | 1 2/11 0/12                        |  |  |  |  |  |

| -              | PA1       | 56         | 1/0      |                                    |  |  |  |  |  |

| -              | PA2       | 57         | I/O      |                                    |  |  |  |  |  |

| -              | PA3       | 58         | I/O      |                                    |  |  |  |  |  |

| Port-A         | PA4       | 59         | I/O      | Programmable input/output pin      |  |  |  |  |  |

|                | PA5       | 60         | I/O      |                                    |  |  |  |  |  |

| -              | PA6       | 61         | I/O      |                                    |  |  |  |  |  |

|                | PA7       | 62         | I/O      | _                                  |  |  |  |  |  |

|                | SEG40/PB0 | 35         | I/O      |                                    |  |  |  |  |  |

|                | SEG41/PB1 | 36         | I/O      |                                    |  |  |  |  |  |

|                | SEG42/PB2 | 37         | I/O      |                                    |  |  |  |  |  |

|                | SEG43/PB3 | 38         | I/O      |                                    |  |  |  |  |  |

| Port-B         | SEG44/PB4 | 39         | I/O      | Programmable input/output pin      |  |  |  |  |  |

|                | SEG45/PB5 | 40         | I/O      |                                    |  |  |  |  |  |

|                | SEG46/PB6 | 41         | I/O      |                                    |  |  |  |  |  |

|                | SEG47/PB7 | 42         | I/O      |                                    |  |  |  |  |  |

|                | SEG32/PC0 | 27         | I/O      |                                    |  |  |  |  |  |

|                | SEG33/PC1 | 28         | I/O      |                                    |  |  |  |  |  |

|                | SEG34/PC2 | 29         | I/O      |                                    |  |  |  |  |  |

| Port-C         | SEG35/PC3 | 30         | I/O      | Programmable input/output pin      |  |  |  |  |  |

| Port-C         | SEG36/PC4 | 31         | I/O      | Programmable input/output pin      |  |  |  |  |  |

|                | SEG37/PC5 | 32         | I/O      |                                    |  |  |  |  |  |

|                | SEG38/PC6 | 33         | I/O      |                                    |  |  |  |  |  |

|                | SEG39/PC7 | 34         | I/O      |                                    |  |  |  |  |  |

|                | COM8      | 76         | 0        |                                    |  |  |  |  |  |

|                | COM9      | 77         | 0        |                                    |  |  |  |  |  |

|                | COM10     | 78         | 0        |                                    |  |  |  |  |  |

| COM[8~15]      | COM11     | 79         | 0        | Programmable open drain output pin |  |  |  |  |  |

| 20[0 .0]       | COM12     | 80         | 0        | - 155.5abib opon aram balpat pin   |  |  |  |  |  |

|                | COM13     | 81         | 0        |                                    |  |  |  |  |  |

|                | COM14     | 82         | 0        |                                    |  |  |  |  |  |

|                | COM15     | 83         | 0        |                                    |  |  |  |  |  |

# 10.2 Port-A

#### 10.2.1 Port-A Description

Port-A is a bit-programmable bi-direction I/O port, which is controlled by PCA register. It also provides bit programmable pull-up resistor for each input pin. Two interrupts can be

triggered by Port-A, de-bounced interrupt for keyboard scan and edge sensitive interrupt (PA0 only) for external event.

**TABLE 10-2 Summary Of Port-A Registers**

| Address | Name        | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |

|---------|-------------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| \$000   | PA          | R/W | PA[7]  | PA[6]  | PA[5]  | PA[4]  | PA[3]  | PA[2]  | PA[1]  | PA[0]  | 1111 1111 |

| \$008   | PCA         | R/W | PCA[7] | PCA[6] | PCA[5] | PCA[4] | PCA[3] | PCA[2] | PCA[1] | PCA[0] | 0000 0000 |

| \$00E   | PAK         | R/W | PAK[7] | PAK[6] | PAK[5] | PAK[4] | PAK[3] | PAK[2] | PAK[1] | PAK[0] | 0000 0000 |

| \$00F   | <b>PMCR</b> | R/W | PULL   | PDBN   | INTEG  | -      | TEST   | -      | -      | -      | 100 - 0   |

| \$03C   | IREQ        | R/W | -      | •      | IRBT   | IRPT   | IRT1   | IRT0   | IRDAC  | IRX    | 00 0000   |

| \$03E   | IENA        | R/W | -      | •      | IEBT   | IEPT   | IET1   | IET0   | IEDAC  | IEX    | 00 0000   |

#### 10.2.2 Port-A I/O Control

Direction of Port-A is controlled by PCA. Each bit of PCA controls the direction of one single I/O of Port-A respectively,

with "1" for output mode, and "0" for input mode.

**TABLE 10-3 Port-A Control Register (PCA)**

| Address | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |

|---------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| \$008   | PCA  | R/W | PCA[7] | PCA[6] | PCA[5] | PCA[4] | PCA[3] | PCA[2] | PCA[1] | PCA[0] | 0000 0000 |

Bit 7~0: PCA[7~0]: Port-A directional bits

1 = Output mode 0 = Input mode

#### 10.2.3 Dynamic input buffers of Port-A

When Port-A is used as keyboard return lines and one key is pressed, the LCD segment waveform will input to Port-A and then be affected by the input buffer of Port-A. Setting control bit of PAK may enable the dynamic input buffer of the related input pin and thus lower the effect on display quality.

The dynamic input buffer is enabled only when the LCD keyboard awaking pulses exist, that is, LCTL[7]=0 LCTL[4]=1.

Otherwise setting of PAK will be ignored, and the dynamic input buffer will be off.

**Note:** The dynamic input buffer can not pass the real value appears at input pin. It must be off when reading Port-A.

TABLE 10-4 Port-A used as keyboard return line selection

| Address | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |

|---------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| \$00E   | PAK  | R/W | PAK[7] | PAK[6] | PAK[5] | PAK[4] | PAK[3] | PAK[2] | PAK[1] | PAK[0] | 0000 0000 |

#### Bit 7~0: PAK[7~0]:

1 = Port-A used as keyboard return line.

0 = Port-A used as keyboard normal I/O.

### 10.2.4 Port-A Pull-Up Option

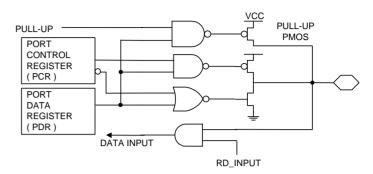

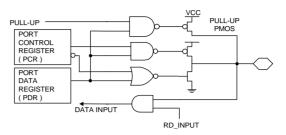

Port-A contains PMOS transistors of pull-up resistor controlled by software in bit-manner. In case of input direction, on/off of the pull-up PMOS transistor is controlled by the data wrote to data register, PA. "1" is for enable and "0" is for disable. Above all, whole pull-up control is by PULL bit of PMCR. Refer to FIGURE 10-1 for the block description.

FIGURE 10-1 Port-A Block Diagram

**TABLE 10-5 Port Function Control Register (PMCR)**

| Address | Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

|---------|------|-----|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| \$00F   | PMCR | R/W | PULL  | PDBN  | INTEG |       | TEST  | -     | -     | -     | 100 - 0 |

Bit 7: PULL: Enable all pull-up function bit

1 = Enable pull-up function 0 = Disable pull-up function

Bit 6: PDBN: Enable Port-A interrupt de-bounce bit

1 = De-bounce for Port-A interrupt 0 = No de-bounce for Port-A interrupt

Bit 5: INTK interrupt edge option bit

1 = Rising edge 0 = Falling edge

Bit3: **TEST**: Test bit, must be "0"

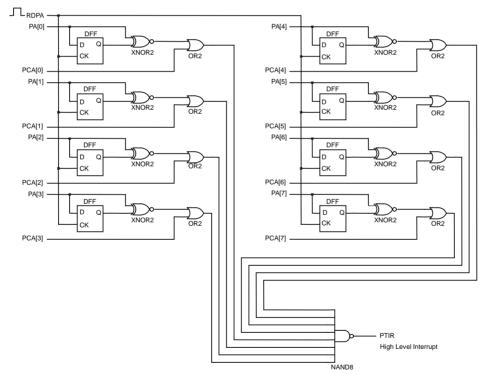

#### 10.2.5 Port-A Interrupt

Port-A is suitable for the return line inputs of keyboard scan because of the port transition interrupt function. Difference between current value and the data kept previously of Port-A will generate an interrupt request. The last state of Port-A must be latched before transition, and this can be done by one read

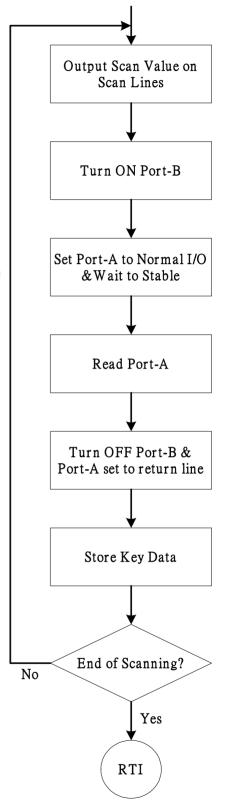

instruction to Port-A. If both INTX and PT interrupts are enabled, signal edge of PA0 may trigger PT interrupt as well as INTX. Steps and program example are shown below. Also refer to FIGURE 10-2 for the block diagram.

#### **Operate Port-A interrupt steps:**

- 1. Set input mode.

- 2. Read Port-A.

- Clear interrupt request flag (IRPT).

- Set interrupt enable flag (IEPT). 4.

- 5. Clear CPU interrupt disable flag (I).

- Read Port-A before 'RTI' instruction in ISR.

#### Example:

STZ <PCA ; Set input mode. LDA #\$FF ; PA be PULL-UP. STA <PA LDA <PA ; Keep last state. RMB4 <IREQ : Clear IRQ flag. SMB4 ; Enable INT. <IENA CLI

#### Interrupt subroutine

LDA <PA ; Keep last state. RTI

FIGURE 10-2 Port Interrupt Logic Diagram

#### 10.2.6 Port-A Interrupt De-bounce

ST20P64 has hardware de-bounce block for Port-A interrupt. It is enabled with "1" and disable with "0" of PDBN(PMCR[6]). The de-bounce function is activated by Port-A transition. It uses

OSCX as the sampling clock. The de-bounce time is <u>OSCX x</u> <u>512 cycles (about 16 ms).</u> Data filtered by de-bounce presents a stable state, then the interrupt can be issued.

**TABLE 10-6 Port Function Control Register (PMCR)**

| Address | Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

|---------|------|-----|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| \$00F   | PMCR | R/W | PULL  | PDBN  | INTEG | -     | TEST  | 1     | 1     | 1     | 1000    |

Bit 6: PDBN: Enable Port-A interrupt de-bounce bit

1 = De-bounce for Port-A interrupt 0 = No de-bounce for Port-A interrupt

#### 10.2.7 PA0/INTX

PA0 plays another function of external edge-sensitive interrupt source. Falling or rising edge is controlled by INTEG(PMCR[5]). Please refer to FIGURE 10-3. If both INTX and PT interrupts

are enabled, signal edge of PA0 may trigger PT interrupt as well as INTX. Steps and program example are shown below.

#### Steps for INTX interrupt operation:

1. Set PA0 to input mode. (PCA[0])

2. Select edge level. (INTEG)

3. Clear INTX interrupt request flag. (IRX)

4. Set INTX interrupt enable bits. (IEX)

5. Clear CPU interrupt mask flag (I).

Example:

RMB0 <PCA ; Set input mode.

SMB5 <PMCR ; Rising edge.

RMB0 <IREQ ; Clear IRQ flag.

SMB0 <IENA ; Enable INTX interrupt.

CLI

Falling Edge Interrupt

FIGURE 10-3 INTX Logic Diagram

PMCR[5]

PA 0/INTX

## 10.3 Port-B and Port-C

#### 10.3.1 General Description

Port-B and Port-C are bit-programmable bi-direction I/O ports, controlled by PCB and PCC registers. There is also bit programmable pull-up resistor for each input pin. All of the 16 I/Os can change into LCD segment drives. Control register

LSEL specifies which of these I/Os are LCD drives(<u>Please refer to TABLE 15-2</u>LCD Segment Number Selection Register (LSEL)).

TABLE 10-7 Summary of Port-B AND Port-C Registers

| Address | Name        | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Defa  | ault |

|---------|-------------|-----|--------|--------|--------|---------|---------|---------|---------|---------|-------|------|

| \$001   | PB          | R/W | PB[7]  | PB[6]  | PB[5]  | PB[4]   | PB[3]   | PB[2]   | PB[1]   | PB[0]   | 1111  | 1111 |

| \$002   | PC          | R/W | PC[7]  | PC[6]  | PC[5]  | PC[4]   | PC[3]   | PC[2]   | PC[1]   | PC[0]   | 1111  | 1111 |

| \$009   | PCB         | R/W | PCB[7] | PCB[6] | PCB[5] | PCB[4]  | PCB[3]  | PCB[2]  | PCB[1]  | PCB[0]  | 0000  | 0000 |

| \$00A   | PCC         | R/W | PCC[7] | PCC[6] | PCC[5] | PCC[4]  | PCC[3]  | PCC[2]  | PCC[1]  | PCC[0]  | 0000  | 0000 |

| \$00F   | <b>PMCR</b> | R/W | PULL   | PDBN   | INTEG  | -       | TEST    | -       | -       | •       | 100 - |      |

| \$039   | LSEL        | R/W | -      | -      | -      | LSEL[4] | LSEL[3] | LSEL[2] | LSEL[1] | LSEL[0] | 1     | 1111 |

#### 10.3.2 Input/Output Control

PCB/PCC controls the I/O direction of Port-B/C. Each bit of PCB[7~0]/PCC[7~0] controls the direction of one single bit of

Port-B/C respectively, with "1" for output mode, and "0" for input mode

**TABLE 10-8 PORT-B Control Register (PCB)**

| Address | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Defa | ıult |

|---------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|------|------|

| \$009   | PCB  | R/W | PCB[7] | PCB[6] | PCB[5] | PCB[4] | PCB[3] | PCB[2] | PCB[1] | PCB[0] | 0000 | 0000 |

Bit 7~0: PCB[7~0]: Port-B directional bits

1 = Output mode 0 = Input mode

**TABLE 10-9 PORT-C Control Register (PCC)**

| Address | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Defa | ault |

|---------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|------|------|

| \$00A   | PCC  | R/W | PCC[7] | PCC[6] | PCC[5] | PCC[4] | PCC[3] | PCC[2] | PCC[1] | PCC[0] | 0000 | 0000 |

Bit 7~0: PCC[7~0]: Port-C directional bits

1 = Output mode 0 = Input mode

#### 10.3.3 PORT-B and PORT-C PULL-UP OPTION

Port-B/C contains PMOS transistors of pull-up resistor controlled by software in bit-manner. In case of input direction, on/off of the pull-up PMOS transistor is controlled by the data wrote to data register, PB/PC. "1" is for enable and "0" is for disable. Above all, whole pull-up control is by PULL bit of PMCR. Refer to FIGURE 10-4 for the block description.

FIGURE 10-4 Port-B and Port-C Block Diagram

**TABLE 10-10 Port Control Register (PMCR)**

|         |      |     |       |       |       |       |       | (     |       |       |         |

|---------|------|-----|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| Address | Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

| \$00F   | PMCR | R/W | PULL  | PDBN  | INTEG | -     | TEST  | -     | -     | -     | 100     |

Bit 7: PULL: Enable all pull-up functions bit

1 = Enable pull-up function0 = Disable pull-up function

## **10.4 COMMON-PORT**

The COM15~COM8 can be used as LCD drivers or output ports. In output port mode, COM[7~0] will be map to COM15~COM8 output ports, which pin assignment will be decided by DUTY[1:0] of \$39(LSEL), Please refer to the following table.

TABLE 10-11 LCD Segment Number Selection Register (LSEL)

| Addres | s Name | R/W | Bit 7   | Bit 6   | Bit 5 | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Default   |

|--------|--------|-----|---------|---------|-------|---------|---------|---------|---------|---------|-----------|

| \$039  | LSEL   | R/W | DUTY[1] | DUTY[0] | BIAS4 | LSEL[4] | LSEL[3] | LSEL[2] | LSEL[1] | LSEL[0] | 0001 1111 |

Bit 5: **DUTY**: Common output selection bit

> 0X = 1/16 duty and COM15~COM8 used as LCD Common pins 10 = 1/12 duty and COM15~COM12 used as output pins

11 = 1/8 duty and COM15~COM8 used as output pins

TABLE 10-12 COM Output Register (COM)

|         |        |     |                                     |        | 0 0    | Oin Outpu | it itogioto | . (55.4.) |        |        |           |

|---------|--------|-----|-------------------------------------|--------|--------|-----------|-------------|-----------|--------|--------|-----------|

| Address | Name   | R/W | Bit 7                               | Bit 6  | Bit 5  | Bit 4     | Bit 3       | Bit 2     | Bit 1  | Bit 0  | Default   |

| \$036   | COM    | R/W | COM[7]                              | COM[6] | COM[5] | COM[4]    | COM[3]      | COM[2]    | COM[1] | COM[0] | ???? ???? |

| Bit 7:  | 1 = CC |     | M15 scan o<br>out =FLOA<br>out =LOW |        |        |           |             |           |        |        |           |

| Bit 6:  | 1 = CC |     | M14 scan o<br>out =FLOA<br>out =LOW |        |        |           |             |           |        |        |           |

| Bit 5:  | 1 = CC |     | M13 scan o                          |        |        |           |             |           |        |        |           |

0 = COM13 output =LOW

Bit 4: COM[4]: COM12 scan output bit 1 = COM12 output =FLOATING 0 = COM12 output =LOW

Bit 3: COM[3]: COM11 scan output bit 1 = COM11 output =FLOATING 0 = COM11 output =LOW

Bit 2: COM[2]: COM10 scan output bit 1 = COM10 output =FLOATING 0 = COM10 output =LOW

COM[1]: COM9 scan output bit Bit 1: 1 = COM9 output =FLOATING 0 = COM9 output =LOW

COM[0]: COM8 scan output bit 1 = COM8 output =FLOATING 0 = COM8 output =LOW

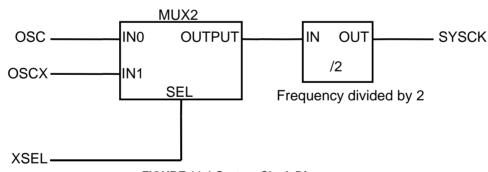

# 11. OSCILLATOR

ST20P64 has dual clock sources, OSC (RC) and OSCX (32768Hz crystal). The system clock (SYSCK) can be switched between OSC and OSCX, and is controlled by XSEL (SYS[7]). When system clock is switched, the warm-up cycles occur at the same time. Clock source being used is shown at

XSEL (read). Read and test XSEL to confirm SYSCK is already switched over. Other blocks, such as LCD controller, Timer1, Base Timer and PSG, can utilize these two clock sources as well.

**TABLE 11-1 System Control Register (SYS)**

| Address Nam | e R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default   |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----------|

| \$030 SYS   | R/W   | XSEL  | OSTP  | XSTP  | TEST  | WSKP  | WAIT  | -     | LVDET | 0000 00-0 |

Bit 7: XSEL: System clock (SYSCK) select (write) / confirm (read) bit

1 = OSCX 0 = OSC

Bit 6: OSTP: OSC stop control bit

1 = Disable OSC 0 = Enable OSC

Bit 5: XSTP: OSCX stop control bit

1 = Disable OSCX 0 = Enable OSCX

Bit 4: TEST: Test bit, must be "0"

#### Note:

- 1. XSEL (SYS[7]) shows which clock source is used for SYSCK when it is read.

- 2. System warm-up of 16 or 256 oscillation cycles occurs when system clock (SYSCK) is changed or power on reset.

FIGURE 11-1 System Clock Diagram

# 12. TIMER/EVENT COUNTER

# 12.1 Prescaler

#### 12.1.1 Function Description

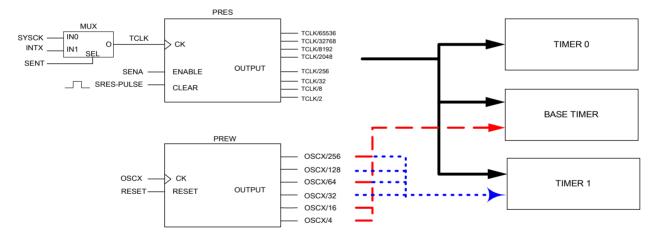

The ST20P64 has three timers, Base timer, Timer 0 and Timer 1, and two prescalers PRES and PREW. There are two clock

sources, SYSCK and INTX, for PRES and one clock source, OSCX, for PREW. Refer to FIGURE 12-1

**TABLE 12-1 Summary of Timer Registers**

| Address | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |

|---------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| \$021   | BTM  | W   | -      | -      | -      | -      | BTM[3] | BTM[2] | BTM[1] | BTM[0] | 0000      |

| \$023   | PRS  | R   | PRS[7] | PRS[6] | PRS[5] | PRS[4] | PRS[3] | PRS[2] | PRS[1] | PRS[0] | 0000 0000 |

| ψ023    | FINO | W   | SRES   | SENA   | SENT   | -      | •      |        | •      | •      | 000       |

| \$024   | TOM  | R/W | -      | -      | T0M[5] | T0M[4] | •      | T0M[2] | T0M[1] | T0M[0] | 00 -000   |

| \$025   | T0C  | R/W | T0C[7] | T0C[6] | T0C[5] | T0C[4] | T0C[3] | T0C[2] | T0C[1] | T0C[0] | 0000 0000 |

| \$026   | T1M  | R/W | -      |        | -      | T1M[4] | T1M[3] | T1M[2] | T1M[1] | T1M[0] | 0 0000    |

| \$027   | T1C  | R/W | T1C[7] | T1C[6] | T1C[5] | T1C[4] | T1C[3] | T1C[2] | T1C[1] | T1C[0] | 0000 0000 |

| \$030   | SYS  | R/W | XSEL   | OSTP   | XSTP   | TEST   | WSKP   | WAIT   | -      | -      | 0000 00   |

| \$03C   | IREQ | R/W | -      | -      | IRBT   | IRPT   | IRT1   | IRT0   | IRDAC  | IRX    | 00 0000   |

| \$03E   | IENA | R/W | -      | -      | IEBT   | IEPT   | IET1   | IET0   | IEDAC  | IEX    | 00 0000   |

FIGURE 12-1 Structure Of Two Prescalers

#### 12.1.2 PRES

The prescaler PRES is an 16-bits counter as shown in FIGURE 12-1. Which provides four clock sources for base timer and timer1, and it is controlled by register PRS. The instruction read toward PRS will bring out the content of PRES and the

Instruction write toward PRS will reset, enable or select clock sources for PRES.

When user set external interrupt as the input of PRES for event counter, combining PRES and Timer1 will get a 16bit-event counter.

**TABLE 12-2 Prescaler Control Register (PRS)**

| Address      | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |

|--------------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| \$023        | PRS  | R   | PRS[7] | PRS[6] | PRS[5] | PRS[4] | PRS[3] | PRS[2] | PRS[1] | PRS[0] | 0000 0000 |

| <b>\$023</b> | FKS  | W   | SRES   | SENA   | SENT   | -      | -      | -      | -      | -      | 000       |

**READ**

Bit 7~0: PRS[7~0]: The low byte value of PRES counter

WRITE

Bit 7: SRES: Prescaler Reset bit

Write "1" to reset the prescaler (PRS[7~0])

Bit 6: **SENA:** Prescaler enable bit

0 = Disable prescaler counting1 = Enable prescaler counting

Bit 5: SENT : Clock source(TCLK) selection for prescaller PRES

0 = Clock source from system clock "SYSCK" 1 = Clock source from external events "INTX"

#### 12.1.3 PREW

The prescaler PREW is an 8-bits counter as shown in FIGURE 12-1. PREW provides four clocks source for base timer and

timer1. It stops counting only if OSCX stops or hardware reset occurs.

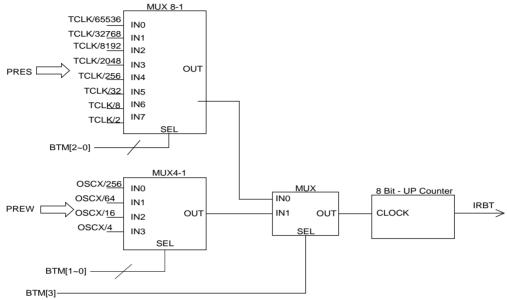

## 12.2 Base timer

### 12.2.1 Function Description

Base timer is an 8-bit up counting timer. When it overflows from \$FF to \$00, a timer interrupt request IRBT will be generated.

Please refer to FIGURE 12-2

FIGURE 12-2 Structure Of Base Timer

#### 12.2.2 Base Timer Clock Source Control

Several clock sources can be selected for Base Timer. Please refer to TABLE 12-3

**TABLE 12-3 Clock Sources Of Base Timer**

| * SENA | BTM[3] | BTM[2] | BTM[1] | BTM[0] | Base Timer source clock |

|--------|--------|--------|--------|--------|-------------------------|

| 0      | Х      | X      | Х      | X      | STOP                    |

| 1      | 0      | 0      | 0      | 0      | TCLK / 65536            |

| 1      | 0      | 0      | 0      | 1      | TCLK / 32768            |

| 1      | 0      | 0      | 1      | 0      | TCLK / 8192             |

| 1      | 0      | 0      | 1      | 1      | TCLK / 2048             |

| 1      | 0      | 1      | 0      | 0      | TCLK / 256              |

| 1      | 0      | 1      | 0      | 1      | TCLK / 32               |

| 1      | 0      | 1      | 1      | 0      | TCLK / 8                |

| 1      | 0      | 1      | 1      | 1      | TCLK / 2                |

| X      | 1      | 0      | 0      | 0      | OSCX / 256              |

| X      | 1      | 0      | 0      | 1      | OSCX / 64               |

| X      | 1      | 0      | 1      | 0      | OSCX / 16               |

| X      | 1      | 0      | 1      | 1      | OSCX / 4                |

Note: TCLK will stop when an '0' is written to SENA (PRS[6]).

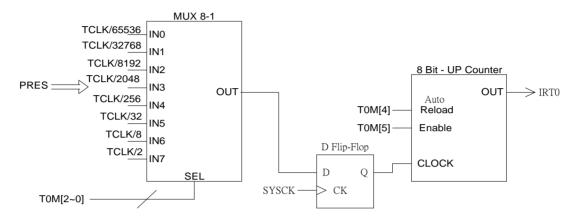

### 12.3 Timer 0

#### 12.3.1 Function Description

The Timer0 is an 8-bit up counter. It can be used as a timer or an event counter. T0C(\$25) is a real time read/write counter. When an overflow from \$FF to \$00, a timer interrupt request IRT0 will

be generated. Timer0 will stop counting when system clock stops. Please refer to FIGURE 12-3.

FIGURE 12-3 Timer0 Structure

#### 12.3.2 Timer0 Clock Source Control

Several clock sources can be chosen from for Timer0. <u>It's very important that Timer0 can keep counting as long as SYSCK</u>

stays active. Refer to TABLE 12-4.

**TABLE 12-4 Clock Sources Of Timer0**

| T0M[2] | T0M[1] | T0M[0] | T0 Ti mer Clock Source |

|--------|--------|--------|------------------------|

| 0      | 0      | 0      | TCLK/65536             |

| 0      | 0      | 1      | TCLK/32768             |

| 0      | 1      | 0      | TCLK/8192              |

| 0      | 1      | 1      | TCLK/2048              |

| 1      | 0      | 0      | TCLK/256               |

| 1      | 0      | 1      | TCLK/32                |

| 1      | 1      | 0      | TCLK/8                 |

| 1      | 1      | 1      | TCLK/2                 |

T0M[4]: Control automatic reload operation

0 : No auto reload

1 : Auto reload

T0M[5]: Control Timer 0 enable/disable

0 : Disable counting 1 : Enable counting

SENA : Prescaler enable bit

0 : TCLK stop 1 : TCLK counting

TABLE 12-5 Timer0 Register (T0C)

|         | TABLE 12 0 Timero Register (100) |     |        |        |        |        |        |        |        |        |           |  |  |  |

|---------|----------------------------------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|--|--|--|

| Address | Name                             | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |  |  |  |

| \$025   | T0C                              | R/W | T0C[7] | T0C[6] | T0C[5] | T0C[4] | T0C[3] | T0C[2] | T0C[1] | T0C[0] | 0000 0000 |  |  |  |

|         |                                  |     |        |        |        |        |        |        |        |        |           |  |  |  |

Bit 7-0: **TOC[7-0]**: Timer0 up counter register

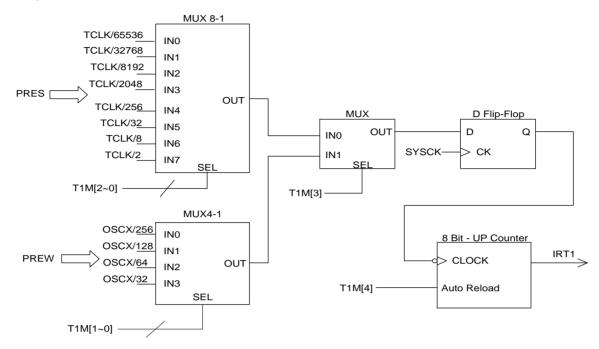

## 12.4 Timer 1

The Timer1 is an 8-bit up counter. It used as timer/counter as program specified. The difference between base timer is that Timer1 will halt during CPU SBY, but base timer will not. It is shown in FIGURE 12-4.

FIGURE 12-4 Timer1 Structure

TABLE 12-6 Timer1 Register (T1C)

| Address | Name | R/W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default   |

|---------|------|-----|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| \$027   | T1C  | R/W | T1C[7] | T1C[6] | T1C[5] | T1C[4] | T1C[3] | T1C[2] | T1C[1] | T1C[0] | 0000 0000 |

|         |      |     |        |        |        |        |        |        |        |        |           |

Bit 7-0: T1C[7-0]: Timer1 up counter register

**TABLE 12-7 Clock Sources Of Timer1**

| T1M[3] | T1M[2] | T1M[1]      | T1M[0]      | T1 Timer Clock Source |  |  |

|--------|--------|-------------|-------------|-----------------------|--|--|

| 0      | 0      | 0           | 0           | TCLK/65536            |  |  |

| 0      | 0      | 0           | 1           | TCLK/32768            |  |  |

| 0      | 0      | 1           | 0           | TCLK/8192             |  |  |

| 0      | 0      | 1           | 1           | TCLK/2048             |  |  |

| 0      | 1      | 0           | 0           | TCLK/256              |  |  |

| 0      | 1      | 0           | 1           | TCLK/32               |  |  |

| 0      | 1      | 1           | 0           | TCLK/8                |  |  |

| 0      | 1      | 1           | 1           | TCLK/2                |  |  |

| 1      | 0      | 0           | 0           | OSCX/256              |  |  |

| 1      | 0      | 0           | 1           | OSCX/128              |  |  |

| 1      | 0      | 1           | 1 0 OSCX/64 |                       |  |  |

| 1      | 0      | 1 1 OSCX/32 |             |                       |  |  |

|        |        |             |             |                       |  |  |

T1M[4]: Control automatic reload operation

0: No auto reload

1: auto reload

SENA : Prescaler enable bit

0 : TCLK stop 1 : TCLK counting

## 13. PSG

# 13.1 Function description

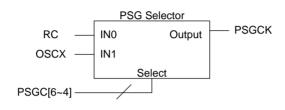

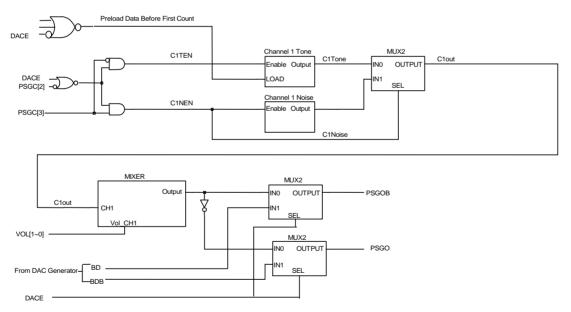

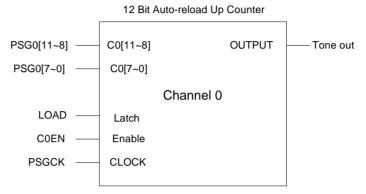

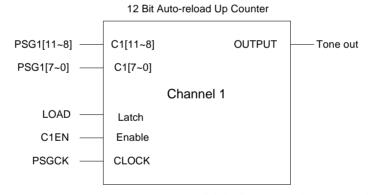

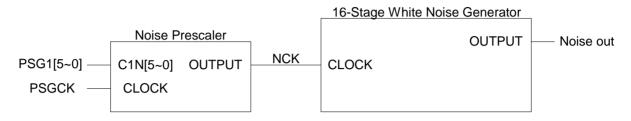

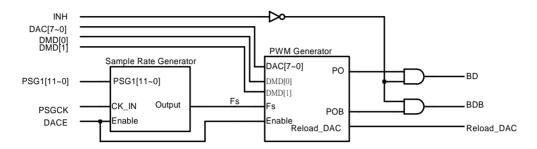

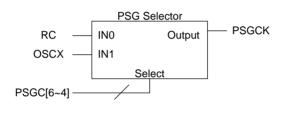

The built-in dual channel Programmable Sound Generator (PSG) is controlled by registers. Its flexibility makes it useful in applications such as music synthesis, sound effects generation, audible alarms and tone signaling. In order to generate sound effects while allowing the processor to perform other tasks, the PSG can continue to produce sound after the initial commands have been given by the CPU. The structure of PSG was shown in FIGURE 13-2 and the PSG clock source is shown in

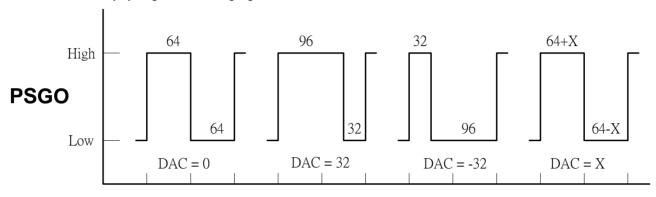

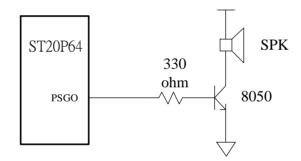

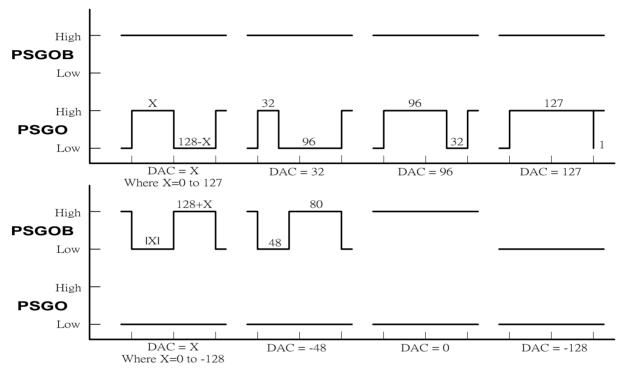

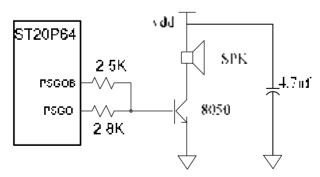

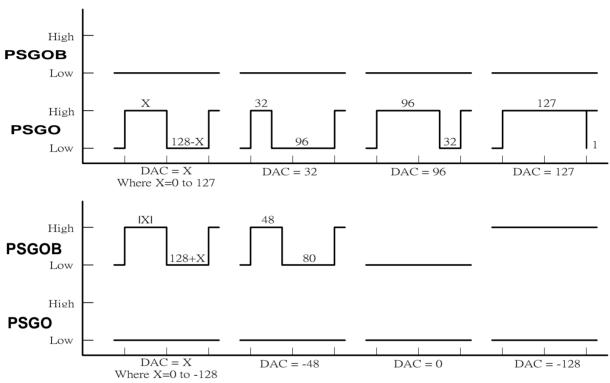

FIGURE 13-1. ST20P64 has three playing modes. First is that both channel0 (CH0) and channel1 (CH1) output square type tones. Second is CH0 outputs square tone, and CH1 outputs noise. Third mode is PWM DAC mode. Sounds of two channels are mixed into one signal and are outputted in the form of digital waveform from two pins, PSGOB/PSGO. Therefore one AC waveform can be performed.

|    | PSGC  |   | PSGCK     |

|----|-------|---|-----------|

| B6 | B5 B4 |   | PSGCK     |

| 0  | 0     | 0 | SYSCK     |

| Х  | 0 1   |   | SYSCK/2   |

| Х  | 1     | 0 | SYSCK/4   |

| 0  | 1     | 1 | SYSCK/8   |

| 1  | 0     | 0 | SYSCK x 2 |

FIGURE 13-1 PSG Clock Source Control

FIGURE 13-2 PSG Block Diagram

PS: In order to make sure the PSG function is working normally on the EV or Real Chip Board, Please connect PSG's power **PVCC** to VCC

**TABLE 13-1 Summary Of PSG Registers**

|                | in the second of |     |         |         |         |         |          |               |         |               |            |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|---------|---------|---------|----------|---------------|---------|---------------|------------|--|--|

| <b>Address</b> | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3    | Bit 2         | Bit 1   | Bit 0         | Default    |  |  |

| \$010          | PSG0L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W   | PSG0[7] | PSG0[6] | PSG0[5] | PSG0[4] | PSG0[3]  | PSG0[2]       | PSG0[1] | PSG0[0]       | 0000 0000  |  |  |

| \$011          | PSG0H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W   | •       | •       | •       | -       | PSG0[11] | PSG0[10]      | PSG0[9] | PSG0[8]       | 0000       |  |  |

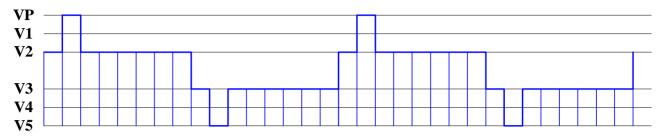

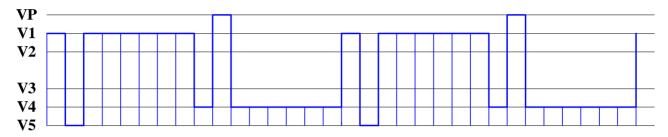

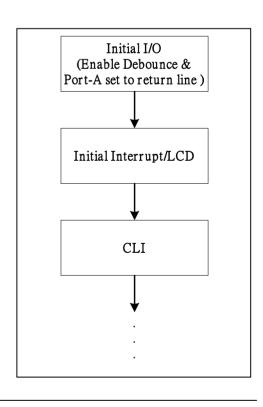

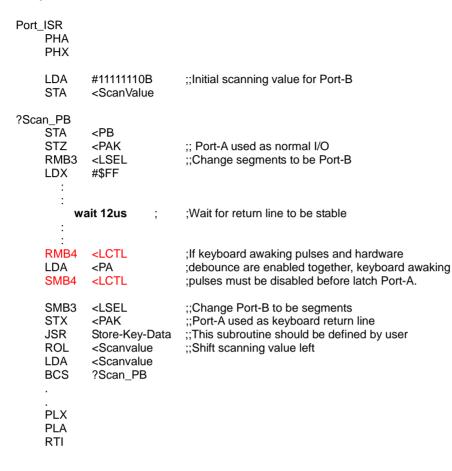

| \$012          | PSG1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W   | PSG1[7] | PSG1[6] | PSG1[5] | PSG1[4] | PSG1[3]  | PSG1[2]       | PSG1[1] | PSG1[0]       | 0000 0000  |  |  |