# S1D15722D01B000 Technical Manual

### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2008, All rights reserved.

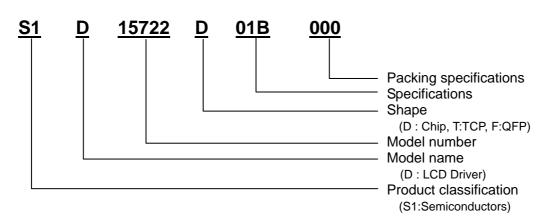

# Configuration of product number

•DEVICES

# **Table of Contents**

| 1. DESCRIPTION                                               | 1  |

|--------------------------------------------------------------|----|

| 2. FEATURES                                                  | 2  |

| 3. BLOCK DIAGRAM                                             | 3  |

| 4. PIN ASSIGNMENT                                            | 4  |

| 4.1 Chip Assignment                                          | 4  |

| 4.2 Alignment mark                                           |    |

| 4.3 Pad Center Coordinates                                   | 5  |

| 5. PIN DESCRIPTION                                           | 9  |

| 5.1 Power Supply Pin                                         |    |

| 5.2 System Bus Connection Pins                               |    |

| 5.3 Display Timing Signal Pins                               |    |

| 5.4 Liquid Crystal Drive Pins<br>5.5 Temperature Sensor Pins |    |

| 5.5 Temperature Sensor Pins                                  |    |

| 6. FUNCTIONAL DESCRIPTION                                    |    |

| 6.1 MPU Interface                                            |    |

| 6.1.1 Selecting Interface Type                               |    |

| 6.1.2 Parallel interface                                     |    |

| 6.1.3 Serial Interface<br>6.1.4 Chip Select                  |    |

| 6.1.5 Accessing Display Data RAM and Internal Register       |    |

| 6.2 Display Data RAM                                         |    |

| 6.2.1 Display Data RAM<br>6.2.2 Gray Scale Display           |    |

| 6.2.3 Page Address Circuit/Column Address Circuit            |    |

| 6.2.4 Line Address Circuit                                   |    |

| 6.2.5 I/O Buffer Circuit<br>6.2.6 Display Data Latch Circuit |    |

| 6.3 Oscillation Circuit                                      |    |

| 6.4 Display Timing Signal Generator                          |    |

| 6.5 Operating State Detector Circuit                         | 21 |

| 6.6 Liquid Crystal Drive Circuit                             |    |

| 6.6.1 Segment Driver<br>6.6.2 Common Driver                  |    |

| 6.7 Temperature Sensor Circuit                               |    |

| 6.7.1 Analog Voltage Output                                  |    |

| 6.7.2 Precautions                                            |    |

| 6.8 Reset Circuit                                            |    |

| 7. COMMAND                                                   |    |

| 7.1 Command Description<br>7.2 Command Table                 |    |

| 7.3 Example of Setting Instructions (Reference Example)      |    |

| 8. ABSOLUTE MAXIMUM RATINGS                                  |    |

| 9. DC CHARACTERISTICS                                        | 52 |

|--------------------------------------------------------------|----|

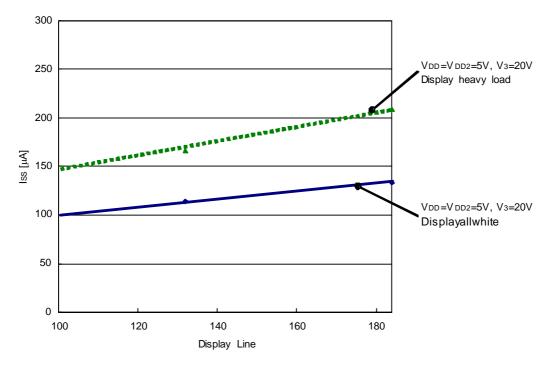

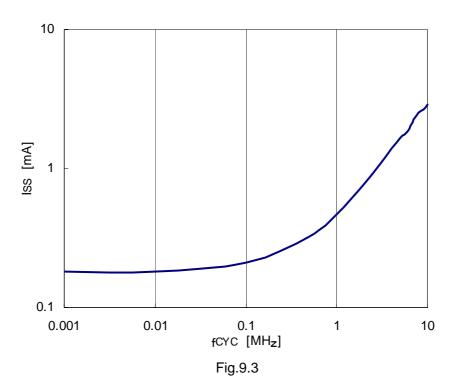

| 9.1 Dynamic Current Consumption Value                        |    |

| 9.1.1 When in normal operation.                              |    |

| 9.2 Current Consumption in the Power-saving Mode             |    |

| 9.3 Reference Data                                           |    |

| 9.3.1 When in normal operation<br>9.3.2 During MPU access    |    |

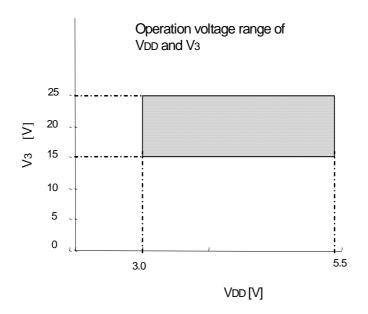

| 9.3.3 Operating Voltage Rage of VDI Series and V3 Series     | 50 |

| 9.3.4 Liquid Crystal Frame Frequency fFR                     |    |

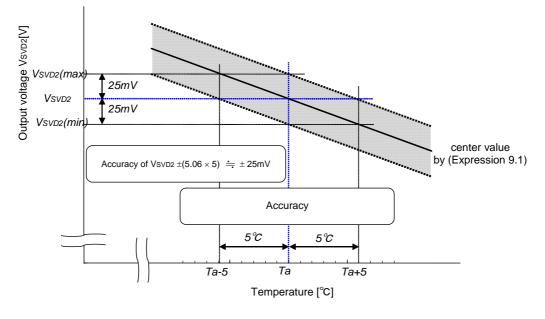

| 9.4 Temperature Sensor Characteristics                       | 58 |

| 9.4.1 Analog Voltage Output Characteristics                  | 58 |

| 10. TIMING CHARACTERISTICS                                   | 59 |

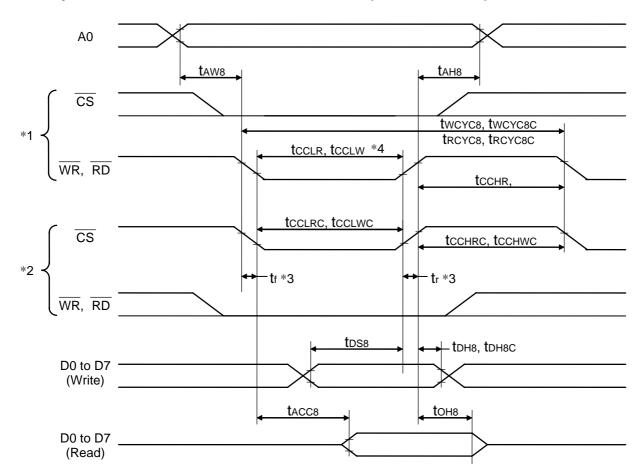

| 10.1 System Bus Read/Write Characteristics 1 (80 Series MPU) | 59 |

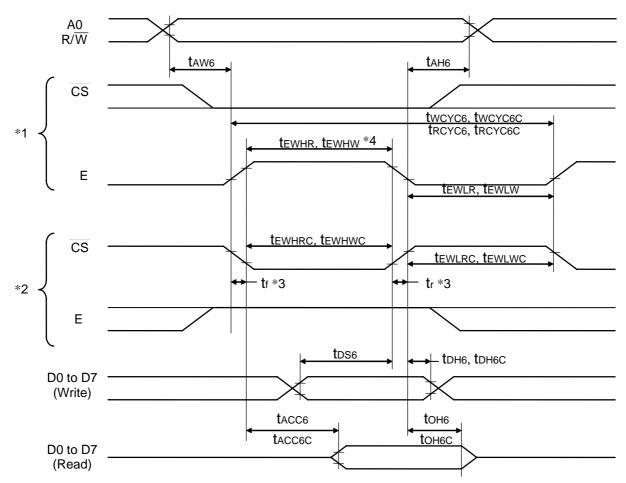

| 10.2 System Bus Read/Write Characteristics 2 (68 Series MPU) | 61 |

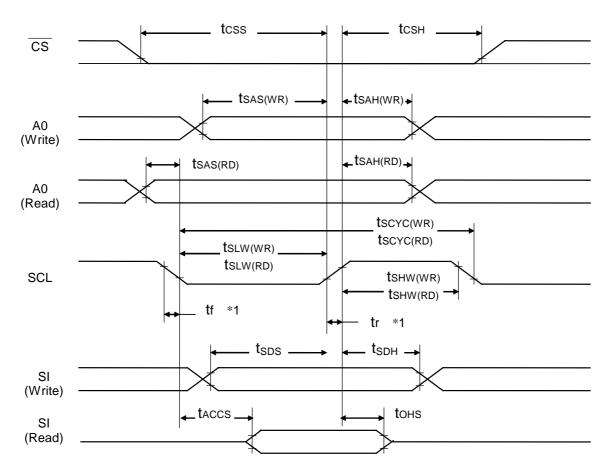

| 10.3 Serial Interface                                        | 63 |

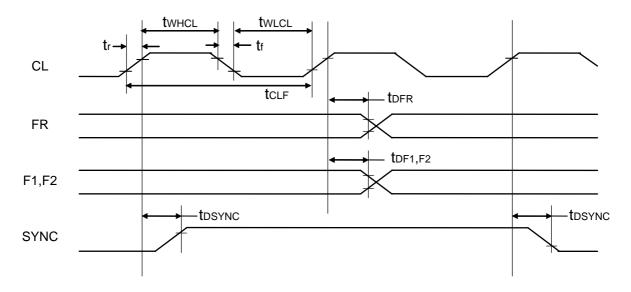

| 10.4 Display Control I/O Timing                              | 64 |

| 10.5 Reset Input Timing                                      | 65 |

| 10.6 Temperature Sensor Measuring Timing                     | 65 |

| 11. POWER CIRCUIT (REFERENCE EXAMPLE)                        | 66 |

| 12. MPU INTERFACE (REFERENCE EXAMPLE)                        | 67 |

| 13. CONNECTION BETWEEN LCD DRIVERS (REFERENCE EXAMPLE)       | 68 |

| 14. LCD PANEL CONNECTION (REFERENCE EXAMPLE)                 | 69 |

| 15. PRECAUTIONS                                              | 70 |

| REVISION HISTORY                                             | 71 |

# **1. DESCRIPTION**

The S1D15722 series is a MLS drive system dot matrix LCD driver that can be directly connected to the microcomputer bus. An 8-bit parallel or serial display data sent from the microcomputer is stored in the built-in display data RAM and LCD drive signal is generated independently of the microcomputer. (Required external LCD bias voltages input.)

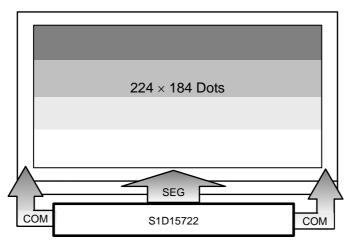

The S1D15722 series provides both FRM 4-grayscale display and binary display. With display data RAM  $224 \times 184 \times 2$  bits incorporated, for 4-grayscale display, 2 bits of built-in RAM correspond to 1 dot of pixel, and for binary display, 1 bit of the built-in RAM corresponds to 1 dot of pixel.

The S1D15722 series contains 184 circuits of common output and 224 circuits of segment output. This allows display of a maximum of  $224 \times 184$  dots per chip.

Read/write operation from microcomputer to display data RAM does not require external operation clock.

# 2. FEATURES

- Direct display of RAM data with display data RAM

- For 4-grayscale display (normally white, normal display mode) RAM bit data (higher and lower)

- (1, 1): Level 3 of gray scale Black

- (1, 0): Level 2 of gray scale

- (0, 1): Level 1 of gray scale

- (0, 0): Level 0 of gray scale White

- For binary display (Normally White, normal display mode)

- RAM bit data

- "1": ON Black

- "0": OFF White

- RAM capacity

- $184 \times 224 \times 2 = 82,432$  bits

- Liquid crystal drive circuit

- 184 common output and 224 segment output

- Provides a high-speed 8-bit MPU interface (can be directly connected to MPU of both 80 and 68 series)/serial interface.

- Extensive command functions

Display lines set, n-line inversion, display data RAM address control, gray scale control, display ON/OFF, display in forward/reverse direction, full display lighting ON/OFF, display clock built-in oscillation circuit control, select common output status, etc.

- Required external LCD bias voltages input

- Built-in high precision voltage adjustment function

Built-in high precision CR oscillation circuit

- Power supply:

Logic power supply : VDD VSSL = 3.0V to 5.5V (Internal logic is operated by VDI-VSSL ··· 2.85V typ.)

LCD drive power supply: V3 VSSH = 15V to 25V

(VSSL = VSSH = GND)

- Wide temperature range: 40 to + $90^{\circ}$ C

- CMOS Process

- Shipping form: bare chip

- No anti-radiation and light resistance design

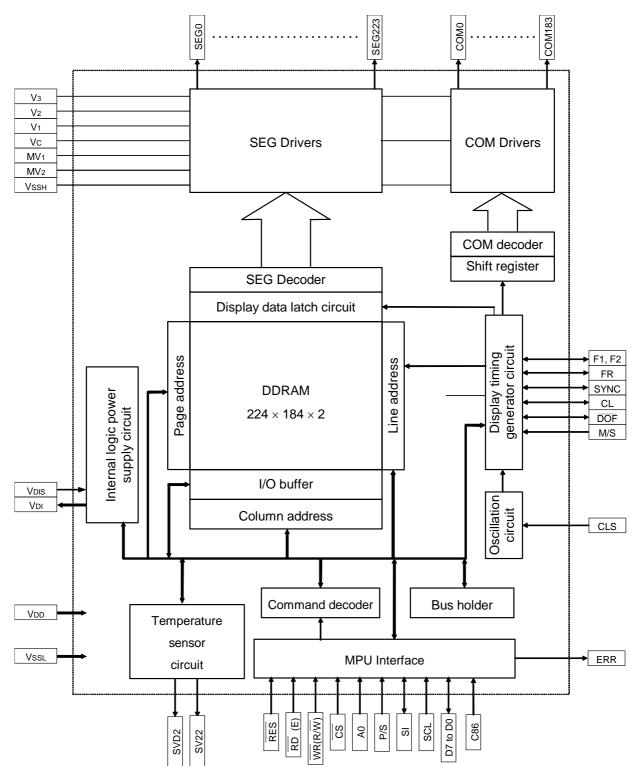

# 3. BLOCK DIAGRAM

# 4. PIN ASSIGNMENT

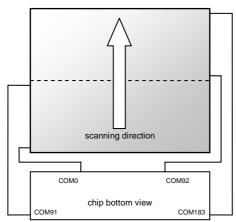

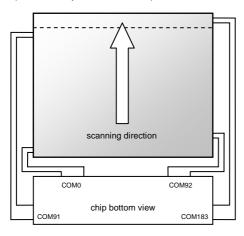

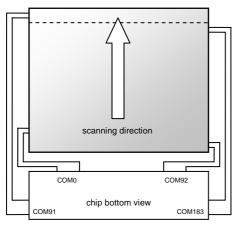

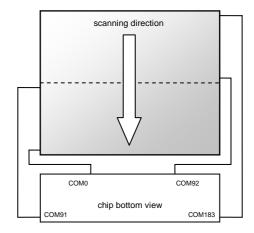

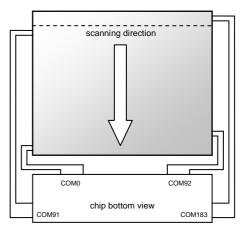

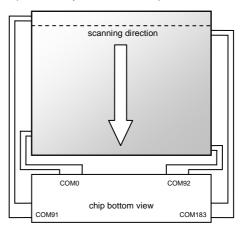

# 4.1 Chip Assignment

| lte       | em                                                           | х        | Size      | Y         | Unit     |

|-----------|--------------------------------------------------------------|----------|-----------|-----------|----------|

| Chip      | o size                                                       | 3.31     | ×         | 21.00     | mm       |

| Chip th   | iickness                                                     |          | 0.625     |           | mm       |

| Bump      | o pitch                                                      |          | 62 (Min.) |           | μm       |

| Bump size | 1 to 5                                                       | 45       | ×         | 85        | μm       |

| PAD No.   | 6 to 17,<br>19 to 44,<br>83,<br>85 to 98<br>18,<br>48 to 82, | 90<br>90 | ×<br>×    | 109<br>60 | μm<br>μm |

|           | 84<br>45 to 47                                               | 90       | ×         | 45        | μm       |

|           | 99 to 153                                                    | 45       | ×         | 85        | μm       |

|           | 154 to 481                                                   | 90       | ×         | 35        | μm       |

|           | 482 to 531                                                   | 45       | ×         | 85        | μm       |

| Bump      | height                                                       |          | Тур. 17   |           | μm       |

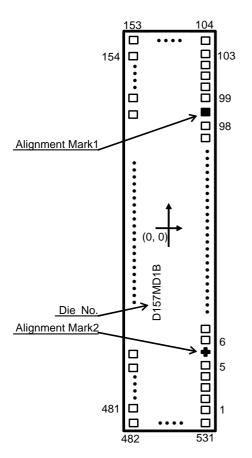

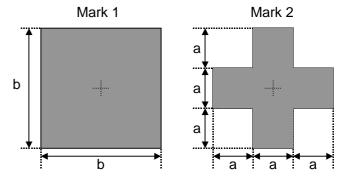

## 4.2 Alignment mark

Alignment coordinate

1

$$(1500.0, 9380.0) \,\mu\text{m}$$

Mark size

$\begin{array}{l} a=15 \ \mu m \\ b=45 \ \mu m \end{array}$

### 4.3 Pad Center Coordinates

| PAD             | Pin            |        |           | PAD | Pin    |     |     |        | PAD        | PIN            |                | nit: |      |

|-----------------|----------------|--------|-----------|-----|--------|-----|-----|--------|------------|----------------|----------------|------|------|

| No.             | Name           | Х      | Y         | No. | Name   | Х   | (   | Y      | No.        | Name           | Х              | ١    | ſ    |

| 1               | NC             | 1539.7 | -10204.05 | 51  | FR     | 151 | 72  | -150.0 | 101        | NC             | 1539.7         | 994  | 6.5  |

| 2               | NC             | 1539.7 | -10075.5  | 52  | CL     |     |     | -60.0  | 102        | NC             | 1539.7         |      | 75.5 |

| 3               | NC             | 1539.7 | -9946.5   | 53  | DOF    |     |     | 210.0  | 103        | NC             | 1539.7         | 102  |      |

| 4               | NC             | 1539.7 | -9817.5   | 54  | F1     |     |     | 300.0  | 104        | NC             | 1519.0         |      | 64.7 |

| 5               | NC             | 1539.7 | -9688.5   | 55  | F2     |     |     | 570.0  | 105        | NC             | 1457.0         | 100  |      |

| 6               | TEST3          | 1517.2 | -9238.5   | 56  | VSSL   |     |     | 660.0  | 105        | COM91          | 1395.0         |      |      |

| 7               | TEST3          | 1317.2 | -9230.5   | 57  |        |     |     | 750.0  | 107        | COM91<br>COM90 | 1333.0         |      |      |

| 8               | TEST4          |        | -8788.5   | 58  | RES    |     |     | 1020.0 | 107        | COM89          | 1271.0         |      |      |

| 9               | TEST4          |        | -8662.5   | 59  | A0     |     |     | 1110.0 | 109        | COM88          | 1209.0         |      |      |

| 10              | TEST5          |        | -8338.5   | 60  | VSSL   |     |     | 1290.0 | 110        | COM87          | 1147.0         |      |      |

| 11              | TEST5          |        | -8212.5   | 61  | WR,R/W |     |     | 1380.0 | 111        | COM86          | 1085.0         |      |      |

| 12              | TEST6          |        | -7888.5   | 62  | RD, E  |     |     | 1650.0 | 112        | COM85          | 1003.0         |      |      |

| 13              | TEST6          |        | -7762.5   | 63  | VDD    |     |     | 1740.0 | 113        | COM84          | 961.0          |      |      |

| 14              | TEST7          |        | -7438.5   | 64  | SI     |     |     | 1830.0 | 114        | COM83          | 899.0          |      |      |

| 14              | TEST7          |        | -7430.5   | 65  | SCL    |     |     | 2100.0 | 115        | COM82          | 837.0          |      |      |

|                 |                |        |           |     | D0     |     |     | 2100.0 |            |                |                |      |      |

| <u>16</u><br>17 | TEST8<br>TEST8 |        | -6988.5   | 66  | D0     |     |     | 2460.0 | 116<br>117 | COM81<br>COM80 | 775.0<br>713.0 |      |      |

|                 |                |        | -6862.5   | 67  |        |     |     |        | -          |                |                |      |      |

| 18              | TEST9          |        | -6530.0   | 68  | D2     |     |     | 2550.0 | 118        | COM79          | 651.0          |      |      |

| 19              | TEST10         |        | -6348.5   | 69  | D3     |     |     | 2820.0 | 119        | COM78          | 589.0          |      |      |

| 20              | TEST10         |        | -6222.5   | 70  | D4     |     |     | 2910.0 | 120        | COM77          | 527.0          |      |      |

| 21              | TEST11         |        | -5898.5   | 71  | D5     |     |     | 3180.0 | 121        | COM76          | 465.0          |      |      |

| 22              | TEST11         |        | -5772.5   | 72  | D6     |     |     | 3270.0 | 122        | COM75          | 403.0          |      |      |

| 23              | TEST12         |        | -5448.5   | 73  | D7     |     |     | 3540.0 | 123        | COM74          | 341.0          |      |      |

| 24              | TEST12         |        | -5322.5   | 74  | VDD    |     |     | 3630.0 | 124        | COM73          | 279.0          |      |      |

| 25              | TEST9          |        | -4998.5   | 75  | M/S    |     |     | 3720.0 | 125        | COM72          | 217.0          |      |      |

| 26              | TEST9          |        | -4872.5   | 76  | CLS    |     |     | 3990.0 | 126        | COM71          | 155.0          |      |      |

| 27              | Vdd2           |        | -4510.7   | 77  | VSSL   |     |     | 4080.0 | 127        | COM70          | 93.0           |      |      |

| 28              | Vdd2           |        | -4384.7   | 78  | TEST   |     |     | 4260.0 | 128        | COM69          | 31.0           |      |      |

| 29              | VDD2           |        | -4258.7   | 79  | C86    |     |     | 4350.0 | 129        | COM68          | -31.0          |      |      |

| 30              | Vdd            |        | -3926.7   | 80  | P/S    |     |     | 4620.0 | 130        | COM67          | -93.0          |      |      |

| 31              | Vdd            |        | -3800.7   | 81  | Vdd    |     |     | 4710.0 | 131        | COM66          | -155.0         |      |      |

| 32              | Vdd            |        | -3674.7   | 82  | ERR    |     |     | 4800.0 | 132        | COM65          | -217.0         |      |      |

| 33              | Vssh           |        | -3362.1   | 83  | Vssh   |     |     | 5051.5 | 133        | COM64          | -279.0         |      |      |

| 34              | Vssh           |        | -3236.1   | 84  | TEST13 |     |     | 5210.0 | 134        | COM63          | -341.0         |      |      |

| 35              | Vssh           |        | -3110.1   | 85  | TEST14 |     |     | 5371.5 | 135        | COM62          | -403.0         |      |      |

| 36              | Vssh           |        | -2984.1   | 86  | TEST15 |     |     | 5701.5 | 136        |                | -465.0         |      |      |

| 37              | Vssl           |        | -2821.1   | 87  | TEST15 |     |     | 5827.5 | 137        | COM60          | -527.0         |      |      |

| 38              | VSSL           |        | -2695.1   | 88  | TEST16 |     |     | 6159.5 | 138        | COM59          | -589.0         |      |      |

| 39              | VSSL           |        | -2569.1   | 89  | TEST16 |     |     | 6285.5 | 139        | COM58          | -651.0         |      |      |

| 40              | Vssl           |        | -2443.1   | 90  | TEST17 |     |     | 6613.5 | 140        | COM57          | -713.0         |      |      |

| 41              | Vdi            |        | -2280.1   | 91  | TEST17 |     |     | 6739.5 | 141        | COM56          | -775.0         |      |      |

| 42              | Vdi            |        | -2154.1   | 92  | V3     |     |     | 7061.5 | 142        | COM55          | -837.0         |      |      |

| 43              | Vdd            |        | -1841.5   | 93  | V2     |     |     | 7405.5 | 143        | COM54          | -899.0         |      |      |

| 44              | Vdd            |        | -1715.5   | 94  | V1     |     |     | 7749.5 | 144        | COM53          | -961.0         |      |      |

| 45              | TEST2          |        | -1440.0   | 95  | Vc     |     |     | 8093.5 | 145        | COM52          | -1023.0        |      |      |

| 46              | SV22           |        | -1050.0   | 96  | MV1    |     |     | 8437.5 | 146        | COM51          | -1085.0        |      |      |

| 47              | SVD2           |        | -800.0    | 97  | MV2    |     |     | 8781.5 | 147        | COM50          | -1147.0        |      |      |

| 48              | Vdis           |        | -600.0    | 98  | Vssн   |     | ,   | 9111.5 | 148        | COM49          | -1209.0        |      |      |

| 49              | Vssl           |        | -510.0    | 99  | NC     | 153 | 9.7 | 9688.5 | 149        | COM48          | -1271.0        |      |      |

| 50              | SYNC           |        | -420.0    | 100 | NC     |     |     | 9817.5 | 150        | COM47          | -1333.0        |      |      |

Unit : µm

| PAD | Pin   |         |         | PAD | Pin   |         |        | PAD | PIN   |         | nit : µm |

|-----|-------|---------|---------|-----|-------|---------|--------|-----|-------|---------|----------|

| No. | Name  | Х       | Y       | No. | Name  | Х       | Y      | No. | Name  | X       | Y        |

| 151 | COM46 | -1395.0 | 10364.7 | 201 | COM0  | -1517.2 | 7223.0 | 251 | SEG45 | -1517.2 | 4123.0   |

| 152 | NC    | -1457.0 |         | 202 | NC    |         | 7161.0 | 252 | SEG46 |         | 4061.0   |

| 153 | NC    | -1519.0 |         | 203 | NC    |         | 7099.0 | 253 | SEG47 |         | 3999.0   |

| 154 | NC    | -1517.2 | 10137.0 | 204 | NC    |         | 7037.0 | 254 | SEG48 |         | 3937.0   |

| 155 | NC    |         | 10075.0 | 205 | NC    |         | 6975.0 | 255 | SEG49 |         | 3875.0   |

| 156 | COM45 |         | 10013.0 | 206 | SEG0  |         | 6913.0 | 256 | SEG50 |         | 3813.0   |

| 157 | COM44 |         | 9951.0  | 207 | SEG1  |         | 6851.0 | 257 | SEG51 |         | 3751.0   |

| 158 | COM43 |         | 9889.0  | 208 | SEG2  |         | 6789.0 | 258 | SEG52 |         | 3689.0   |

| 159 | COM42 |         | 9827.0  | 209 | SEG3  |         | 6727.0 | 259 | SEG53 |         | 3627.0   |

| 160 | COM41 |         | 9765.0  | 210 | SEG4  |         | 6665.0 | 260 | SEG54 |         | 3565.0   |

| 161 | COM40 |         | 9703.0  | 211 | SEG5  |         | 6603.0 | 261 | SEG55 |         | 3503.0   |

| 162 | COM39 |         | 9641.0  | 212 | SEG6  |         | 6541.0 | 262 | SEG56 |         | 3441.0   |

| 163 | COM38 |         | 9579.0  | 213 | SEG7  |         | 6479.0 | 263 | SEG57 |         | 3379.0   |

| 164 | COM37 |         | 9517.0  | 214 | SEG8  |         | 6417.0 | 264 | SEG58 |         | 3317.0   |

| 165 | COM36 |         | 9455.0  | 215 | SEG9  |         | 6355.0 | 265 | SEG59 |         | 3255.0   |

| 166 | COM35 |         | 9393.0  | 216 | SEG10 |         | 6293.0 | 266 | SEG60 |         | 3193.0   |

| 167 | COM34 |         | 9331.0  | 217 | SEG11 |         | 6231.0 | 267 | SEG61 |         | 3131.0   |

| 168 | COM33 |         | 9269.0  | 218 | SEG12 |         | 6169.0 | 268 | SEG62 |         | 3069.0   |

| 169 | COM32 |         | 9207.0  | 219 | SEG13 |         | 6107.0 | 269 | SEG63 |         | 3007.0   |

| 170 | COM31 |         | 9145.0  | 220 | SEG14 |         | 6045.0 | 270 | SEG64 |         | 2945.0   |

| 171 | COM30 |         | 9083.0  | 221 | SEG15 |         | 5983.0 | 271 | SEG65 |         | 2883.0   |

| 172 | COM29 |         | 9021.0  | 222 | SEG16 |         | 5921.0 | 272 | SEG66 |         | 2821.0   |

| 173 | COM28 |         | 8959.0  | 223 | SEG17 |         | 5859.0 | 273 | SEG67 |         | 2759.0   |

| 174 | COM27 |         | 8897.0  | 224 | SEG18 |         | 5797.0 | 274 | SEG68 |         | 2697.0   |

| 175 | COM26 |         | 8835.0  | 225 | SEG19 |         | 5735.0 | 275 | SEG69 |         | 2635.0   |

| 176 | COM25 |         | 8773.0  | 226 | SEG20 |         | 5673.0 | 276 | SEG70 |         | 2573.0   |

| 177 | COM24 |         | 8711.0  | 227 | SEG21 |         | 5611.0 | 277 | SEG71 |         | 2511.0   |

| 178 | COM23 |         | 8649.0  | 228 | SEG22 |         | 5549.0 | 278 | SEG72 |         | 2449.0   |

| 179 | COM22 |         | 8587.0  | 229 | SEG23 |         | 5487.0 | 279 | SEG73 |         | 2387.0   |

| 180 | COM21 |         | 8525.0  | 230 | SEG24 |         | 5425.0 | 280 | SEG74 |         | 2325.0   |

| 181 | COM20 |         | 8463.0  | 231 | SEG25 |         | 5363.0 | 281 | SEG75 |         | 2263.0   |

| 182 | COM19 |         | 8401.0  | 232 | SEG26 |         | 5301.0 | 282 | SEG76 |         | 2201.0   |

| 183 | COM18 |         | 8339.0  | 233 | SEG27 |         | 5239.0 | 283 | SEG77 |         | 2139.0   |

| 184 | COM17 |         | 8277.0  | 234 | SEG28 |         | 5177.0 | 284 | SEG78 |         | 2077.0   |

| 185 | COM16 |         | 8215.0  | 235 | SEG29 |         | 5115.0 | 285 | SEG79 |         | 2015.0   |

| 186 | COM15 |         | 8153.0  | 236 | SEG30 |         | 5053.0 | 286 | SEG80 |         | 1953.0   |

| 187 | COM14 |         | 8091.0  | 237 | SEG31 |         | 4991.0 | 287 | SEG81 |         | 1891.0   |

| 188 | COM13 |         | 8029.0  | 238 | SEG32 |         | 4929.0 | 288 | SEG82 |         | 1829.0   |

| 189 | COM12 |         | 7967.0  | 239 | SEG33 |         | 4867.0 | 289 | SEG83 |         | 1767.0   |

| 190 | COM11 |         | 7905.0  | 240 | SEG34 |         | 4805.0 | 290 | SEG84 |         | 1705.0   |

| 191 | COM10 |         | 7843.0  | 241 | SEG35 |         | 4743.0 | 291 | SEG85 |         | 1643.0   |

| 192 | COM9  |         | 7781.0  | 242 | SEG36 |         | 4681.0 | 292 | SEG86 |         | 1581.0   |

| 193 | COM8  |         | 7719.0  | 243 | SEG37 |         | 4619.0 | 293 | SEG87 |         | 1519.0   |

| 194 | COM7  |         | 7657.0  | 244 | SEG38 |         | 4557.0 | 294 | SEG88 |         | 1457.0   |

| 195 | COM6  |         | 7595.0  | 245 | SEG39 |         | 4495.0 | 295 | SEG89 |         | 1395.0   |

| 196 | COM5  |         | 7533.0  | 246 | SEG40 |         | 4433.0 | 296 | SEG90 |         | 1333.0   |

| 197 | COM4  |         | 7471.0  | 247 | SEG41 |         | 4371.0 | 297 | SEG91 |         | 1271.0   |

| 198 | COM3  |         | 7409.0  | 248 | SEG42 |         | 4309.0 | 298 | SEG92 |         | 1209.0   |

| 199 | COM2  |         | 7347.0  | 249 | SEG43 |         | 4247.0 | 299 | SEG93 |         | 1147.0   |

| 200 | COM1  |         | 7285.0  | 250 | SEG44 |         | 4185.0 | 300 | SEG94 |         | 1085.0   |

### 4. PIN ASSIGNMENT

| PAD Pin v                        | ,    |

|----------------------------------|------|

| No. Name X                       | (    |

| 301 SEG95 -1517.2 102            | 3.0  |

| 302 SEG96 96                     | 1.0  |

| 303 SEG97 899                    | 9.0  |

| 304 SEG98 83                     | 7.0  |

| 305 SEG99 775                    | 5.0  |

| 306 SEG100 713                   | 3.0  |

| 307 SEG101 65                    | 1.0  |

| 308 SEG102 589                   | 9.0  |

| 309 SEG103 52                    | 7.0  |

| 310 SEG104 46                    | 5.0  |

| 311 SEG105 403                   | 3.0  |

| 312 SEG106 34                    |      |

| 313 SEG107 279                   |      |

| 314 SEG108 21                    |      |

| 315 SEG109 155                   |      |

| 316 SEG110 93                    |      |

| 317 SEG111 31                    |      |

| 318 SEG112 -3'                   |      |

| 319 SEG113 -93                   |      |

| 320 SEG114 -15                   |      |

| 321 SEG115 -21                   |      |

| 321 SEG115 -21<br>322 SEG116 -27 |      |

| 323 SEG117 -34                   |      |

| 324 SEG118 -40                   |      |

|                                  |      |

| 325 SEG119 -46                   |      |

| 326 SEG120 -52                   |      |

| 327 SEG121 -58                   |      |

| 328 SEG122 -65                   |      |

| 329 SEG123 -71                   |      |

| 330 SEG124 -77                   |      |

| 331 SEG125 -83                   |      |

| 332 SEG126 -89                   |      |

| 333 SEG127 -96                   |      |

| 334 SEG128 -102                  |      |

| 335 SEG129 -108                  |      |

| 336 SEG130 -114                  |      |

| 337 SEG131 -120                  |      |

| 338 SEG132 -127                  |      |

| 339 SEG133 -133                  |      |

| 340 SEG134 -139                  |      |

| 341 SEG135 -145                  |      |

| 342 SEG136 -151                  | 19.0 |

| 343 SEG137 -158                  | 31.0 |

| 344 SEG138 -164                  | 43.0 |

| 345 SEG139 -170                  | )5.0 |

| 346 SEG140 -176                  | 67.0 |

| 347 SEG141 -182                  | 29.0 |

| 348 SEG142 -189                  | 91.0 |

| 349 SEG143 -195                  | 53.0 |

|                                  |      |

| PAD | Pin    |         |         |

|-----|--------|---------|---------|

| No. | Name   | Х       | Y       |

| 351 | SEG145 | -1517.2 | -2077.0 |

| 352 | SEG146 |         | -2139.0 |

| 353 | SEG147 |         | -2201.0 |

| 354 | SEG148 |         | -2263.0 |

| 355 | SEG149 |         | -2325.0 |

| 356 | SEG150 |         | -2387.0 |

| 357 | SEG151 |         | -2449.0 |

| 358 | SEG152 |         | -2511.0 |

| 359 | SEG153 |         | -2573.0 |

| 360 | SEG154 |         | -2635.0 |

| 361 | SEG155 |         | -2697.0 |

| 362 | SEG156 |         | -2759.0 |

| 363 | SEG157 |         | -2821.0 |

| 364 | SEG158 |         | -2883.0 |

| 365 | SEG159 |         | -2945.0 |

| 366 | SEG160 |         | -3007.0 |

| 367 | SEG161 |         | -3069.0 |

| 368 | SEG162 |         | -3131.0 |

| 369 | SEG163 |         | -3193.0 |

| 370 | SEG164 |         | -3255.0 |

| 371 | SEG165 |         | -3317.0 |

| 372 | SEG166 |         | -3379.0 |

| 373 | SEG167 |         | -3441.0 |

| 374 | SEG168 |         | -3503.0 |

| 375 | SEG169 |         | -3565.0 |

| 376 | SEG170 |         | -3627.0 |

| 377 | SEG171 |         | -3689.0 |

| 378 | SEG172 |         | -3751.0 |

| 379 | SEG173 |         | -3813.0 |

| 380 | SEG174 |         | -3875.0 |

| 381 | SEG175 |         | -3937.0 |

| 382 | SEG176 |         | -3999.0 |

| 383 | SEG177 |         | -4061.0 |

| 384 | SEG178 |         | -4123.0 |

| 385 | SEG179 |         | -4185.0 |

| 386 | SEG180 |         | -4247.0 |

| 387 | SEG181 |         | -4309.0 |

| 388 | SEG182 |         | -4371.0 |

| 389 | SEG183 |         | -4433.0 |

| 390 | SEG184 |         | -4495.0 |

| 391 | SEG185 |         | -4557.0 |

| 392 | SEG186 |         | -4619.0 |

| 393 | SEG187 |         | -4681.0 |

| 394 | SEG188 |         | -4743.0 |

| 395 | SEG189 |         | -4805.0 |

| 396 | SEG190 |         | -4867.0 |

| 397 | SEG191 |         | -4929.0 |

| 398 | SEG192 |         | -4991.0 |

| 399 | SEG193 |         | -5053.0 |

| 400 | SEG194 |         | -5115.0 |

|     |        |         |         |

|            | -                | Unit : μm        |      |         |  |  |

|------------|------------------|------------------|------|---------|--|--|

| PAD<br>No. | PIN<br>Name      | )                | (    | Y       |  |  |

| 401        | SEG195           | -15 <sup>-</sup> | 17.2 | -5177.0 |  |  |

| 402        | SEG196           |                  |      | -5239.0 |  |  |

| 403        | SEG197           |                  |      | -5301.0 |  |  |

| 404        | SEG198           |                  |      | -5363.0 |  |  |

| 405        | SEG199           |                  |      | -5425.0 |  |  |

| 406        | SEG200           |                  |      | -5487.0 |  |  |

| 407        | SEG201           |                  |      | -5549.0 |  |  |

| 408        | SEG202           |                  |      | -5611.0 |  |  |

| 409        | SEG203           |                  |      | -5673.0 |  |  |

| 410        | SEG204           |                  |      | -5735.0 |  |  |

| 411        | SEG205           |                  |      | -5797.0 |  |  |

| 412        | SEG206           |                  |      | -5859.0 |  |  |

| 413        | SEG207           |                  |      | -5921.0 |  |  |

| 414        | SEG208           |                  |      | -5983.0 |  |  |

| 415        | SEG209           |                  |      | -6045.0 |  |  |

| 416        | SEG210           |                  |      | -6107.0 |  |  |

| 417        | SEG211           |                  |      | -6169.0 |  |  |

| 418        | SEG212           |                  |      | -6231.0 |  |  |

| 419        | SEG212           |                  |      | -6293.0 |  |  |

| 420        | SEG213           |                  |      | -6355.0 |  |  |

| 420        | SEG214<br>SEG215 |                  |      | -6417.0 |  |  |

| 421        | SEG215<br>SEG216 |                  |      | -6479.0 |  |  |

| 422        | SEG210<br>SEG217 |                  |      | -6541.0 |  |  |

| 423        |                  |                  |      |         |  |  |

|            | SEG218           |                  |      | -6603.0 |  |  |

| 425        | SEG219           |                  |      | -6665.0 |  |  |

| 426        | SEG220           |                  |      | -6727.0 |  |  |

| 427        | SEG221           |                  |      | -6789.0 |  |  |

| 428        | SEG222           |                  |      | -6851.0 |  |  |

| 429        | SEG223           |                  |      | -6913.0 |  |  |

| 430        | NC               |                  |      | -6975.0 |  |  |

| 431        | NC               |                  |      | -7037.0 |  |  |

| 432        | NC               |                  |      | -7099.0 |  |  |

| 433        | NC               |                  |      | -7161.0 |  |  |

| 434        | COM92            |                  |      | -7223.0 |  |  |

| 435        | COM93            |                  |      | -7285.0 |  |  |

| 436        | COM94            |                  |      | -7347.0 |  |  |

| 437        | COM95            |                  |      | -7409.0 |  |  |

| 438        | COM96            |                  |      | -7471.0 |  |  |

| 439        | COM97            |                  |      | -7533.0 |  |  |

| 440        | COM98            |                  |      | -7595.0 |  |  |

| 441        | COM99            |                  |      | -7657.0 |  |  |

| 442        | COM100           |                  |      | -7719.0 |  |  |

| 443        | COM101           |                  |      | -7781.0 |  |  |

| 444        | COM102           |                  |      | -7843.0 |  |  |

| 445        | COM103           |                  |      | -7905.0 |  |  |

| 446        | COM104           |                  |      | -7967.0 |  |  |

| 447        | COM105           |                  |      | -8029.0 |  |  |

| 448        | COM106           |                  |      | -8091.0 |  |  |

| 449        | COM107           |                  |      | -8153.0 |  |  |

| 450        | COM108           |                  | ,    | -8215.0 |  |  |

| PAD        | Pin              | V       | V        |  |

|------------|------------------|---------|----------|--|

| No.        | Name             | X       | Y        |  |

| 451        | COM109           | -1517.2 | -8277.0  |  |

| 452        | COM110           |         | -8339.0  |  |

| 453        | COM111           |         | -8401.0  |  |

| 454        | COM112           |         | -8463.0  |  |

| 455        | COM113           |         | -8525.0  |  |

| 456        | COM114           |         | -8587.0  |  |

| 457        | COM115           |         | -8649.0  |  |

| 458        | COM116           |         | -8711.0  |  |

| 459        | COM117           |         | -8773.0  |  |

| 460        | COM118           |         | -8835.0  |  |

| 461        | COM119           |         | -8897.0  |  |

| 462        | COM120           |         | -8959.0  |  |

| 463        | COM121           |         | -9021.0  |  |

| 464        | COM122           |         | -9083.0  |  |

| 465        | COM123           |         | -9145.0  |  |

| 466        | COM124           |         | -9207.0  |  |

| 467        | COM125           |         | -9269.0  |  |

| 468        | COM126           |         | -9331.0  |  |

| 469        | COM127           |         | -9393.0  |  |

| 470        | COM128           |         | -9455.0  |  |

| 471        | COM129           |         | -9517.0  |  |

| 472        | COM130           |         | -9579.0  |  |

| 473        | COM131           |         | -9641.0  |  |

| 474        | COM132           |         | -9703.0  |  |

| 475        | COM133           |         | -9765.0  |  |

| 476        | COM134           |         | -9827.0  |  |

| 477        | COM135           |         | -9889.0  |  |

| 478        | COM136           |         | -9951.0  |  |

| 479        | COM137           |         | -10013.0 |  |

| 480        | NC               |         | -10075.0 |  |

| 481        | NC               |         | -10137.0 |  |

| 482        | NC               | -1519.0 | -10364.7 |  |

| 483        | NC               | -1457.0 | 10001.7  |  |

| 484        | COM138           | -1395.0 |          |  |

| 485        | COM139           | -1333.0 |          |  |

| 486        | COM140           | -1271.0 |          |  |

| 487        | COM140           | -1209.0 |          |  |

| 488        | COM142           | -1147.0 |          |  |

| 489        | COM143           | -1085.0 |          |  |

| 490        | COM143           | -1023.0 |          |  |

| 491        | COM145           | -961.0  |          |  |

| 492        | COM145<br>COM146 | -899.0  |          |  |

| 492        | COM140<br>COM147 | -837.0  |          |  |

| 493        | COM147<br>COM148 | -775.0  |          |  |

| 494<br>495 | COM148<br>COM149 |         |          |  |

|            |                  | -713.0  |          |  |

| 496        | COM150           | -651.0  |          |  |

| 497        | COM151           | -589.0  |          |  |

| 498        | COM152           | -527.0  |          |  |

| 499        | COM153           | -465.0  |          |  |

| 500        | COM154           | -403.0  | ¥        |  |

|     |        |        | Unit : µm |

|-----|--------|--------|-----------|

| PAD | Pin    | х      | Y         |

| No. | Name   |        | -         |

| 501 | COM155 | -341.0 | -10364.7  |

| 502 | COM156 | -279.0 |           |

| 503 | COM157 | -217.0 |           |

| 504 | COM158 | -155.0 |           |

| 505 | COM159 | -93.0  |           |

| 506 | COM160 | -31.0  |           |

| 507 | COM161 | 31.0   |           |

| 508 | COM162 | 93.0   |           |

| 509 | COM163 | 155.0  |           |

| 510 | COM164 | 217.0  |           |

| 511 | COM165 | 279.0  |           |

| 512 | COM166 | 341.0  |           |

| 513 | COM167 | 403.0  |           |

| 514 | COM168 | 465.0  |           |

| 515 | COM169 | 527.0  |           |

| 516 | COM170 | 589.0  |           |

| 517 | COM171 | 651.0  |           |

| 518 | COM172 | 713.0  |           |

| 519 | COM173 | 775.0  |           |

| 520 | COM174 | 837.0  |           |

| 521 | COM175 | 899.0  |           |

| 522 | COM176 | 961.0  |           |

| 523 | COM177 | 1023.0 |           |

| 524 | COM178 | 1085.0 |           |

| 525 | COM179 | 1147.0 |           |

| 526 | COM180 | 1209.0 |           |

| 527 | COM181 | 1271.0 |           |

| 528 | COM182 | 1333.0 |           |

| 529 | COM183 | 1395.0 |           |

| 530 | NC     | 1457.0 |           |

| 531 | NC     | 1519.0 | <b>v</b>  |

# 5. PIN DESCRIPTION

# 5.1 Power Supply Pin

| Pin name                       | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Number of<br>pins |  |  |  |  |  |

|--------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|--|

| Vdd                            | Power supply    | C system power supply. Also, use this pin together with the MPU power supply<br>bin Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |  |  |  |  |  |

| Vdd2                           | Power<br>supply | Connect to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                 |  |  |  |  |  |

| VSSL                           | Power<br>supply | 0V pin connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                 |  |  |  |  |  |

| Vssh                           | Power<br>supply | High-voltage resistance circuit negative power supply pin. Short-circuit to VssL outside the LCD module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                 |  |  |  |  |  |

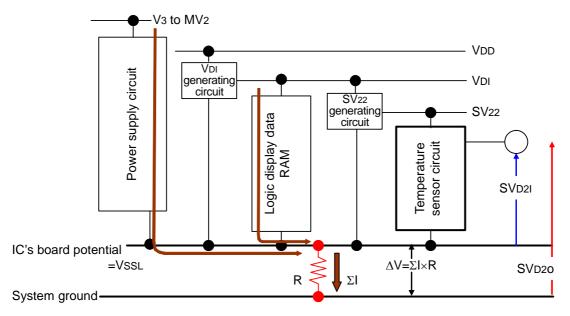

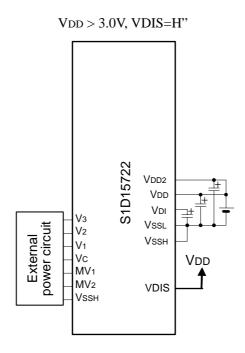

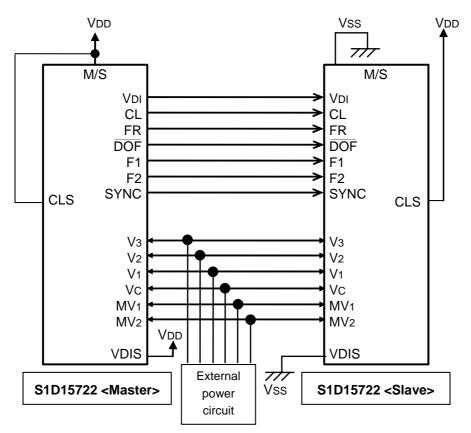

| Vdi                            | Power<br>supply | Power supply pin for internal circuit. It is made from VDD.<br>This pin is required to connect external capacitance between this pin and Vss to<br>stabilize the voltage.<br>The VDI generator can select valid/invalid by VDIS pin.<br>For single chip usage, the VDI generator must be ON (VDIS = HIGH).<br>Prohibit to supply VDI externally.<br>For multi chip usage, each VDI of chips are must be same, therefore set master's<br>VDIS = HIGH and slave's VDIS = LOW to supply VDI voltage from master chip to<br>slave chip(s).                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                 |  |  |  |  |  |

| Vdis                           | I               | This pin is used for making the VDI generating circuit valid or invalid.VDIS = HIGH: The VDI generating circuit is valid. (Master chip)VDIS = LOW: The VDI generating circuit is invalid. (Slave chip)When the VDIS pin is used by changing from LOW to HIGH, it should be initialized<br>by the pin after changing it.Only the VDIS pin controls operation of the VDI generating circuit and the circuit<br>operates independently of the save power command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |  |  |  |  |  |

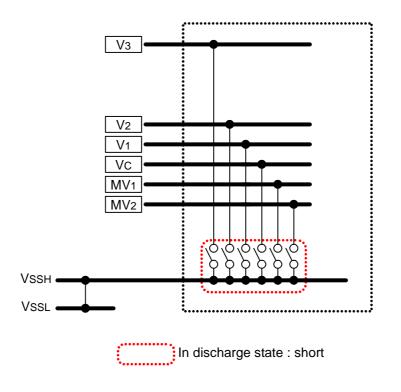

| V3, V2,<br>V1, VC,<br>MV1, MV2 | Power<br>supply | Multi-level, liquid crystal drive power supply pins. The voltage specified according to liquid crystal cells is impedance-converted by a split resistor or operational amplifier and applied.<br>The following magnitude correlation should be followed:<br>$V_3 \ge V_2 \ge V_1 \ge V_C \ge MV 1 \ge MV_2 \ge V_{SSH}$ (=VSSL)<br>The following voltages are example in case of Bias 1/13 to 8. Input externally symmetrical voltages against VC.<br><u>Bias 1/13 1/12 1/11 1/10 1/9 1/8</u><br>$V_2 \ 8.5/13 \cdot V_3 \ 8/12 \cdot V_3 \ 7.5/11 \cdot V_3 \ 7/10 \cdot V_3 \ 6.5/9 \cdot V_3 \ 6/8 \cdot V_3$<br>$V_1 \ 7.5/13 \cdot V_3 \ 7/12 \cdot V_3 \ 6.5/11 \cdot V_3 \ 6/10 \cdot V_3 \ 5.5/9 \cdot V_3 \ 5/8 \cdot V_3$<br>$V_C \ 6.5/13 \cdot V_3 \ 6/12 \cdot V_3 \ 5.511 \cdot V_3 \ 5/10 \cdot V_3 \ 4.5/9 \cdot V_3 \ 4/8 \cdot V_3$<br>$MV_1 \ 5.5/13 \cdot V_3 \ 5/12 \cdot V_3 \ 4.5/11 \cdot V_3 \ 3/10 \cdot V_3 \ 2.5/9 \cdot V_3 \ 2/8 \cdot V_3$ | each 1            |  |  |  |  |  |

## 5.2 System Bus Connection Pins

| Pin name    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Number of<br>pins |  |  |  |  |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| D7 to D0    | I/O | 8-bit bi-directional data bus; connected to the standard 8-bit or 16-bit MPU data bus.<br>When serial interface is selected ( $P/S = LOW$ ), if chip select is inactive or the state of operation is other than reading or writing, D0 to D7 are set to High-impedance (Hi-Z).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |  |  |  |  |

| SI          | I/O | Serial data input/output pin when the serial interface is selected ( $P/S = LOW$ ) When serial interface is selected, read status is enabled, but read display data RAM is not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                 |  |  |  |  |

| SCL         | Ι   | Serial clock input pin when serial interface is selected ( $P/S = LOW$ ). Data is read at the rising edge of clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                 |  |  |  |  |

| A0          | I   | The least significant bit (LSB) of the standard MPU address bus is connected and a distinction is made between data and command.<br>A0 = HIGH : D0 to D7 is display data or command parameter.<br>A0 = LOW : D0 to D7 is control command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                 |  |  |  |  |

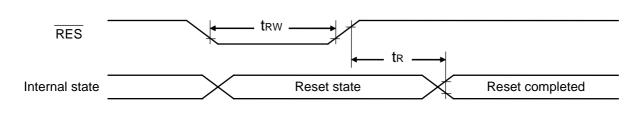

| RES         | I   | Setting RES to LOW resets the device.<br>Reset operation depends on the signal level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                 |  |  |  |  |

| CS          | I   | Chip select signal Active when $\overline{CS}$ = LOW, enabling input or output of data/command. When $\overline{CS}$ = HIGH, data bus are set to Hi-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                 |  |  |  |  |

| RD<br>(E)   | I   | <ul> <li>When MPU of the 80 series is connected. Active LOW         This pin connects RD signal of 80 series MPU. Data bus enters a state of         output while this signal is set to LOW.     </li> <li>When MPU of the 68 series is connected. Active HIGH</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |  |  |  |  |

| WR<br>(R/W) | I   | <ul> <li>Becomes enable clock input pin of the 68 series MPU.</li> <li>When MPU of the 80 series is connected. Active LOW This pin connects the 80 series MPU signal. Signals on the data bus are latched at the trailing edge of Signal WR.</li> <li>When the 68 series MPU is connected: Becomes input pin of read/write control signal. R/W = HIGH : Read R/W = HIGH : Read</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |                   |  |  |  |  |

| P/S         | Ι   | $R/W$ = LOW : Write         Select pin between parallel interface and serial interface $P/S$ = HIGH : Parallel interface $P/S$ = LOW : Serial Interface:         Sets as shown in the table below depending on the state of P/S. $P/S$ Data/Command Data Read/Write Serial clock         HIGH       A0         D0 to D7 $\overline{RD}$ , $\overline{WR}$ LOW       A0         SI       Write         Read status         When P/S = LOW, D0 to D7 are Hi-Z. For D0 to D7, it may be set to HIGH, LOW         or open.       However, set $\overline{RD}(E)$ and $\overline{WR}$ ( $R/\overline{W}$ ) to HIGH or LOW.         When serial interface is selected, read status is enabled, but read display data         RAM is not enabled. |                   |  |  |  |  |

| Pin name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |  |  |  |  |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| C86      | Ι   | Pin for switching MPU interface.<br>C86 = HIGH : 68 series MPU interface<br>C86 = LOW : 80 series MPU interface<br>When serial interface is selected, set to LOW.                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 |  |  |  |  |

| ERR      | 0   | <ul> <li>Pin for monitoring the operating state of IC.</li> <li>ERR = LOW : Normal operating state</li> <li>ERR = HIGH : Initial state or error detection</li> <li>Becomes ERR = HIGH in the initial state following resetting.</li> <li>Becomes ERR = LOW after resetting.</li> <li>If a bit-flip occurs in the register which is part of internal logic because of external noise or similar reason, becomes ERR = HIGH. When ERR = HIGH, re-write all commands. After resetting, returns to WRR = LOW. At this time it is also recommended to re-write data to display data RAM.</li> </ul> |   |  |  |  |  |

# 5.3 Display Timing Signal Pins

| Pin name | I/O |                                                                                                                                                                                                                                                                                                                                                                                     |                                                |                                                               | Description                                                                                                                               |                          |       |  |  |  |  |  |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|--|--|--|--|--|

|          |     | Pin for selecting master/slave operation.<br>Master operation outputs timing signal required for LCD display and slave<br>operation inputs timing signal required for LCD display. This causes<br>synchronization in LCD display system.<br>M/S = HIGH : Master operation<br>M/S = LOW : Slave operation<br>Sets as shown in the table below depending on the state of M/S and CLS. |                                                |                                                               |                                                                                                                                           |                          |       |  |  |  |  |  |

| M/S      | I   | M/S                                                                                                                                                                                                                                                                                                                                                                                 |                                                | cillation                                                     | CL                                                                                                                                        | FR, DOF,<br>F1, F2, SYNC | 1     |  |  |  |  |  |

|          |     | HIGH                                                                                                                                                                                                                                                                                                                                                                                | -                                              | nabled                                                        | Output                                                                                                                                    | Output                   |       |  |  |  |  |  |

|          |     |                                                                                                                                                                                                                                                                                                                                                                                     | -                                              | isabled                                                       | Input                                                                                                                                     | Output                   |       |  |  |  |  |  |

|          |     |                                                                                                                                                                                                                                                                                                                                                                                     | LOW                                            | -                                                             | isabled                                                                                                                                   | Input                    | Input |  |  |  |  |  |

|          |     |                                                                                                                                                                                                                                                                                                                                                                                     | LOW D                                          | isabled                                                       | Input                                                                                                                                     | Input                    |       |  |  |  |  |  |

| CLS      | I   | CLS = H<br>CLS = LC<br>When CLS                                                                                                                                                                                                                                                                                                                                                     | IGH : Built-in<br>DW : Built-in<br>= LOW, disp | oscillation<br>oscillation o<br>lay clock is<br>r or slave, s | t-in oscillation circuit fo<br>circuit enabled<br>sircuit disabled (externa<br>input from the CL pin.<br>et each CLS pin to the<br>Master | al input)                | 1     |  |  |  |  |  |

|          |     | Use o                                                                                                                                                                                                                                                                                                                                                                               | f built-in osci                                |                                                               |                                                                                                                                           | HIGH                     |       |  |  |  |  |  |

|          |     |                                                                                                                                                                                                                                                                                                                                                                                     |                                                | External in                                                   |                                                                                                                                           | LOW                      | LOW   |  |  |  |  |  |

| CL       | I/O | Display clock input/output pin.     Sets as shown in the table below depending on the state of M/S and CLS.       M/S     CLS     CL       HIGH     HIGH     Output       LOW     Input       LOW     HIGH       LOW     Input       To use this IC on master/slave, connect each CL pin.                                                                                           |                                                |                                                               |                                                                                                                                           |                          | 1     |  |  |  |  |  |

### **5. PIN DESCRIPTION**

| Pin name        | I/O | Description                                                                                                                                                             | Number of<br>pins |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| FR              | I/O | Liquid crystal alternating-current signal input/output pin.<br>M/S = HIGH : Output<br>M/S = LOW : Input<br>To use this IC on master/slave, connect each FR pin.         | 1                 |

| F1, F2,<br>SYNC | I/O | Liquid crystal synchronization signal input/output pin.<br>M/S = HIGH : Output<br>M/S = LOW : Input<br>To use this IC on master/slave, connect each F1, F2 or SYNC pin. | 1 for each        |

| DOF             | I/O | Pin for controlling blanking of liquid crystal display.<br>M/S = HIGH : Output<br>M/S = LOW : Input<br>To use this IC on master/slave, connect each DOF pin.            | 1                 |

# 5.4 Liquid Crystal Drive Pins

| Pin name          | I/O | Description                                                                                                                                                 |              |  |  |  |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|

| SEG0 to<br>SEG223 | 0   | Liquid crystal segment drive output pin. One level is selected from V2, V1, Vc, MV1, and MV2 by combining display RAM and FR, F1 and F2 signals.            | 224 in total |  |  |  |

| COM0 to<br>COM183 | 0   | Liquid crystal common drive output pin. One level is selected from V <sub>3</sub> , Vc, and VssL (= VssL) by combining scan data and FR, F1 and F2 signals. | 184 in total |  |  |  |

# 5.5 Temperature Sensor Pins

| Pin name | I/O | Description                                       | Number of<br>pins |

|----------|-----|---------------------------------------------------|-------------------|

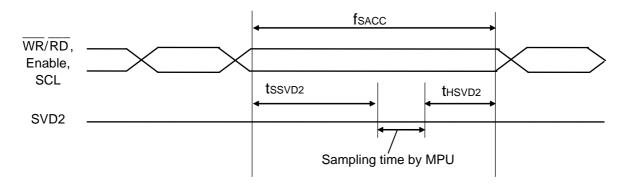

| SVD2     | 0   | Temperature sensor analog voltage output pin.     | 1                 |

| SV22     | 0   | Pin for testing temperature sensor. Sets to open. | 1                 |

### 5.6 Test Pins

| Pin name           | I/O | Description                           | Number of<br>pins |

|--------------------|-----|---------------------------------------|-------------------|

| TEST               | I   | Pin for testing IC chip. Set to LOW.  | 1                 |

| TEST2              | 0   | Pin for testing IC chip. Set to open. | 1                 |

| TEST3 to<br>TEST17 | Ι   | Pin for testing IC chip. Set to open. | 1                 |

# 6. FUNCTIONAL DESCRIPTION

### 6.1 MPU Interface

#### 6.1.1 Selecting Interface Type

This IC allows data transfer through 8-bit bi-directional data bus (D7 to D0) or serial data input (SI). Selecting HIGH or LOW for polarity of P/S pin allows selection of 8-bit parallel data input or serial data input as shown in Table 6.1.

#### Table 6.1

| P/S                   | CS | A0 | RD | WR | C86 | SI | SCL | D7~D0 |

|-----------------------|----|----|----|----|-----|----|-----|-------|

| HIGH : Parallel input | CS | A0 | RD | WR | C86 | _  | _   | D7~D0 |

| LOW : Serial input    | CS | A0 | _  | _  | —   | SI | SCL | (HZ)  |

— : Set - to HIGH or LOW. HZ is in the state of high impedance.

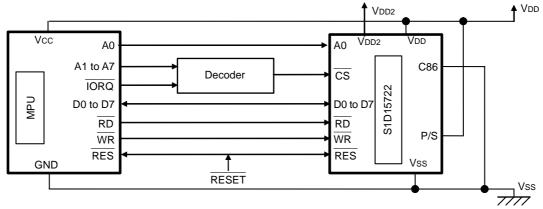

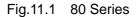

#### 6.1.2 Parallel interface

When parallel interface is selected (P/S = HIGH), setting the C86 pin to HIGH or LOW allows direct connection to the MPU bus of either 80 series or 68 series as shown in Table 6.2.

#### Table 6.2

| C86                      | CS | A0 | RD | WR  | D7~D0 |

|--------------------------|----|----|----|-----|-------|

| HIGH : 68 series MPU bus | CS | A0 | E  | R/W | D7~D0 |

| LOW : 80 series MPU bus  |    | A0 | RD | WR  | D7~D0 |

Data bus signal is identified by combination of A0,  $\overline{RD}(E)$  and  $\overline{WR}(R/\overline{W})$  as shown in Table 6.3.

#### Table 6.3

| Common | 68 series |    |    | Function                                       |  |

|--------|-----------|----|----|------------------------------------------------|--|

| A0     | R/W       | RD | WR | Function                                       |  |

| 1      | 1         | 0  | 1  | Display data reading, reads status.            |  |

| 1      | 0         | 1  | 0  | Status data writing, writes command parameter. |  |

| 0      | 0         | 1  | 0  | Writes a command.                              |  |

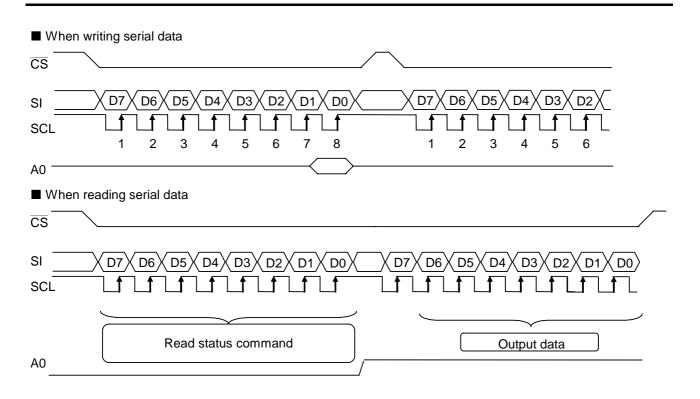

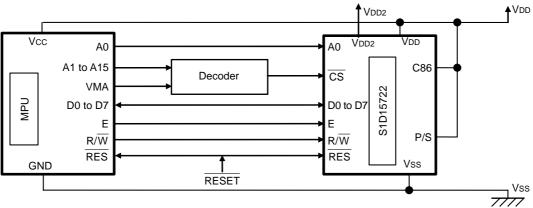

#### 6.1.3 Serial Interface

When serial interface is selected (P/S = LOW), the chip is active ( $\overline{CS} = LOW$ ) and can accept serial data input (SI) and serial clock input (SCL). Serial interface is comprised of an 8-bit shift register and 3-bit counter. Serial data is captured from serial data input pin in order from D7, D6 to D0 on the rising edge of the serial clock and converted into 8-bit parallel data on the rising edge of the 8th serial clock and then processed.

Whether serial data input is display data, command parameter or command is determined by A0 input. For A0 = HIGH, display data or command parameter, for A0 = LOW, command. A0 input is read and determined on the 8xn-th rising edge of the serial clock after the chip goes into the active state.

Using the status read command enables read status and read data, respectively, even when serial interface is selected. However, it should be noted that the  $\overline{CS}$  signal is handled differently from the time of serial data input. Read from display data RAM is not enabled. Signal chart of serial interface is shown in Fig.6.1.

### **6. FUNCTIONAL DESCRIPTION**

Fig.6.1 Signal Chart of Serial Interface

- \* When the chip is inactive, the counter is reset to the initial state. Continuous serial clock input is possible, however, it is recommended to clear the counter by setting  $\overline{CS}$  = HIGH for every 8 bits of serial clock at the time of serial data input so that malfunction caused by external noise can be prevented. When reading serial data, continuously read data by entering serial clock from the SCL pin with the setting left  $\overline{CS}$  = LOW instead of setting  $\overline{CS}$  = HIGH after the read command. After getting the read data, to set  $\overline{CS}$  = HIGH is necessary.

- \* For serial interface, read from display data RAM is not enabled.

- \* For SCL signal, great care should be taken for wiring termination reflection and external noise. It is recommended to check operation using the actual equipment.

#### 6.1.4 Chip Select

Since this IC has chip select pin, parallel interface or serial interface is enabled when  $\overline{CS} = LOW$  is set. When the chip select is inactive, D0 to D7 are in the state of high impedance and input of A0,  $\overline{RD}$ ,  $\overline{WR}$ , SI, and SCL is disabled. When serial interface is selected, shift register and counter are reset.

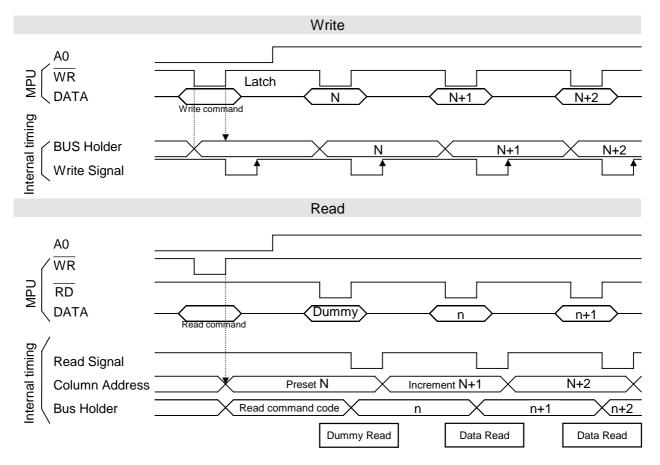

#### 6.1.5 Accessing Display Data RAM and Internal Register

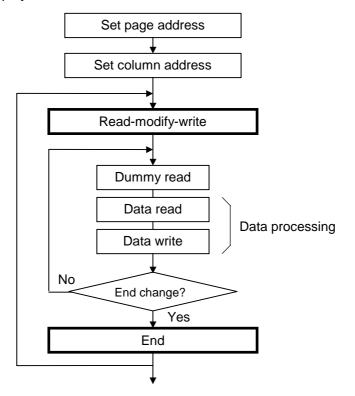

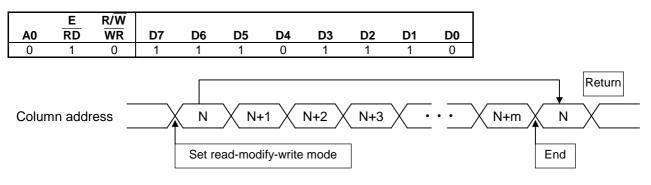

Since this IC is accessed as a kind of pipeline processing between LSIs via bus holder coming with internal data bus, wait time is not necessary if the cycle time is satisfied, enabling high-speed data transmission.

For example, if MPU writes data to display data RAM, data is temporarily held in the bus holder and written to the display data RAM by the next data write cycle. When MPU reads display data RAM, read data is held in the bus holder in the first data read cycle (dummy) and read on the system bus from the bus holder in the next data read cycle.

Therefore, read sequence of display data RAM is subject to constraints. In the data read immediately after the display data read command, the specified address data is not output (dummy read), but it is output at the 2nd data read session.

This relationship is shown in Fig.6.2.

Fig.6.2 Read Sequence of Display Data RAM

### 6.2 Display Data RAM

#### 6.2.1 Display Data RAM

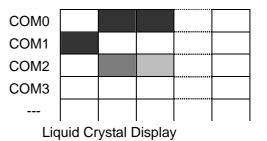

This RAM for storing display dot data is comprised of  $184 \times 224 \times 2$  bits. The desired bit is accessible by specifying page address and column address.

When 4 gray scales are selected with the set display mode command, the input display data is processed as a pair of 2 bits each. Combination is

RAM bit data (higher bit, lower bit) = (D1, D0), (D3, D2), (D5, D4), (D7, D6)

= (1, 1): Gray scale 3 Black (in normal display mode)= (1, 0): Gray scale 2= (0, 1): Gray scale 1= (0, 0): Gray scale 0 White (in normal display mode)

When RAM bit data is gray scales 1 and 2, gray scale display will be provided according to parameters of set gray scale pattern command.

When binary display is selected with the set display mode command, 1-bit of built-in RAM corresponds to 1 dot of pixel. When RAM bit data is "1", black display appears. When RAM data is "0", white display appears.

RAM bit data

| "1": ON  | Black (in normal display mode) |

|----------|--------------------------------|

| "0": OFF | White (in normal display mode) |

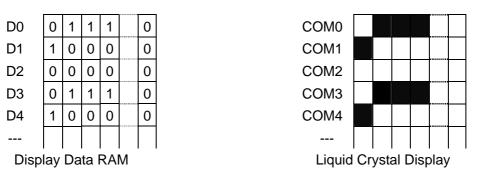

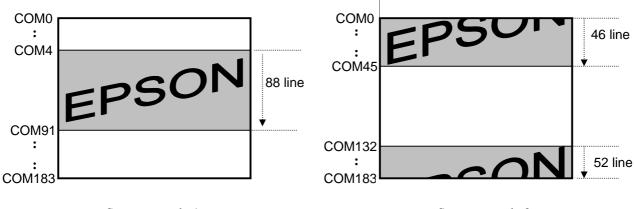

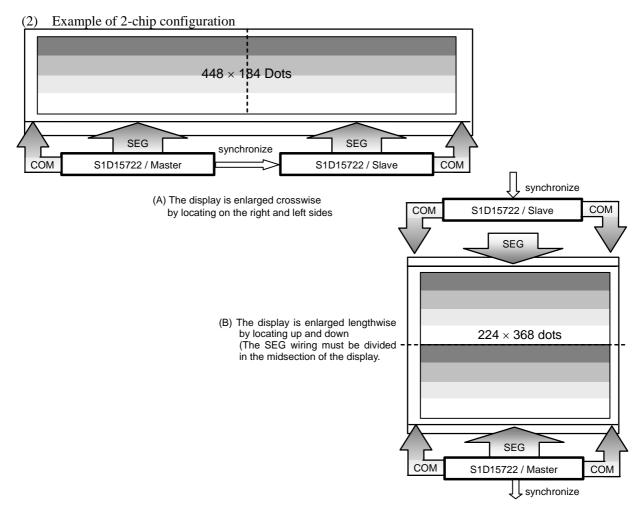

Since display data D7 to D0 from MPU corresponds to the common direction of LCD as shown in Fig.6.3 and Fig.6.4, higher degree of freedom is achieved in configuring display with less constraints on display data transfer if the S1D15722 series is used for the multi-chip.

Read/write from MPU to RAM is performed via I/O buffer, which is controlled independently of liquid crystal drive RAM. Therefore, even if MPU makes an asynchronous access to RAM during liquid crystal display, it does not have an adverse effect on the display.

| (D1, D0)         | (0, 0) | (1, 1) | (1, 1) |  | (0, 0) |  |  |

|------------------|--------|--------|--------|--|--------|--|--|

| (D3, D2)         | (1, 1) | (0, 0) | (0, 0) |  | (0, 0) |  |  |

| (D5, D4)         | (0, 0) | (1, 0) | (0, 1) |  | (0, 0) |  |  |

| (D7, D6)         | (0, 0) | (0, 0) | (0, 0) |  | (0, 0) |  |  |

|                  |        |        |        |  |        |  |  |

| Dicplay Data BAM |        |        |        |  |        |  |  |

Display Data RAM

Fig.6.4 Binary Display

#### 6.2.2 Gray Scale Display

When 4-gray scale is displayed with the set display mode command, the display is expressed by controlling FRM (frame gray scale) based on the gray scale data written to the display data RAM.

Density of gray level (gray scale 2, gray scale 1) of four gray scales is specified with the set gray scale pattern command. The density of gray scale can be selected from 14 levels.

#### 6.2.3 Page Address Circuit/Column Address Circuit

Use the set page address command and set column address command to specify display data RAM address to be accessed as shown in Fig.6.5 and Fig.6.6.

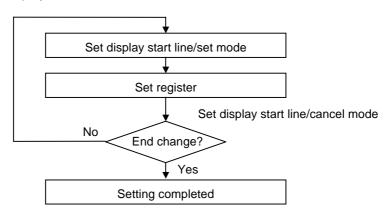

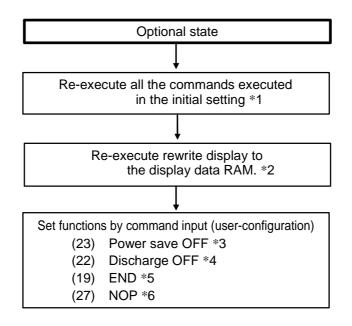

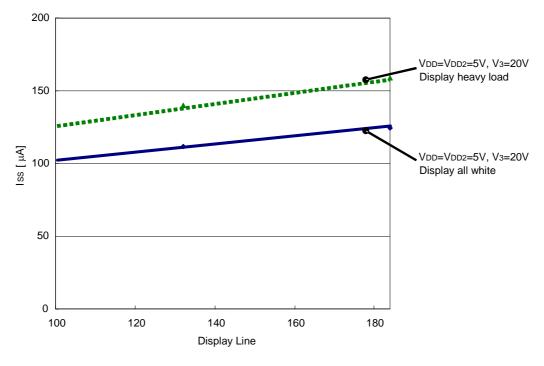

The address increment direction can be selected between the column direction and page direction using the select display data input direction command. In both directions, an increment by +1 takes place following read or write operation.