NOVATEK 聯 詠 科 技

V2.0

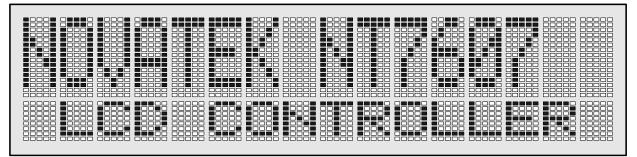

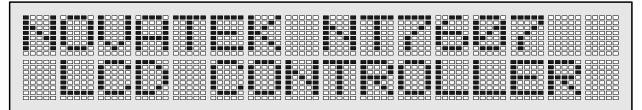

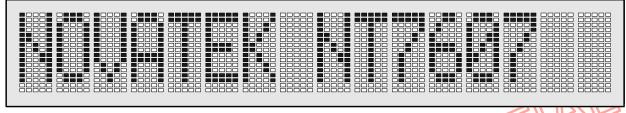

# NT7607

16 Characters X 3 Lines + 80 icons

STN LCD Controller/Driver

| Revision History           |

|----------------------------|

| Features4                  |

| General Description        |

| Pad Descriptions           |

| Block Diagram              |

| Functional Descriptions    |

| Commands                   |

| Electrical Characteristics |

| Application Notice         |

| ITO Layout Notice          |

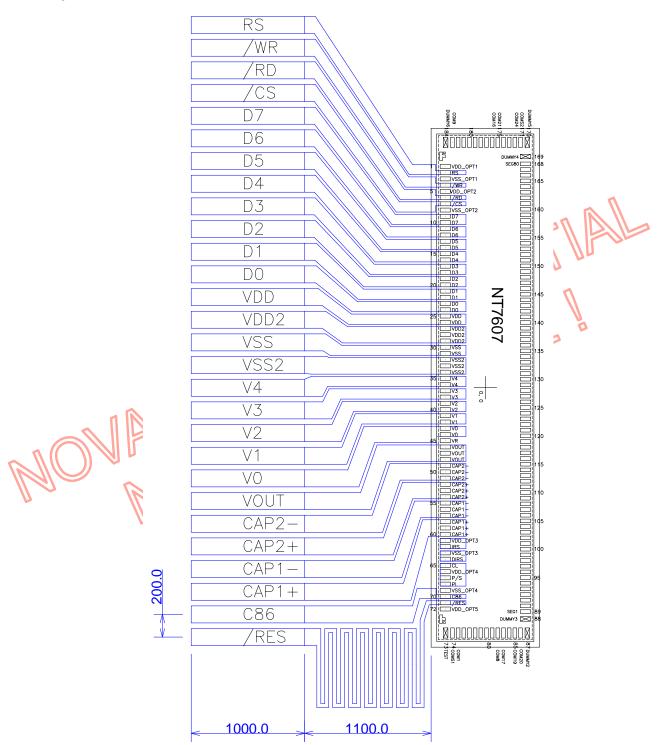

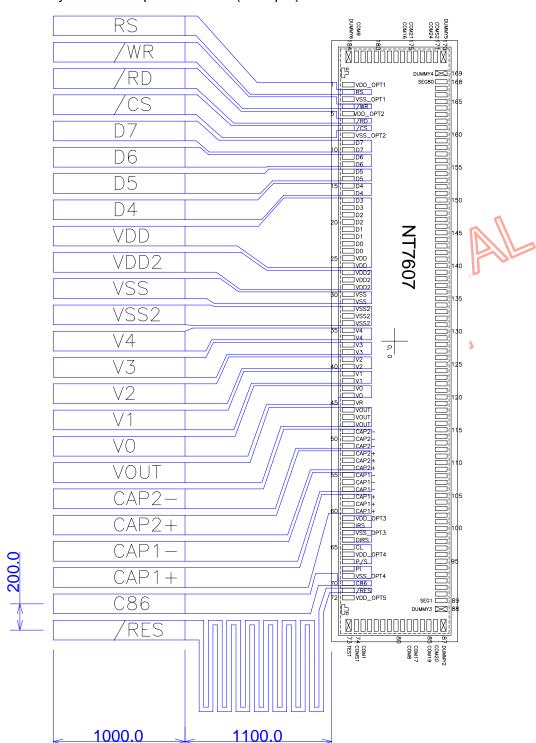

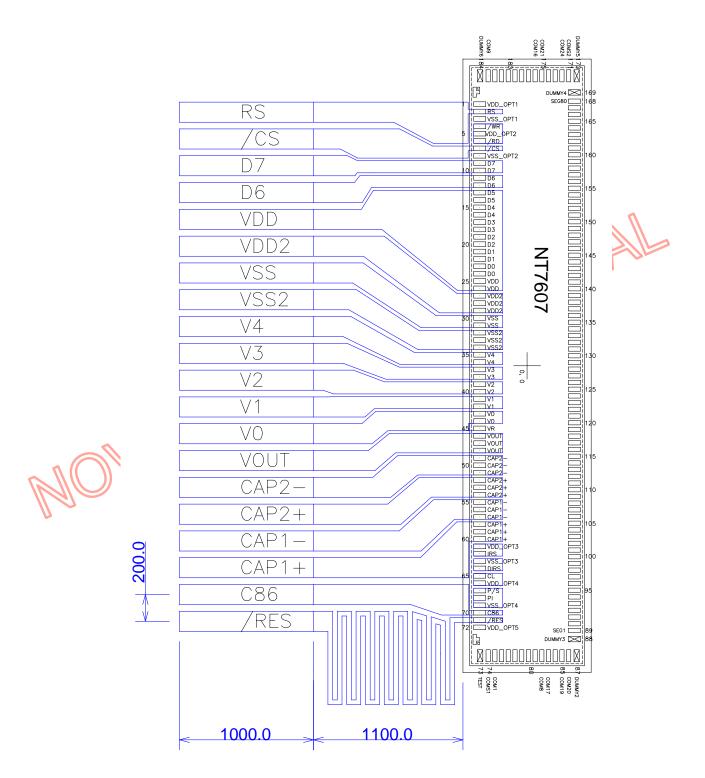

| Bonding Diagram            |

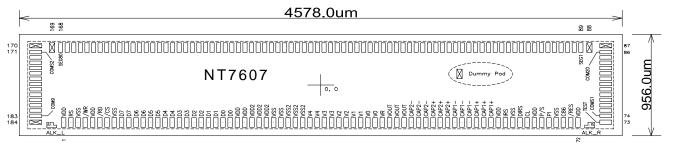

| Package Information        |

| Pad Dimensions             |

| Ordering Information       |

| Cautions                   |

| MO P                       |

# **Revision History**

| NT7607 Specification Revision History |                            |          |  |  |  |  |  |  |

|---------------------------------------|----------------------------|----------|--|--|--|--|--|--|

| Version                               | ersion Content Date        |          |  |  |  |  |  |  |

| 1.0                                   | Released                   | Oct 2006 |  |  |  |  |  |  |

| 2.0                                   | Add ROM code table of D06. | Dec 2006 |  |  |  |  |  |  |

ONATEK CONFIDENTIAL ONATESCLOSURE I NO DISCLOSURE I

# Features

- Single-chip LCD controller / driver

- 26 common outputs

- 80 segment outputs

- Applicable display panel

- 2-line x 16 characters + 80 icons (1/17 duty)

- 3-line x 16 characters + 80 icons (1/25 duty)

- 5 x 7 character format plus cursor; 5 x 8 for user defined symbols

- Character Generator ROM (CGROM)

- 10,240 bits (256 characters x 5 x 8 dots)

- Custom CGROM is also available

- Character Generator RAM (CGRAM): 320 bits (8 characters x 5 x 8 dots)

- Display Data RAM (DDRAM): 512 bits (16 characters x 4 lines x 8)

- Segment Icon Ram (ICONRAM): 80 bits (80 icons)

- Versatile functions provided on chip: Return home, Display control, Power save, Power control, etc.

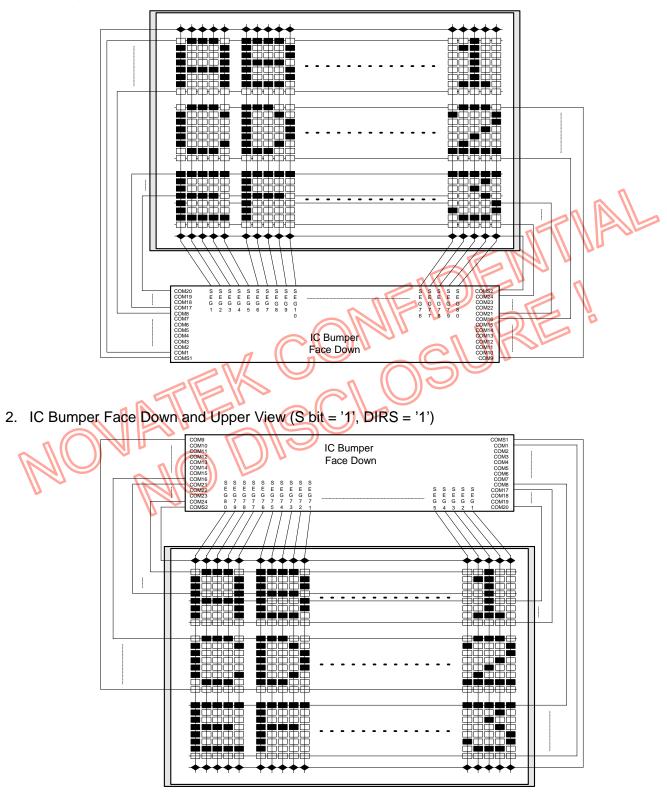

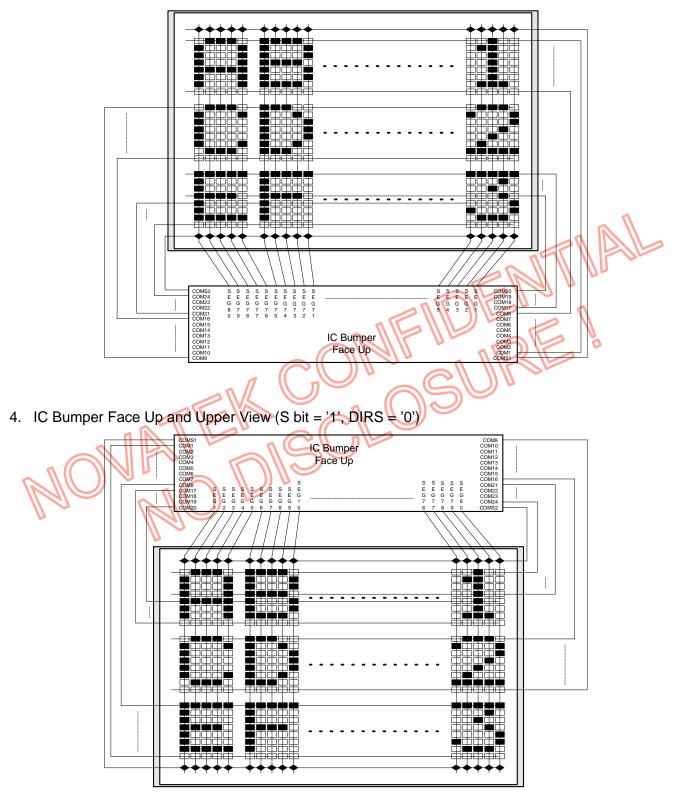

- COM / SEG bi-directional (4-type LCD application available)

- On-chip oscillator requires no external components (external clock also possible)

- 2X / 3X DC-DC converter generation of LCD supply voltage

- Voltage regulator with electronic volume for contrast control (32 steps)

- Voltage follower & bias circuit

- Very low current consumption (VDD, VDD2 = 3.0 V):

- Sleep mode: < 5 μA

- Normal mode: < 80 µA

- Power supply voltage: VDD=1.8~3.6V, VDD2 = 2.4~3.6V

- Display supply voltage range (VLCD = V0 VSS): VLCD = 4.0 to 7.0 V

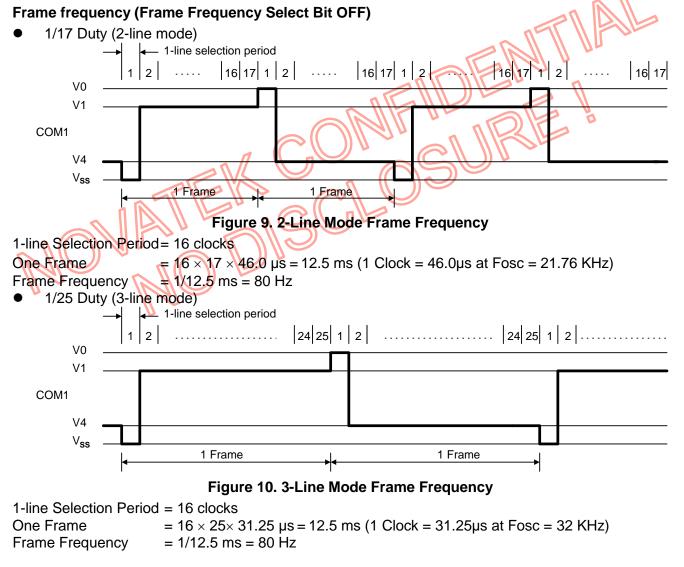

- 80 / 67 Hz frequency selection of frame rate

- No busy check or no execution waiting time

- 4-bit or 8-bit parallel bus: 6800 and 8080

- Serial interface: 3-wire / 4-wire SPI

- CMOS process

- Available in COG form

# **General Description**

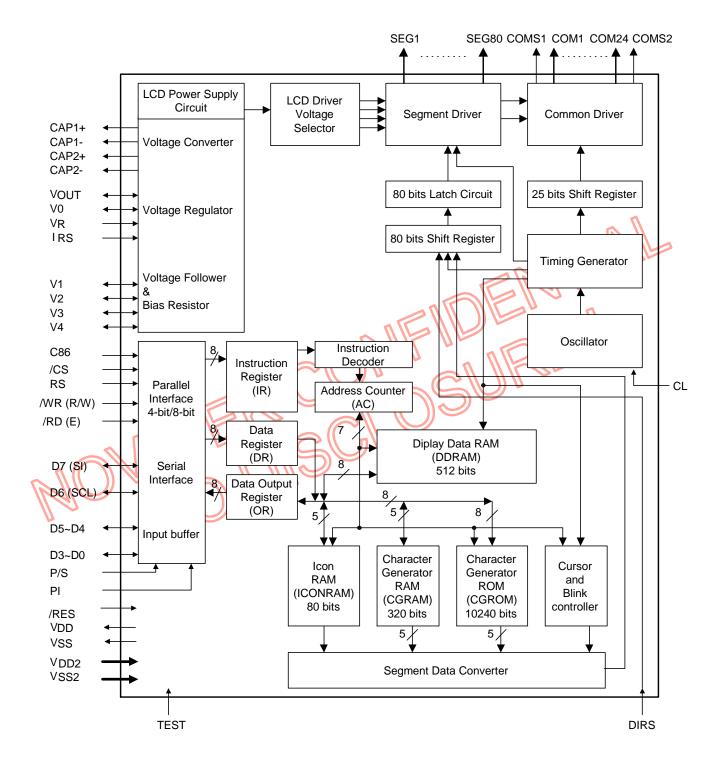

The NT7607 is a low power CMOS LCD controller and driver designed to drive a dot matrix LCD display of 2-line or 3-line by 16 characters with 5  $\times$  8-dot format. All necessary functions for the display are provided in a single chip, including on-chip generation of LCD bias voltages, resulting in a minimum of external components and lower system current consumption. The NT7607 interfaces to most micro-controllers via a 4-bit / 8-bit parallel bus or via the 3SPI / 4SPI serial interface. The chip contains a character generator and displays alphanumeric character.

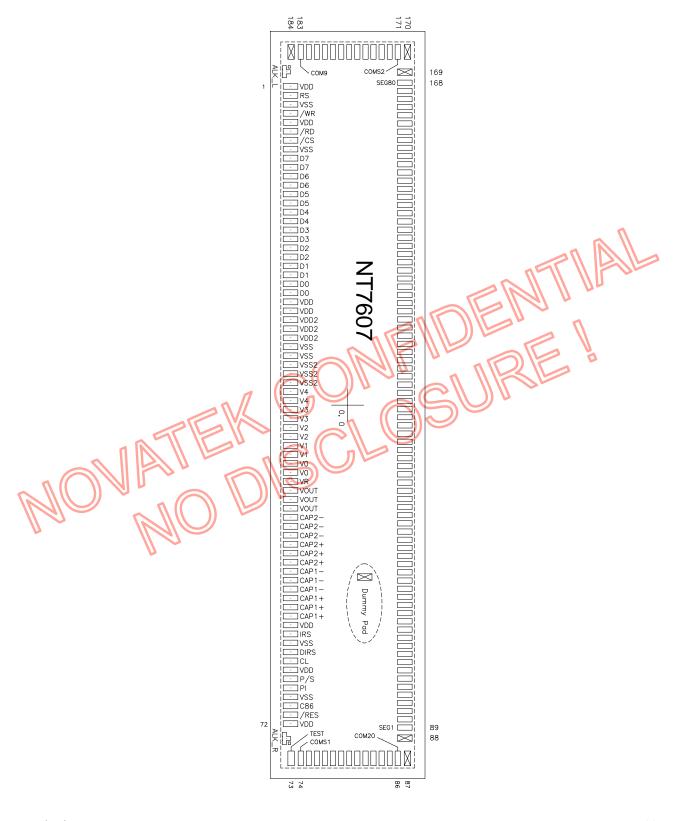

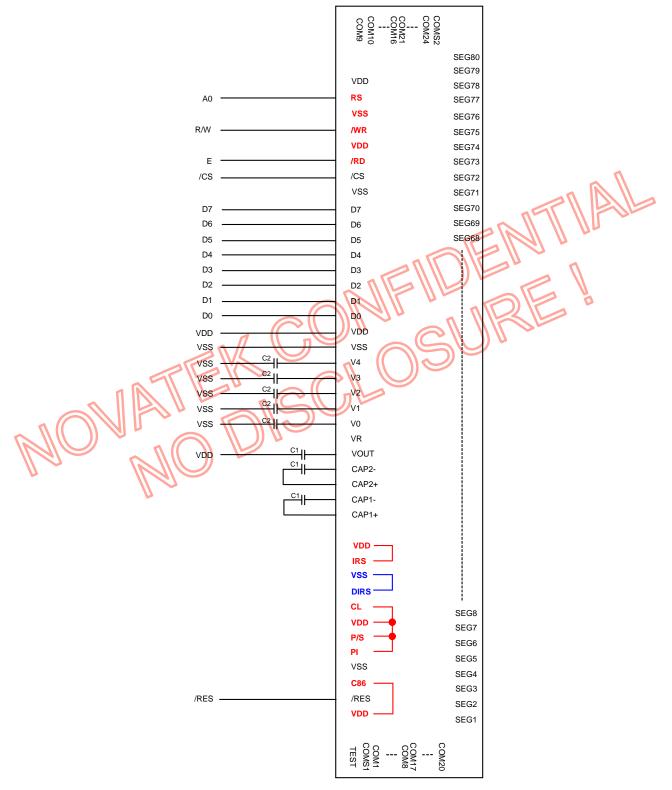

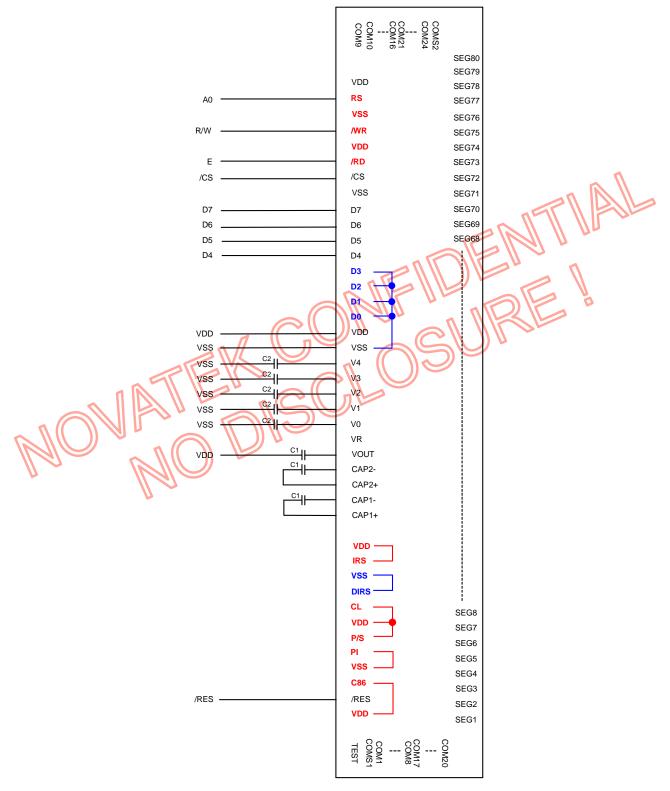

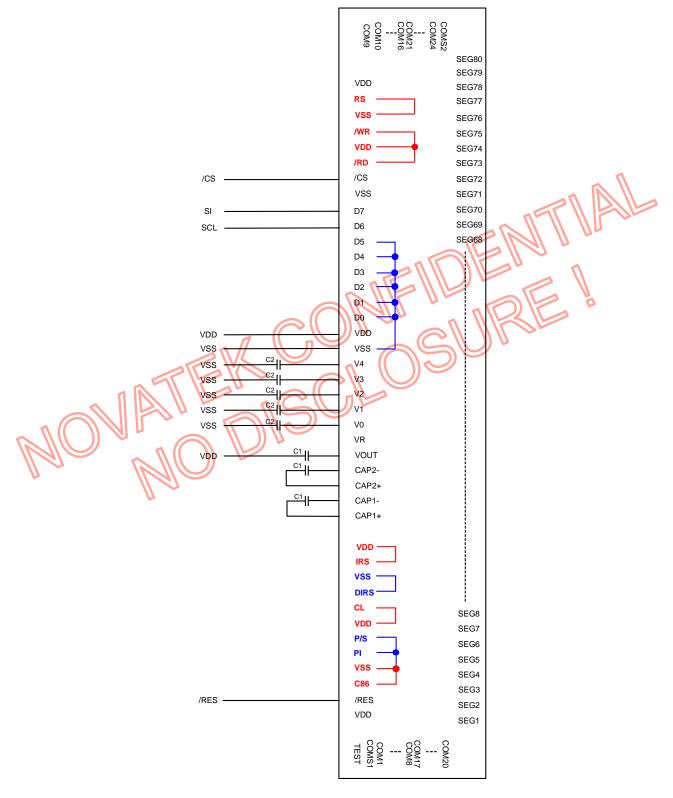

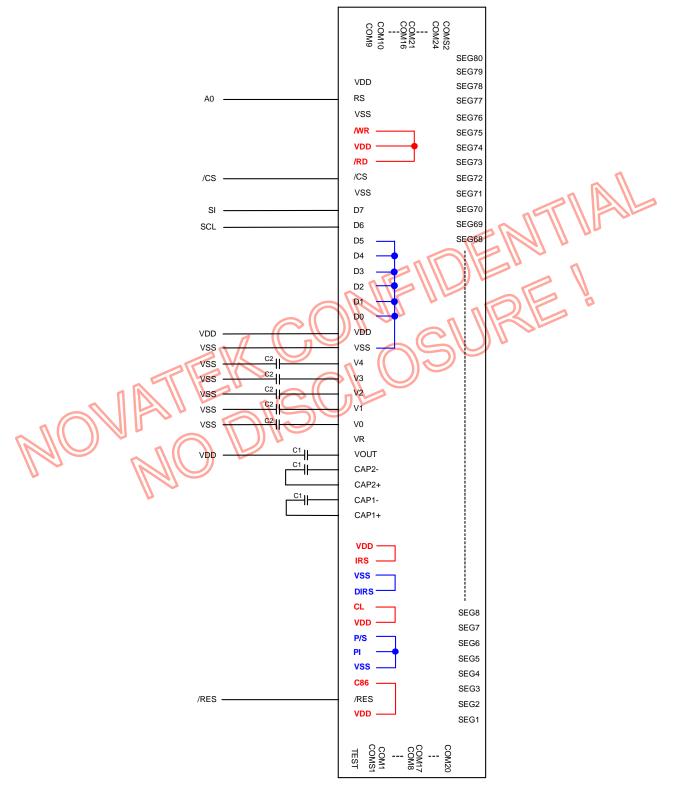

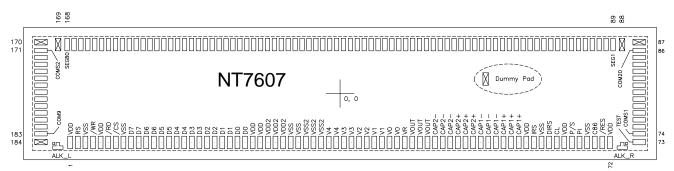

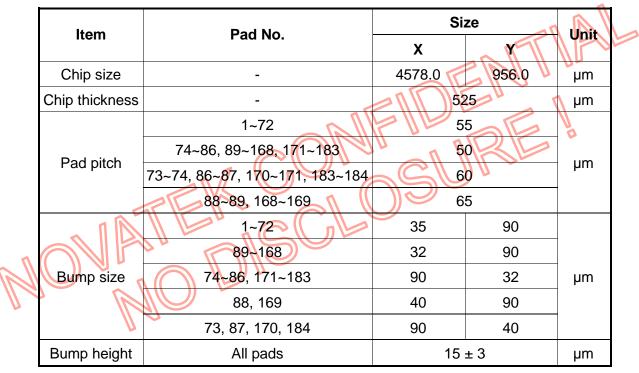

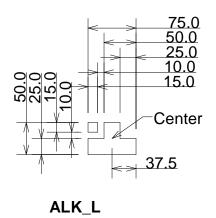

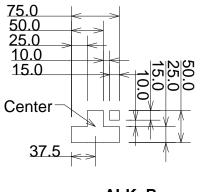

# **Pad Configuration**

2006/12/07 5 Ver 2.0 With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

NT7607

# **Block Diagram**

# **Pad Descriptions**

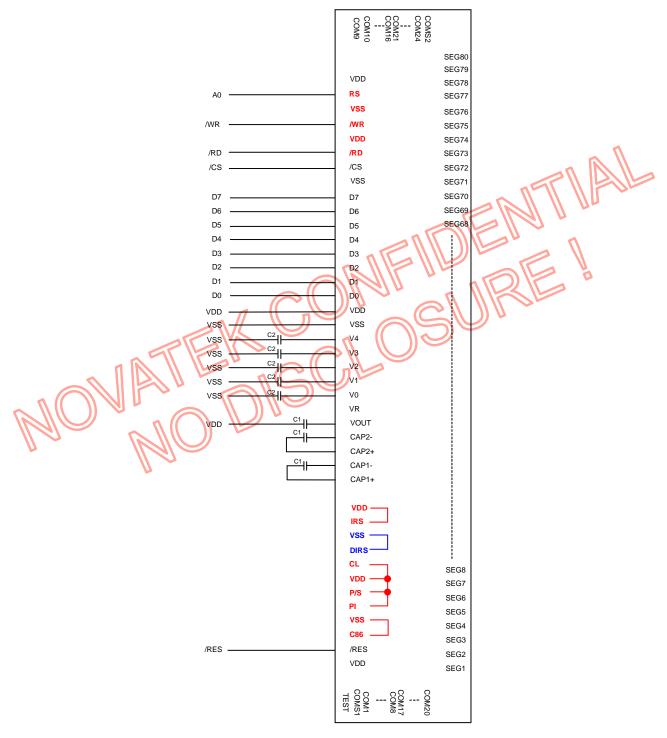

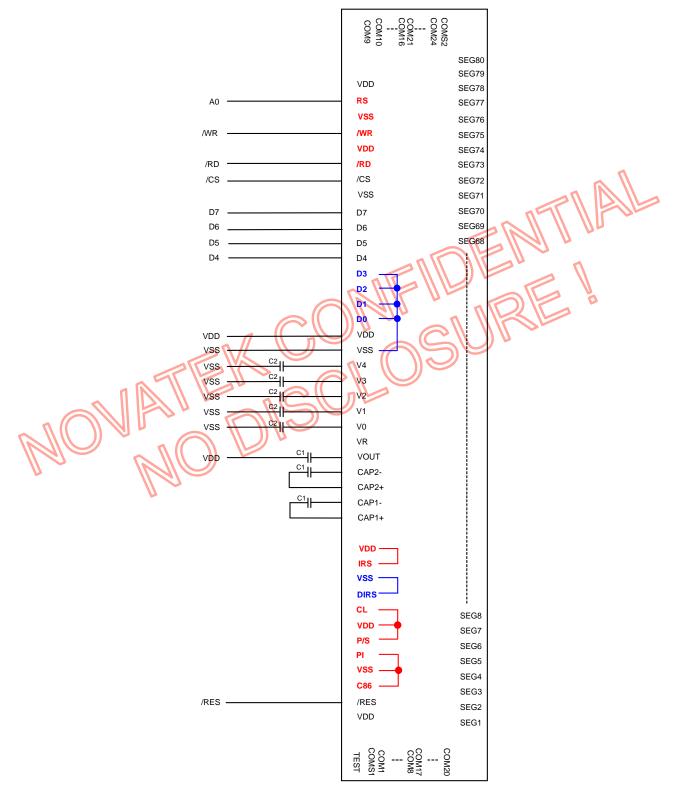

#### **Power Supply**

| Pad No.                                        | Designation                | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|------------------------------------------------|----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 25, 26                                         | VDD                        | Ρ   | 1.8 ~ 3.6 V power supply input for digital circuit                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 30, 31                                         | VSS                        | Р   | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 1, 5, 61, 66,<br>72                            | VDD                        | 0   | 1.8 ~ 3.6 V power supply output for pad option                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 3, 8, 63, 69                                   | VSS                        | 0   | Ground output for pad option                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 27~29                                          | VDD2                       | Р   | 2.4 ~ 3.6 V power supply input for analog circuit                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 32~34                                          | VSS2                       | Р   | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 43, 44<br>41, 42<br>39, 40<br>37, 38<br>35, 36 | V0<br>V1<br>V2<br>V3<br>V4 | P   | LCD driver supply voltages. The voltage determined by LCD cell is impedance-converted by a resistive driver or an operation amplifier for application. Voltages should be the following relationship: $V0 \ge V1 \ge V2 \ge V3 \ge V4 \ge VSS2$<br>When the on-chip operating power circuit is on, the following voltages are given to V1 to V4 by the on-chip power circuit. Voltage selection is performed by the Set LCD Bias instruction. |  |  |  |  |  |  |  |

# LCD Driver Supply

| Pad No. | Designation | 1/0 | Description                                                                           |  |  |  |  |

|---------|-------------|-----|---------------------------------------------------------------------------------------|--|--|--|--|

| 55~57   | CAP1-       | 0   | Capacitor 1- pad for internal DC/DC voltage converter                                 |  |  |  |  |

| 58~60   | CAP1+       | 0   | Capacitor 1+ pad for internal DC/DC voltage converter                                 |  |  |  |  |

| 49~51   | CAP2-       | 0   | Capacitor 2- pad for internal DC/DC voltage converter                                 |  |  |  |  |

| 52~54   | CAP2+       | 0   | Capacitor 2+ pad for internal DC/DC voltage converter                                 |  |  |  |  |

| 46~48   | VOUT        | I/O | DC/DC voltage converter output.                                                       |  |  |  |  |

| 45      | VR          | I   | Voltage adjustment pad. Applies voltage between V0 and VSS using a resistive divider. |  |  |  |  |

#### System Bus Connection Pads

| Pad No. | Designation  | I/O | Description                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|---------|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 62      | IRS          | I   | This terminal selects the resistors for the V0 voltage level adjustment.<br>IRS = "H", Use the internal resistors<br>IRS = "L", Do not use the internal resistors<br>The V0 voltage level is regulated by an external resistive voltage divider<br>attached to the VR terminal.                                                                    |  |  |  |  |  |  |

| 65      | CL           | I   | External clock input.<br>It must be fixed to "H" or "L" when the internal oscillation circuit is used.<br>In case of the external clock mode, CL is used as the clock and OS bit<br>should be OFF.                                                                                                                                                 |  |  |  |  |  |  |

| 68      | PI           | I   | Interface data length selection pin for parallel data input<br>PI = "L": 4-bit data input mode.<br>PI = "H": 8-bit data input mode.                                                                                                                                                                                                                |  |  |  |  |  |  |

| 70      | C86          | I   | This is the MPU interface switch terminal.<br>C86 = "L": 8080 Series MPU interface.<br>C86 = "H": 6800 Series MPU interface.                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 67      | P/S          | I   | This is the parallel data input/serial data input switch terminal.<br>P/S = "L": Serial data input.<br>P/S = "H": Parallel 4-bit / 8-bit data input.<br>When P/S = "L", D0 to D5 are HZ. D0 to D5 may be "H" or "L" /RD (E)<br>and /WR (R/W) are fixed to either "H" or "L". With serial data input, RAM<br>display data reading is not supported. |  |  |  |  |  |  |

| 64      | DIRS         |     | SEG direction selection input<br>DIRS = "L": SEG1, SEG2, SEG79, SEG80<br>DIRS = "H": SEG80, SEG79, SEG2, SEG1                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| R       | ) /cs        |     | This is the chip select signal.<br>When /CS = "L", then the chip select becomes active, and data/instruction I/O is enabled                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 71      | /RES         |     | When /RES is set to "L", the settings are initialized.<br>The reset operation is performed by the /RES signal level.                                                                                                                                                                                                                               |  |  |  |  |  |  |

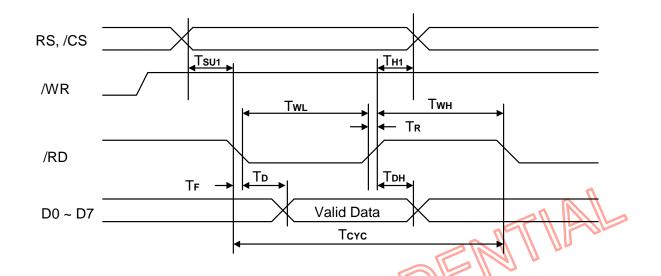

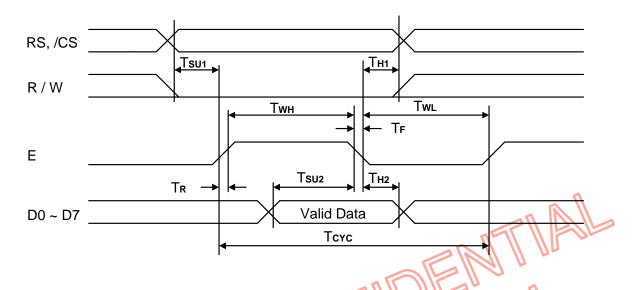

| 6       | /RD<br>(E)   | I   | <ul> <li>When connected to an 8080 Series MPU, it is low active. This pad is connected to the /RD signal of the 8080 MPU, and the NT7607 data bus is in an output status when this signal is "L".</li> <li>When connected to a 6800 Series MPU, this is active HIGH. This is used as an enable clock input of the 6800 series MPU.</li> </ul>      |  |  |  |  |  |  |

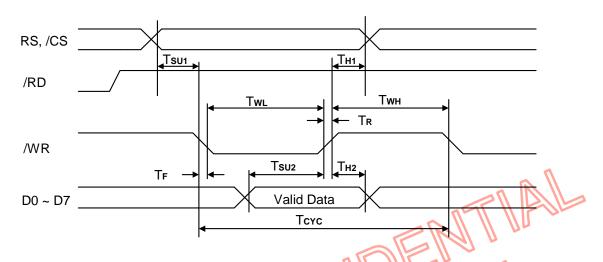

| 4       | /WR<br>(R/W) | I   | When connected to an 8080 Series MPU, this is low active. This terminal connects to the 8080 Series MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.<br>When connected to a 6800 Series MPU: This is the read/write control signal input terminal.<br>R/W = "L": Write.<br>R/W = "H": Read.           |  |  |  |  |  |  |

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

## System Bus Connection Pads (continued)

255

>

| Pad No.                           | Designation                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------------------------|-------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2                                 | RS                                        | Ι   | Register selects signal input.<br>RS = "L": selects the instruction register<br>RS = "H": selects the data register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 24~17<br>16~13<br>11, 12<br>9, 10 | D0 ~ D3<br>D4 ~ D5<br>D6 (SCL)<br>D7 (SI) | I/O | When 8-bit bus mode (P/S = "H" and PI = "H"), D0 ~ D7 are used as<br>bi-directional data bus that connects to an 8-bit MPU data bus.<br>When 4-bit bus mode (P/S = "H" and PI = "L"), D4 ~ D7 are used as<br>bi-directional data bus that connects to a 4bit MPU data bus. And in<br>this case D0 ~ D3 pins are not used and must always be fixed "H" or<br>"L".<br>When the serial interface is selected (P/S = "L"), then D7 serves as<br>the serial data input terminal (SI) and D6 serves as the serial clock<br>input terminal (SCL). At this time, D0 to D5 are must always be fixed<br>"H" or "L". |  |  |  |  |  |

| System E                          | System Bus Connection                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

# **System Bus Connection**

| Pad No.          | Designation     | I/O | Description                                                                                          |

|------------------|-----------------|-----|------------------------------------------------------------------------------------------------------|

| 89~168           | SEG1 ~ 80       | 0   | Segment signal output for LCD display                                                                |

| 75~86<br>172~183 | COM1 ~ 24       | 0   | Common signal output for LCD display.                                                                |

| 74, 171          | COMS1,<br>COMS2 | 0   | Common signal output for icon display<br>COMS1 and COMS2 are the same signal, but name is different. |

# Dummy Pads

| Pad No. | Designation | 1/0 | Description                         |

|---------|-------------|-----|-------------------------------------|

| 87      | Dummy1      | 6   |                                     |

| 88      | Dummy2      |     |                                     |

| 169     | Dummy3      |     | Dummy pads. No connection for user. |

| 170     | Dummy4      | -   |                                     |

| 184     | Dummy5      | -   |                                     |

**Test Pad**

| Pad No. | Designation | I/O | Description                       |  |

|---------|-------------|-----|-----------------------------------|--|

| 73      | TEST        | Ι   | Test pad. No connection for user. |  |

# **Functional Descriptions**

#### **Microprocessor Interface**

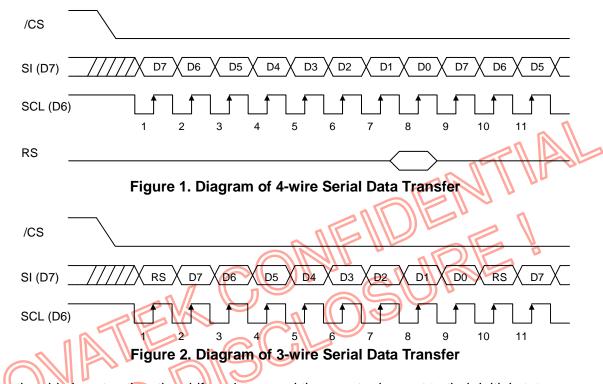

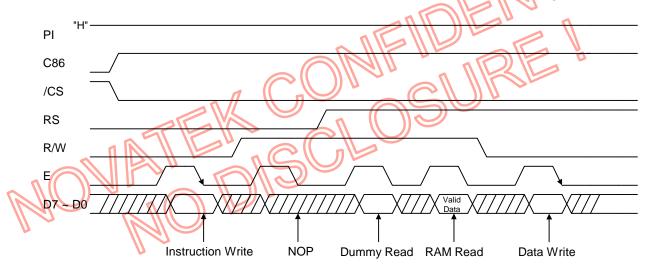

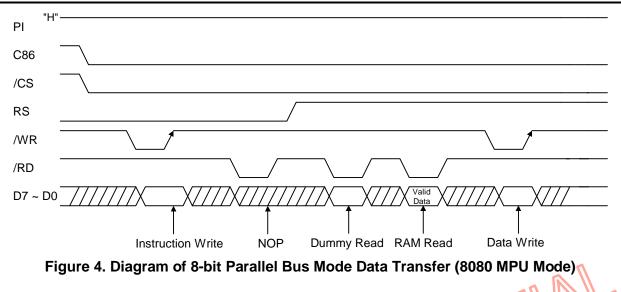

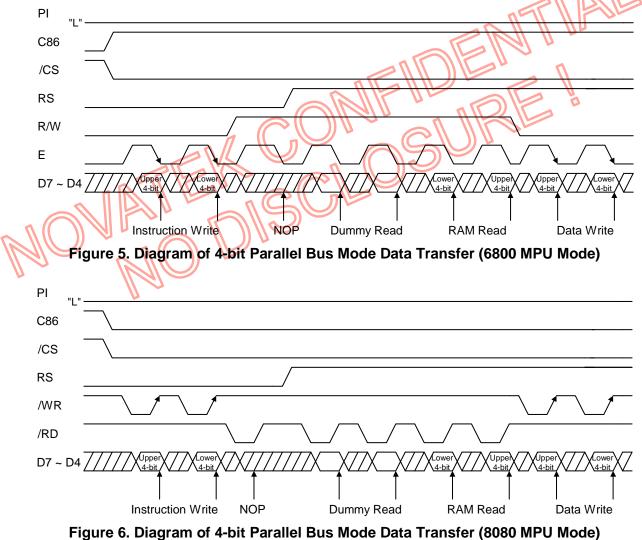

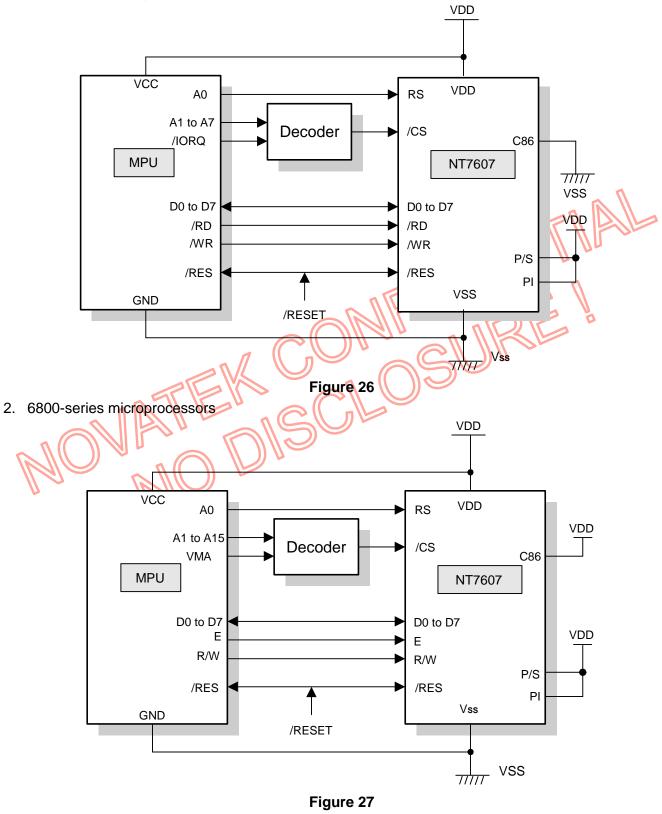

NT7607 has two kinds of interface type with MPU: parallel mode, serial mode. Parallel or serial mode is selected by P/S pad. In parallel mode, 4-bit data bus or 8-bit data bus is selected by PI pad, and 6800 or 8080 MPU mode is selected by C86 pad.

#### Interface type selection

The NT7607 can transfer data via 4-bit bi-directional data bus (D7 to D4) / 8-bit bi-directional data bus (D7 to D0) or via serial data input (SI).

When high or low is selected for the parity of P/S pad, either 4-bit/ 8-bit parallel data input or serial data input can be selected. When serial data input is selected, the RAM data cannot be read out.

| P/S | C86 | ΡI | Туре              | /CS | RS | /RD<br>(E) | /WR<br>(R/W) | D7 | D6    | D5, D4   | D3 to D0 |

|-----|-----|----|-------------------|-----|----|------------|--------------|----|-------|----------|----------|

|     | L   | I  | 3-wire SPI        | /CS | -  | -          | -            | SI | SCL   |          | -        |

|     | Н   | I  | 4-wire SPI        | /CS | RS | -          | -            | SI | SCL   |          | VIE      |

|     | L   | L  | 8080 series 4-bit | /CS | RS | /RD        | /WR          |    | D7 to | 0 D4     | -        |

| Н   | L   | Н  | 8080 series 8-bit | /CS | RS | /RD        | /WR          |    | U     | D7 to D0 |          |

|     | Н   | L  | 6800 series 4-bit | /CS | RS | H          | R/W          |    | D7 to | D4       | -        |

|     | Н   | Н  | 6800 series 8-bit | /CS | RS |            | R/W          |    |       | D7 to D0 |          |

#### Table 1. Parallel or Serial MPU Interface according to P/S

Note: "-" must always be fixed "H" or "L"

# Parallel Input (P/S is high)

When the NT7607 selects parallel input (P/S = high), the 4-bit or 8-bit parallel input mode can be selected by causing the PI pad to go high or low.

When the NT7607 selects parallel input (P/S = high), the 8080 series microprocessor or 6800 series microprocessor can be selected by causing the C86 pad to go high or low.

The NT7607 identifies the data bus signal according to RS, /RD (E) and /WR (R/W) signals.

| C86     |                | 1   | 0              |     |                         |

|---------|----------------|-----|----------------|-----|-------------------------|

| Control | 6800 processor |     | 8080 processor |     | Function                |

| RS      | Е              | R/W | /RD            | /WR |                         |

| 0       | 1              | 1   | 0              | 1   | Reads status            |

| 0       | 1              | 0   | 1 0            |     | Writes instruction data |

| 1       | 1              | 1   | 0              | 1   | Reads display data      |

| 1       | 1              | 0   | 1              | 0   | Writes display data     |

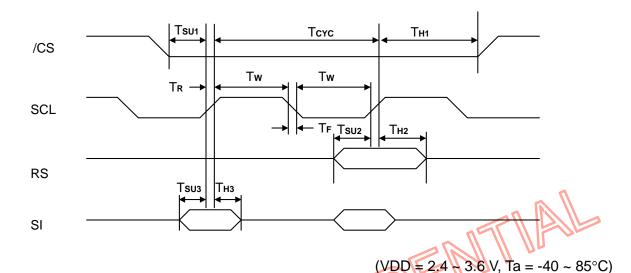

#### Serial Interface (P/S is low)

When the serial interface has been selected (P/S = "L") then when the chip is in active state (/CS = "L") the serial data input (SI) and the serial clock input (SCL) can be received. The serial data is read from the serial data input pin in the rising edge of the serial clocks D7, D6 through D0, in this order. At the rising edge of the 8th serial clock, the serial data (D7 – D0) is converted into 8 bit bus mode data. The RS input of the DR/IR selection is latched in the rising edge of eighth serial clock (SCL) for the processing.

1. When the chip is not active, the shift registers and the counter is reset to their initial states.

- 2. Reading is not possible while in serial interface mode.

- 3. Caution is required on the SCL signal when it comes to line-end reflections and external noise. We recommend the operation be rechecked on the actual equipment.

#### **Chip Select Inputs**

Note:

The NT7607 has one chip select pads. /CS can interface to a microprocessor when /CS is low . When this pads are set to high, D0 to D7 are high impedance and RS, /RD (E), /WR (R/W) inputs are disabled.

#### Registers

The NT7607 has three 8-bit registers, an Instruction Register (IR), and Data Register (DR) and an output data register (OR).

During writing operation, the Register Select signal (RS) determines which register will be accessed. The instruction registers stores instruction codes and address information for the Display Data RAM (DDRAM), Character Generator RAM (CGRAM) and Segment Icon RAM (ICONRAM).

During reading operation, output data register (OR) is used. The output data register temporarily stores data to be read from the DDRAM, CGRAM and ICONRAM and one of these RAM are selected by RAM address setting instruction. After RAM address setting, first reading is a dummy cycle in 8-bit bus mode. The valid data comes from second reading. In 4-bit bus mode, after RAM address setting, first and second reading is dummy cycles. The valid data comes from third reading. The dummy read make the address counter (AC) increased by 1.So it is recommended to set address again before writing, The instruction read cycle is not supported and it is regarded as a no operation cycle.

In 4-bit bus mode, it is needed to transfer 4-bit data (through D7~ D4) by two times .The high order bits (for 8-bit mode D7~D4) are written before the low order bits (for 8-bit mode D3~D0) in write and low order bits (for 8-bit mode D3~D0) are read before the high order bits (8-bit mode D3~D0) in read transaction. The D0~D3 pins are fixed "H" or "L" in this 4-bits bus mode. After /RES resets, NT7607 considers first 4-bit data from MPU as high order bits.

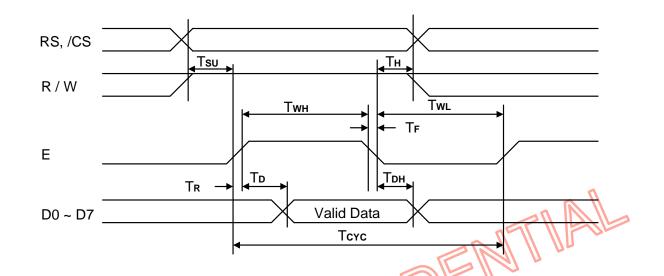

Figure 3. Diagram of 8-bit Parallel Bus Mode Data Transfer (6800 MPU Mode)

#### Address Counter (AC)

The address counter assigns addresses to the DDRAM CGRAM and ICONRAM for reading and writing and is set by the instructions 'CGRAM address set', 'DDRAM address set' and 'ICONRAM address set'. After a read/write operation, the address counter is automatically incremented by 1. The address counter content are only one and stores the address among DDRAM / CGRAM / ICONRAM.

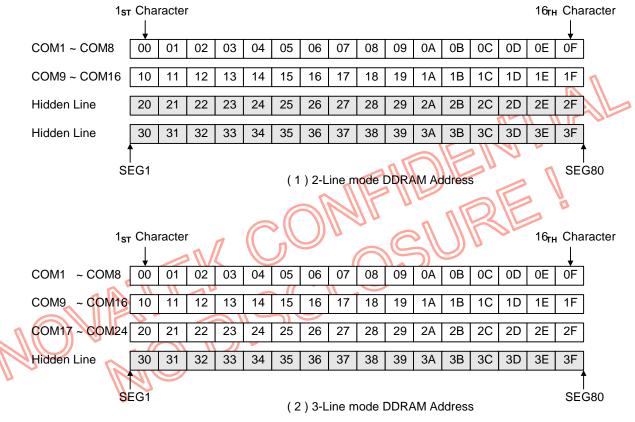

#### Display Data RAM (DDRAM)

The DDRAM stores up to 64 characters of display data represented by 8-bit character codes. DDRAM address is set in the address counter (AC) as a hexadecimal number.

Figure 7. DDRAM Address

#### **Character Generator ROM (CGROM)**

The Character Generator ROM generates 256 character patterns in a  $5 \times 8$ -dot format from 8-bit character codes. The CG bit of the instruction table selects the 8 characters (00H ~ 07H) of CGROM or CGRAM. Table 3 shows the character set that is currently implemented. User can define self-CGROM through changing MASK ROM.

| High<br>4-bit | 0000 | 0001 | 0010 | 0011   | 0100 | 0101 | 0110 | 0111 | 1000 | 1001         | 1010 | 1011 | 1100     | 1101 | 1110     | 1111 |

|---------------|------|------|------|--------|------|------|------|------|------|--------------|------|------|----------|------|----------|------|

| 0000          |      |      |      | Ø      | Ø    | P    | *    |      |      |              |      |      | 9        |      |          | •    |

| 0001          |      |      | 1    |        |      |      |      | -    |      |              | n    | P    | Ţ        | ć,   |          | 88   |

| 0010          |      | ٩.   | Π    | 2      | B    | R    | b    |      |      |              | T    | 4    | Ņ        |      | y        |      |

| 0011          |      | 11   | #    | 3      | C    | 8    | C    |      |      |              | 1    | Ď    | Ŧ        | E    | TI.      |      |

| 0100          |      | T    | \$   | 4      | D    | T    |      | t.   |      | 5            |      | Ι    | k        | þ    | 2        | 2    |

| 0101          |      | 5    | X    | 9      |      |      |      |      |      | $\pm$        |      | đ    | <u>†</u> | 1    | 3        |      |

| 0110          |      |      | 8.   | 6      |      | IJ   | f    |      |      | X            | Ņ    | þ    |          |      | ļ.       |      |

| 0111          |      | ÷    | 7    | 7      |      |      |      |      | ×    | •            | 7    | +    | X        |      |          | Å    |

| 1000          |      | Ť    | Ç    | 8      |      | ×    | ľ    | 88   |      | $\mathbb{X}$ | 4    | 7    | Å        |      |          |      |

| 1001          |      | 4    | )    | 9      | -    | Y    | 1    |      |      | 2            | ċ    | 'n   | ļ        |      |          |      |

| 1010          |      |      | *    | #<br># |      | 2    | đ    |      |      | 3            | T    |      | Ù        | ķ    | <u>.</u> |      |

| 1011          |      |      | ÷    |        | K    |      | k    | Ś    |      | μų.          | 7    | ij   |          |      |          | 3-7  |

| 1100          |      | ÷    | 2    | K,     |      | ÷    | 1    |      |      | N4           | 17   | 2,   | 7        | 7    | <u></u>  |      |

| 1101          |      | ÷    |      |        | M    |      | m    | }    |      |              | _    | X    | Ŷ        |      | ø        | *    |

| 1110          |      | Ŧ    |      | 2      | N    | **   | r    |      |      |              |      | Ċ    |          |      |          | *    |

| 1111          |      |      | 1    | 2      | Ü    |      | O    | ÷    |      | 3            | 19   | IJ   | 2        |      | p        |      |

Table 3-1. Character Standard Code in CGROM (D01)

2006/12/07

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

# NT7607

| High<br>4-bit<br>4-bit |   | 0001 | 0010 | 0011     | 0100 | 0101  | 0110 | 0111 | 1000  | 1001 | 1010 | 1011  | 1100 | 1101 | 1110 | 1111 |

|------------------------|---|------|------|----------|------|-------|------|------|-------|------|------|-------|------|------|------|------|

| 0000                   | Б |      | 3    | 3        | ۵    | P     | •    |      |       | 1    |      | ø     | Å    | Ð    | à    | đ    |

| 0001                   | ŕ | Щ    | ļ    | 1        | A    | Q     | 3    | 9    |       |      | i    |       | Å    | Ň    | á    | ß    |

| 0010                   | e | Ъ    | 11   | 2        | B    | R     | Ь    | r    | Д     | Ь    | ß    | .iii. | 8    | ò    | 3    | ò    |

| 0011                   |   | 6.   | #    |          | 0    | 5     | C,   |      |       | 3    | 9    | ••••• | 8    | Ó    | 8    | å    |

| 0100                   |   | Ŀ    | -    | 4        | D    |       |      | ł,   | ····· | H    | ú    | ž     | Ä    | Ô    | ä    | Ô    |

| 0101                   | h | 3    | 2    | 5        |      |       | e    | u    | Ø     | 9    | ¥    | X     | Å    | ð    | 90   | 8    |

| 0110                   | Ŕ | ю    | 8.   | 6        | -    | Q     | f    | Ų    | Й     | 6    | 3    | X     | Æ    | Ö    | 32   | ö    |

| 0111                   | Ŷ | 9    | 7    | 7        | 0    | W     | 9    | W    | K     |      | 8    | -     |      | x    |      |      |

| 1000                   | Ļ | ¥    | Ç    | 8        | H    | X     | h    | X    | m     |      |      | ŀ     |      | 0    | è    |      |

| 1001                   | ħ | 8    | 2    | 9        | I    | Ŷ     | i    | 9    | Π     | а,   | M    | Ŷ     | É    | Ù    | é    | Û    |

| 1010                   | ŕ | Ŷ    | *    | 11<br>11 | J    | Z     | j    | Z    | Ņ     | 88   | -    | Œ     |      | Ú    | â    | Ú    |

| 1011                   | Ĉ |      | +    | 8<br>7   | K    | Ľ     | k    | ł,   | φ     | 22   |      | Œ     |      | Ů    |      | Ű    |

| 1100                   | 1 |      | 7    | K        |      | ٩,    | 1    |      | LI,   |      | 1    | ÷     | ì    | Ü    | 1    |      |

| 1101                   | 8 |      |      |          |      |       | M    | ]    |       | ß    | ų.   | ÷     | ï    | Å    | 1    | ú    |

| 1110                   | ħ |      |      | Ņ        | N    | e e e | m    | ~~   |       | K    | ,    |       | Å    | 0    | 1    | þ    |

| 1111                   | Ŕ |      | 1    | 2        | m    |       | O    |      |       | Π    |      | ×.    | Ŧ    | ß    | 1    |      |

Table 3-2. Character Standard Code in CGROM (D06)

2006/12/07

Ver 2.0

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

Pattern

0 0 0 0

0 0 0 0

1 1 1 1 1

1 1 1 1

0 0 0

0 0 0 0 0

#### **Character Generator RAM (CGRAM)**

(05H)

CGRAM has up to  $5 \times 8$  dot 8 characters. By writing font data to CGRAM, use defined character can be used. CGRAM can be written regardless of CG bit.

|    |     | 7           | <b>Fabl</b> | e 4.      | Re | latio |    | •  |      |    |              |                            | add                                  | ress                                 | es | dat        | a a | nd | dis | pla                                  | ур                              | atte                                 | erns                                      | 5                                         |              |

|----|-----|-------------|-------------|-----------|----|-------|----|----|------|----|--------------|----------------------------|--------------------------------------|--------------------------------------|----|------------|-----|----|-----|--------------------------------------|---------------------------------|--------------------------------------|-------------------------------------------|-------------------------------------------|--------------|

|    | C   | Char<br>(DD |             |           |    |       |    | I  | DD / | CG | RAM          | ado                        | dres                                 | 5                                    |    | CG         | GRA | M  | dat | a (e                                 | exa                             | mp                                   | le)                                       |                                           | Pattern      |

| Hi | ghe | er          |             | der<br>ts | ĺ  | Low   | er | Hi | gher |    | Orde<br>bits | r                          | Low                                  | /er                                  |    | Cha<br>pat |     |    | ,   |                                      |                                 | arac<br>code                         |                                           |                                           | No.          |

| D7 | D6  | D5          | D4          | D3        | D2 | D1    | D0 | A6 | A5   | A4 | A3           | A2                         | A1                                   | A0                                   | 4  | 3          | 2   | 1  | 0   | 4                                    | 3                               | 2                                    | 1                                         | 0                                         |              |

| 0  | 0   | 0           | 0           | 0<br>)H)  | 0  | 0     | 0  | 1  | 0    | 0  | 0            | 0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>0<br>0<br>1<br>1      | 0<br>1<br>0<br>1<br>0<br>1<br>0      |    |            |     |    |     | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>0<br>1<br>0<br>1<br>0      | 0<br>1<br>0<br>1<br>0<br>1<br>0      | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0      | 0<br>1<br>0<br>1<br>0<br>1<br>0           | Pattern<br>0 |

| 0  | 0   | 0           | 0<br>(01    | 0<br>IH)  | 0  | 0     | 1  | 1  | 0    | 0  | 1            | 0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0      |    |            |     |    |     | 0<br>1<br>0<br>1<br>0<br>1<br>0      | 0<br>1<br>0<br>1<br>0<br>1<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1      | 0<br>1<br>0<br>1<br>0<br>1                | Pattern      |

| 0  | 0   | 0           | 0<br>(02    | 0<br>2H)  | 0  | 1     | 0  | 1  | 0    | 1  | 0            | 0<br>0<br>0<br>1           | 0<br>0<br>1<br>1<br>0<br>0<br>1      | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 |    |            |     |    |     | 000000000                            |                                 | 0000000                              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Pattern<br>2 |

| 0  | 0   | 0           | 0(03        | 0<br>3H)  | 0  | 1     |    | 1  | 0    |    |              | 0<br>0<br>0<br>1<br>1<br>1 |                                      | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 |    |            |     |    |     | 0<br>1<br>1<br>1<br>0<br>1<br>1<br>1 | 1<br>0<br>1<br>1<br>1<br>1      | 1<br>0<br>1<br>1<br>1                | 1<br>0<br>1<br>0<br>1<br>1<br>1           | 0<br>1<br>1<br>0<br>1<br>1<br>1           | Pattern<br>3 |

| 0  | 0   | 9           | 0(04        | 0<br>1H)  | 1  | 0     |    |    | 1    | 0  | 0            | 0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1      | 0<br>1<br>0<br>1<br>0<br>1<br>0      |    |            |     |    |     | 1<br>1<br>0<br>1<br>1<br>1           | 1<br>0<br>0<br>1<br>1<br>1      | 0<br>0<br>0<br>0<br>1<br>1           | 1<br>0<br>0<br>1<br>1<br>1                | 1<br>1<br>1<br>1<br>1<br>1                | Pattern<br>4 |

| 0  | 0   | 0           | 0           | 0         | 1  | 0     | 1  | 1  | 1    | 0  | 1            | 0                          | 0                                    | 0                                    |    |            |     |    |     | 1                                    | 1                               | 1                                    | 1                                         | 1                                         |              |

N

| Table 4. Relationship between contain addresses data and display patterns (continued) | Table 4. Relationsh | p between CGRAM addresses data and display patterns ( | Continued) |

|---------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------|------------|

|---------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------|------------|

| С  | hara | acte |    | des<br>ta) | 5 (D | DR  | ١M | I  | DD / CGRAM address |    |              |                            |                                      | CGRAM data (example)            |   |           |              |   |   |                                           |                                 | Detterm                         |                                 |                                      |                |

|----|------|------|----|------------|------|-----|----|----|--------------------|----|--------------|----------------------------|--------------------------------------|---------------------------------|---|-----------|--------------|---|---|-------------------------------------------|---------------------------------|---------------------------------|---------------------------------|--------------------------------------|----------------|

| Hi | ighe | er   |    | der<br>its | I    | Low | er | Hi | gher               | (  | Orde<br>bits | r                          | Lov                                  | ver                             |   | Cha<br>pa | arao<br>tter |   | ٢ |                                           |                                 | ara<br>cod                      | ctei<br>e                       | r                                    | Pattern<br>No. |

| D7 | D6   | D5   | D4 | D3         | D2   | D1  | D0 | A6 | A5                 | A4 | A3           | A2                         | A1                                   | A0                              | 4 | 3         | 2            | 1 | 0 | 4                                         | 3                               | 2                               | 1                               | 0                                    |                |

| 0  | 0    | 0    | 0  | 0<br>6H)   | 1    | 1   | 0  | 1  | 1                  | 1  | 0            | 0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>0<br>0<br>1<br>1      | 0<br>1<br>0<br>1<br>0<br>1<br>0 |   | -         |              |   |   | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 1<br>1<br>1<br>1<br>1<br>1      | 1<br>1<br>1<br>1<br>1<br>1      | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | Pattern<br>6   |

| 0  | 0    | 0    | 0  | 0<br>7H)   | 1    | 1   | 1  | 1  | 1                  | 1  | 1            | 0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 |   |           |              |   |   | 0<br>1<br>1<br>0<br>1                     | 0<br>0<br>1<br>0<br>0<br>0      | 0<br>0<br>0<br>0<br>0<br>0<br>1 | 0<br>0<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>1<br>1<br>1           | Pattern<br>7   |

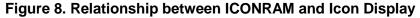

#### Segment ICON RAM (ICONRAM)

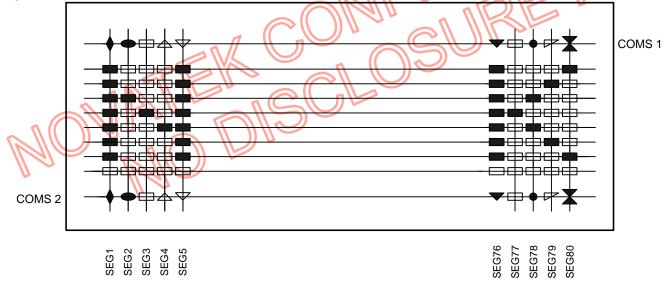

The ICONRAM has segment control data and segment pattern data. COMS1 and COMS2 are the same signals, but the name is different. The number of icons is 80.

| Table 5. Relationshi | Table 5. Relationship between ICONRAM addresses data and display patterns |    |    |       |         |     |     |     |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------|----|----|-------|---------|-----|-----|-----|--|--|--|--|--|

| ICONRAM address      |                                                                           |    |    | ICONR | AM Bits |     |     |     |  |  |  |  |  |

|                      | D7                                                                        | D6 | D5 | D4    | D3      | D2  | D1  | D0  |  |  |  |  |  |

| 00H                  | -                                                                         | -  | -  | S1    | S2      | S3  | S4  | S5  |  |  |  |  |  |

| 01H                  | -                                                                         | -  | -  | S6    | S7      | S8  | S9  | S10 |  |  |  |  |  |

|                      |                                                                           |    | -  | -     | -       |     | -   |     |  |  |  |  |  |

| 0EH                  | -                                                                         | -  | -  | S71   | S72     | S73 | S74 | S75 |  |  |  |  |  |

| 0FH                  | -                                                                         | -  | -  | S76   | S77     | S78 | S79 | S80 |  |  |  |  |  |

Note: "-" Don't care.

#### Oscillator

The on-chip oscillator provides the clock signal for the display system. No external components are required and the CL pad must be connected to "H" or "L" when the internal oscillation circuit is used. In case of the external clock mode, CL is used as the clock and OS bit should be OFF.

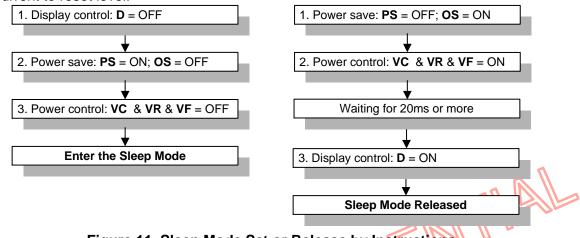

# Sleep mode (Power Save Bit ON, Oscillation Bit OFF)

NT7607 provides with sleep mode for saving power consumption during standby period.

To enter the sleep mode, the power circuit and oscillation circuit should be turned off by using the power save instruction and the power control instruction. This mode helps to save power consumption by reducing current to reset level.

# Figure 11. Sleep Mode Set or Release by Instructions

- Liquid Crystal Display Output COM1 ~ COM24, COMS1, COMS2: VSS level. SEG1 - SEG80: VSS level

- 2. Data written in DDRAM, CGRAM, ICONRAM and registers are remained as previous value.

- 3. Operation mode is retained the same as it was prior to execution of the sleep mode. All internal circuits are stopped.

- Power Circuit and Oscillation Circuit.

The build-in power supply circuit and oscillation circuit are turned off by power save instruction and power control instruction.

# LCD common and segment drivers

The NT7607 contains 26 common and 80 segment drivers, which connect the appropriate LCD bias voltages in sequence to the display in accordance with the data to be displayed. COMS1 and COMS2 drive the icon common. The bias voltages and the timing are selected automatically when the number of lines in the display is selected.

| DIRS pad | SEG data shift direction               |

|----------|----------------------------------------|

| L        | SEG1, SEG2, SEG3,, SEG78, SEG79, SEG80 |

| Н        | SEG80, SEG79, SEG78,, SEG3, SEG2, SEG1 |

| Table 6 | SEG | Data Shift | Direction |

|---------|-----|------------|-----------|

|         |     |            |           |

|             |           | Table 7. COM Data Shift Direction |

|-------------|-----------|-----------------------------------|

| Line mode   | S         | COM data shift direction          |

| 2-Line mode | 0 (left)  | COM1, COM2,, COM16, COMS1 (COMS2) |

| 2-Line mode | 1 (right) | COMS1 (COMS2), COM16,, COM2, COM1 |

| 3-Line mode | 0 (left)  | COM1, COM2,, COM24, COMS1 (COMS2) |

|             | 1 (right) | COMS1 (COMS2), COM24,, COM2, COM1 |

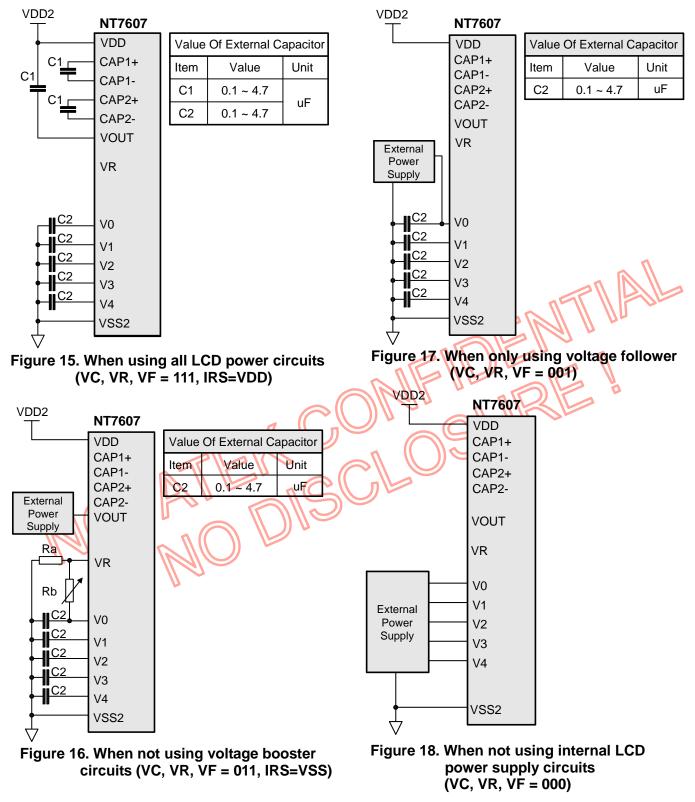

#### LCD supply voltage generator

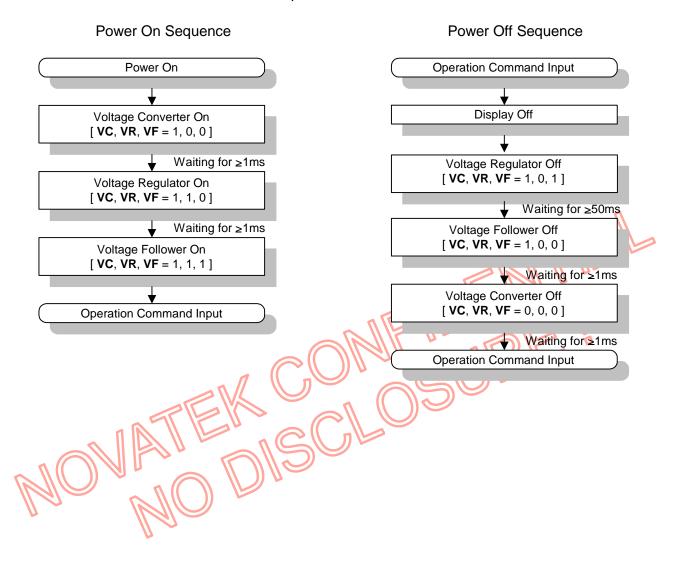

The power supply circuits are low-power consumption power supply circuits that generate the voltage levels required for the liquid crystal drivers. They comprise DC-DC converter circuits, voltage regulator circuits, and voltage follower circuits. The power supply circuits can turn the Booster circuits, the voltage regulator circuits, and the voltage follower circuits ON or OFF independently through the use of the Power Control Set instruction. Consequently, it is possible to make an external power supply and the internal power supply function somewhat in parallel. Table 8 shows the Power Control Set Instruction 3-bit data control function, and Table 9 shows reference combinations.

#### Table 8. The Control Details of Each Bit of the Power Control Set Instruction

| Item a liter                                    | Sta | atus | N |

|-------------------------------------------------|-----|------|---|

| item                                            | "1" | "0"  | ~ |

| VC: DC-DC converter (V/C) circuit control bit   | ON  | OFF  |   |

| VR: Voltage regulator circuit (V/R) control bit | ON  | OFF  |   |

| VF: Voltage follower circuit (V/F) control bit  | ON  | OFF  |   |

#### Table 9. LCD Power Supply Combinations

| Use Settings                                                    | VC | VR | VF | Voltage<br>converter<br>circuit | Voltage<br>regulator<br>circuit | Voltage<br>follower<br>circuit | External<br>voltage input | Step-up<br>voltage<br>system<br>terminal |

|-----------------------------------------------------------------|----|----|----|---------------------------------|---------------------------------|--------------------------------|---------------------------|------------------------------------------|

| Only the internal power supply is used                          | 1  | 1  | 1  | ON                              | ON                              | ON                             | VDD2                      | Used                                     |

| Only the V regulator<br>circuit and the V/F circuit<br>are used | 0  | 1  | 1  | OFF                             | ON                              | ON                             | VOUT, VDD2                | Open                                     |

| Only the V/F circuit is used                                    | 0  | 0  | 1  | OFF                             | OFF                             | ON                             | V0, VDD2                  | Open                                     |

| Only the external power<br>supply is used                       | 0  | 0  | 0  | OFF                             | OFF                             | OFF                            | V0 to V4, VDD2            | Open                                     |

\*The "step-up system terminals" refer CAP1+, CAP1-, CAP2+ and CAP2-.

\*While other combinations, not shown above, are also possible, these combinations are not recommended because they have no practical use.

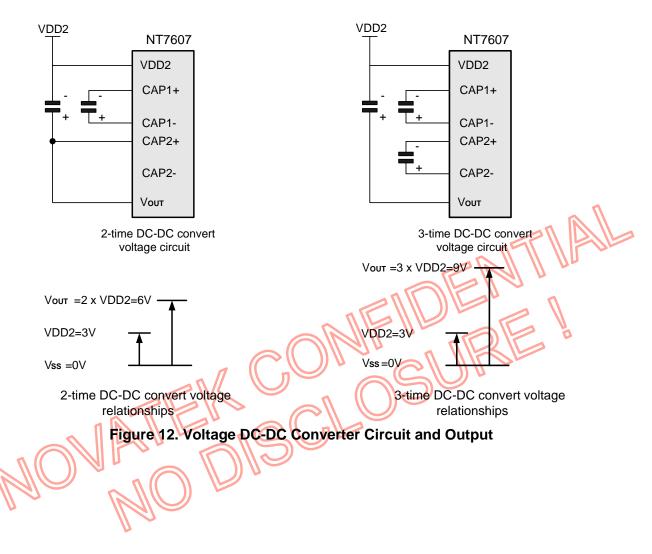

#### The Voltage DC-DC Converter Circuits

Using the step-up voltage circuits equipped within the NT7607 chips it is possible to product 2X, 3X Step-up of the VDD2 - VSS voltage levels. Vour is generated from the voltage converter. And this conversion voltage is used in the build-in Voltage Regulator circuit. Figure 12 shows the application circuit of 2-time and 3-time DC-DC converter.

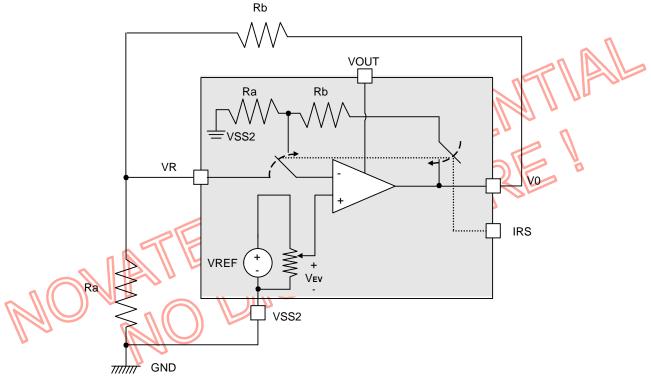

#### The Voltage regulator circuit

The step-up voltage generated at  $V_{00T}$  outputs the liquid crystal driver voltage V0 through the voltage regulator circuit. Because the NT7607 chips have an internal high-accuracy fixed voltage power supply with a 32-level electronic volume function and external resistors for the V0 voltage regulator.

Moreover, the internal VREF of voltage regulator has the temperature compensation function, and the temperature coefficient is about 0.0%/°C.

#### Using External Resistors to Adjust V0 Voltage Regulator

Through the use of the V0 voltage regulator external resistors and the electronic volume function the liquid crystal power supply voltage V0 can be controlled (with adding two external resistors: Ra and Rb), making it possible to adjust the liquid crystal display brightness. The V0 voltage can be calculated using equation A-1 over the range where V0 < VOUT.

$V0 = (1+Rb/Ra)^*Vev = (1+Rb/Ra)^* (1-\alpha/150)^*VREF$  (Equation A-1)

Figure 13. Voltage Regulator and Electronic Contrast Control Circuit

VREF is the IC internal fixed voltage supply, and its voltage at Ta = 25°C is as shown in Table 10.

| Table 10. Voltage VREF Selection |                     |       |      |  |  |  |  |  |  |  |

|----------------------------------|---------------------|-------|------|--|--|--|--|--|--|--|

| Equipment Type                   | Thermal<br>Gradient | Units | VREF |  |  |  |  |  |  |  |

| Internal power Supply            | -0.05               | %/°C  | 2.0V |  |  |  |  |  |  |  |

$\alpha$  is set to 1 level of 32 possible levels by the electronic volume function depending on the data set in the 5-bit electronic volume register. Table 11 shows the value for  $\alpha$  depending on the electronic volume register settings. Rb/Ra is the V0 voltage regulator internal resistor ratio, and can be set to 4 different

levels through the V0 voltage regulator internal resistor ratio set command. The (1+Rb/Ra) ratio assumes the values shown in Table 12 depending on the 2bit data settings in the V0 voltage regulator internal resistor ratio register.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  | α           | Vo      | Contrast |

|----|----|----|----|----|----|----|-----|-------------|---------|----------|

| -  | -  | -  | 0  | 0  | 0  | 0  | 0   | 0 (default) | Maximum | High     |

| -  | -  | -  | 0  | 0  | 0  | 0  | 1 1 |             | :       | :        |

| -  | -  | -  | 0  | 0  | 0  | 1  | 0   | 2           | :       | :        |

|    |    |    |    | :  |    |    | :   | :           | :       | :        |

|    |    |    |    | :  |    |    | :   | :           | :       | :        |

| -  | -  | -  | 1  | 1  | 1  | 1  | 0   | 30          | :       | :        |

| -  | -  | -  | 1  | 1  | 1  | 1  | 1   | 31          | Minimum | Low      |

#### Table 11. Electronic Contrast Control

Note: "-" Don't care.

V0 voltage regulator internal resistance ratio register value and (1+ Rb/Ra) ratio (Reference value) Table 12. Rb/Ra ratio

|    |    |    |       |                |     | 101 |          |                                                    |

|----|----|----|-------|----------------|-----|-----|----------|----------------------------------------------------|

|    |    | Re | giste | r <b>RR[</b> 1 | :0] |     |          | Equipment Type by Thermal Gradient<br>[Units:%/°C] |

| D7 | D6 | D5 | D4    | D3             | D2  | D1  | D0       | -0.05                                              |

| 0  | 1  | 1  | 0     | 0              | 0   | 0   | 0        | 125                                                |

| 0  | 1  | 1  | 0     | 0              | 0   | 0   |          | 2.9 (default)                                      |

| 0  | 1  | 1  | 0     | 0              | 0   |     | <b>0</b> | 3.2                                                |

| 0  | 1  | 1  | 0     | 0              | 0   | 1   | 1        | 3.5                                                |

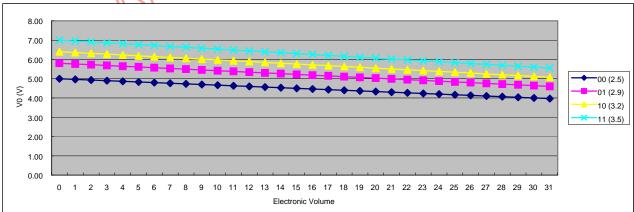

The V0 voltage as a function of the V0 voltage regulator internal resistor ratio register and the electronic volume register.

Note: When selecting external Rb/Ra resistors, Ra+Rb should be greater than 1.5M.

# Figure 14. The Contrast Curve of V0 Voltage with internal resistors

Setup example: When selecting  $Ta = 25^{\circ}C$  and V0 = 5V for an NT7607 model on which internal resistor is used. The equation A-1, the following setup is enabled.

| Contents             |    | Register |    |    |    |    |    |    |  |  |  |

|----------------------|----|----------|----|----|----|----|----|----|--|--|--|

| Contents             | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| Internal Rb/Ra ratio | 0  | 1        | 1  | 0  | 0  | 0  | 0  | 1  |  |  |  |

| Electronic Volume    | 0  | 0        | 0  | 1  | 0  | 1  | 0  | 1  |  |  |  |

#### Table 13. Example of V0 Voltage Adjust

- When the V0 voltage regulator internal resistors or the electronic volume function is used, it is necessary to at least set the voltage regulator circuit and the voltage follower circuit to an operating mode using the power control set commands. Moreover, it is necessary to provide a voltage from VOUT when the Booster circuit is OFF.

- The VR terminal is enabled only when the V0 voltage regulator internal resistors are not used (i.e. the IRS terminal = "L"). When the V0 voltage regulator internal resistors are used (i.e. when the IRS terminal = "H"), then the VR terminal is left open.

- Because the input impedance of the VR terminal is high, it is necessary to take into consideration short leads, shield cables, etc. to handle noise.

# The Liquid Crystal Voltage Generator circuit (Volatage Follower & Bias)

The V0 voltage is produced by a resistive voltage divider within the IC, and can be produced at the V1, V2, V3, and V4 voltage levels required for liquid crystal driving. Moreover, when the voltage follower changes the impedance, it provides V1, V2, V3, and V4 to the liquid crystal drive circuit. 1/4 bias or 1/5 bias for NT7607 can be selected by instruction.

# Reference power supply circuit for driving LCD panel

2006/12/07

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

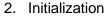

#### **Power-on reset and Initial State**

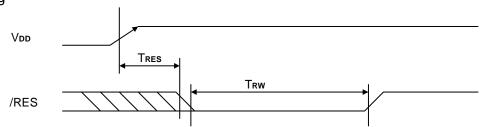

The NT7607 must be reset externally by /RES pin when power is turned on. The external reset is low active. After the reset the chip has the state shown in Table 14.

| Iable 14. State after reset              |                   |                                                                        |  |  |  |  |  |  |  |

|------------------------------------------|-------------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Function                                 | Control bit state | Remarks                                                                |  |  |  |  |  |  |  |

|                                          | D = 0             | Display off                                                            |  |  |  |  |  |  |  |

| Display control set                      | C = 0             | Cursor off                                                             |  |  |  |  |  |  |  |

|                                          | B = 0             | Cursor character blink off                                             |  |  |  |  |  |  |  |

| Power save set                           | OS = 0            | Oscillator off                                                         |  |  |  |  |  |  |  |

| Fower save set                           | PS = 0            | Power save off                                                         |  |  |  |  |  |  |  |

|                                          | VC = 0            | Voltage DC-DC converter OFF                                            |  |  |  |  |  |  |  |

| Power control set                        | VR = 0            | Voltage regulator OFF                                                  |  |  |  |  |  |  |  |

|                                          | VF = 0            | Voltage follower OFF                                                   |  |  |  |  |  |  |  |

|                                          | N = 0             | 2-line display                                                         |  |  |  |  |  |  |  |

| Function set                             | S = 0             | COM left shift                                                         |  |  |  |  |  |  |  |

|                                          | CG = 0            | CGRAM is not used. CGROM is used.                                      |  |  |  |  |  |  |  |

| Return home                              | -                 | Address counter (AC) = 00H                                             |  |  |  |  |  |  |  |

| V0 Regulator Internal Resistor Ratio Set | RR [1:0]=01       | Internal resistor ratio (1+Rb/Ra) = 2.9                                |  |  |  |  |  |  |  |

| Electronic contrast control register     |                   | 10H = (0,0,0,0,0)                                                      |  |  |  |  |  |  |  |

| Frame Frequency Select                   | FS=0              | Frame Frequency = 80Hz                                                 |  |  |  |  |  |  |  |

| In case of 4-bit mode                    |                   | NT7607 considers the first 4-bit data from MPU as the high order bits. |  |  |  |  |  |  |  |

#### Table 14. State after reset

Note: If initialization is not done by /RES pin at application, unknown condition might result.

# Commands

Only the Instruction Register (IR), the Data Register (DR) and output Data Register (OR) can be directly controlled by the MPU. Before internal operation, control information is stored temporarily in these registers, to allow interfacing to various types of MPU that operates at different speeds or to allow interface to peripheral control ICs.

#### Instruction set

#### 1. Return Home

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex        |

|----|----|----|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | -  | 02h to 03h |

Return home instruction field makes cursor return home.

DDRAM address is set to 00H from AC and the cursor returns to 00H position. The contents of DDRAM are not changed

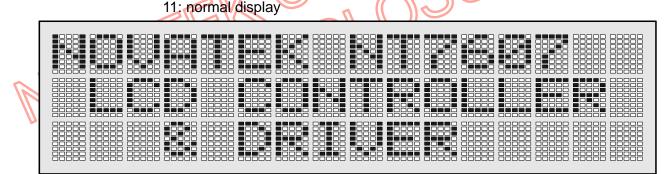

#### 2. Double Height Mode

|      | 0  |    |    |    |    |    |     |     |            |

|------|----|----|----|----|----|----|-----|-----|------------|

| RS   | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Hex        |

| 0    | 0  | 0  | 0  | 0  | 1  | 0  | DH2 | DH1 | 08h to 0Bh |

| <br> |    | -  |    |    |    |    |     |     |            |

Double height mode instruction field selects double height line type.

When DH2 DH1 = 00: normal display (default)

01: COM1 ~ COM16 is a double height, COM17 ~ COM24 is normal

- 10:1) 2-line mode: normal display

- 2) 3-line mode COM1 ~ COM8 is normal, COM9 ~ COM24 is a double height.

Figure 19. 3-Line Normal Mode Display (DH2, DH1 = 00)

Figure 20. COM1 ~ COM16 is a Double Height Line, COM17 ~ COM24 is Normal (DH2, DH1 = 01)

2006/12/07 28 Ver 2.0 With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

Figure 21. COM1 ~ COM8 is Normal, COM9 ~ COM24 is a Double Height Line (DH2, DH1 = 10)

Figure 23. COM1 ~ COM16 is a Double Height Line (DH2, DH1 + 01)

#### 3. Power Save Set

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 👖 Hex      |

|----|----|----|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 0  | 1  |    | os | PS | 0Ch to 0Fh |

|    | -  |    |    |    |    |    |    |    |            |

Power save instruction field is used to control the oscillator and set or to reset the power save mode.

OS: oscillator ON/OFF control bit

When OS = "L", oscillator is turned OFF (default)

When OS = "H", oscillator is turned ON.

PS: power save ON/OFF control bit

When PS = "L": power save is turned OFF (default).

When PS = "H": power save is turned ON.

LCD

#### 4. Function Set

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex        |

|----|----|----|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 1  | 0  | Ν  | S  | CG | 10h to 17h |

N: display line mode instruction field selects 2-line or 3-line display mode

When N = "L": 2-line display mode (default)

When N = "H": 3-line display mode

S: data shift direction of common, S sets the shift direction of common display data When S = "L", COM left shift (default)

When S = "H", COM right shift (Refer to Table 7)

#### CG: CGRAM enable bit

When CG = "L", CGRAM is disable. CGROM (00H~07H) can be accessed and additional current consumption is saved by using this mode (default). (00H~07H = CGROM font display) When CG = "H", CGRAM can be accessed and you can use this RAM for eight special character area. (00H~07H = CGRAM font display)

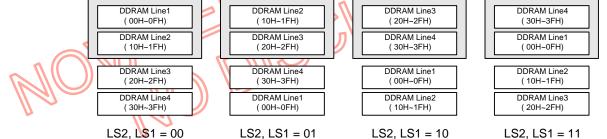

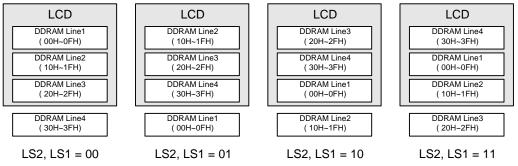

#### 5. Line Shift Mode

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Hex        |

|----|----|----|----|----|----|----|-----|-----|------------|

| 0  | 0  | 0  | 0  | 1  | 1  | 0  | LS2 | LS1 | 18h to 1Bh |

Line shift mode instruction field selects the DDRAM to be displayed in the first line.

When LS2, LS1 = 00: DDRAM line 1 shows at the first line of LCD (default).

#### 01: DDRAM line 2 shows at the first line of LCD.

Figure 24. 2-Line Shift Mode Display at 2 Line LCD

#### 6. Bias Control

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex        |

|----|----|----|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | -  | BS | 1Ch to 1Fh |

Bias Control instruction field sets LCD bias voltages generated internally.

BS: The bit is used when the internal voltage follower is ON

When BS = "L": 1/5 bias (default)

When BS = "H": 1/4 bias (V2 = V3)

#### 7. Power Control Set

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex        |

|----|----|----|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 1  | 0  | 0  | VC | VR | VF | 20h to 27h |

Power Control instruction field sets voltage converter / regulator / follower ON / OFF.

VC: voltage converter circuit control bit

When VC = "L": voltage booster is turned OFF (default)

When VC = "H": voltage booster is turned ON

VR: voltage regulator circuit control bit

When VR = "L": voltage regulator is turned OFF (default)

When VR = "H": voltage regulator is turned ON

VF: voltage follower circuit control bit

When VF = "L": voltage follower is turned OFF (default)

When VF = "H": voltage follower ON

Note: The oscillation circuit must be turned on for the voltage converter circuit to be active.

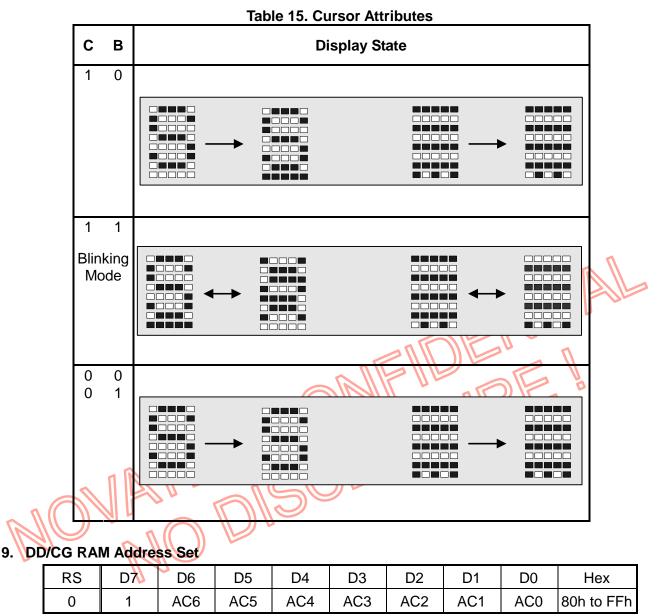

#### 8. Display Control

| RS | D7 D6 | D5 |   | D3 | <b>D</b> 2 | D1 | D0 | Hex        |

|----|-------|----|---|----|------------|----|----|------------|

| 0  | 0 0   | 1  | G | 1  | С          | В  | D  | 28h to 2Fh |

Display control instruction field controls cursor /blink/display ON/OFF.

C: cursor ON /OFF control bit

When C = "L", cursor is disappeared in current display (default). When C = "H", cursor is turned ON.

B: cursor blink ON/OFF control bit

When C = "H" and B = "H", NT7607 make LCD alternate between inverting display character and normal display character at the cursor position with about a half second. On the contrary, if C = "L", only a normal character is displayed regardless of "B" flag.

When B = "L", blink is OFF (default).

D: display ON/OFF control bit

When D = "L", Display is turned OFF. But display data are remained in DDRAM (default). When D = "H", Entire display in turned ON.

DD/CG RAM Address set instruction fields DDRAM/CGRAM address Before writing / reading data into /from RAM, set address by RAM Address Set Instruction. Next when data are written / read in succession. The address is automatically increased by 1. For accessing DD/ CGRAM, the DD/CGRAM Address Set Instruction should be set before. After accessing 7FH, the address of AC is 00H.

#### The address range are 00H ~ 7FH.

| Address | 0 | 1 | 2   | 3    | 4    | 5     | 6   | 7      | 8    | 9     | Α    | В    | С     | D     | Ε  | F |

|---------|---|---|-----|------|------|-------|-----|--------|------|-------|------|------|-------|-------|----|---|

| 00H     |   |   |     |      |      | DDR   | RAM | line   | 1(00 | H ~ ( | 0FH) | )    |       |       |    |   |

| 10H     |   |   |     |      |      | DDR   | RAM | line   | 2(10 | H ~ 1 | 1FH) | )    |       |       |    |   |

| 20H     |   |   |     |      |      | DDR   | RAM | line   | 3(20 | H ~ 2 | 2FH) | )    |       |       |    |   |

| 30H     |   |   |     |      |      | DDR   | RAM | line · | 4(30 | H ~ 3 | 3FH) | )    |       |       |    |   |

| 40H     |   | 0 | CGR | AM ( | patt | ern ( | ))  |        |      | C     | GR   | AM ( | patte | ern 1 | I) |   |

| 50H     |   | 0 | CGR | AM ( | patt | ern 2 | 2)  |        |      | C     | GR   | AM ( | patte | ern 3 | 3) |   |

| 60H     |   | 0 | CGR | AM ( | patt | ern 4 | 1)  |        |      | C     | GR   | AM ( | patte | ern 5 | 5) |   |

| 70H     |   | ( | CGR | AM ( | patt | ern 6 | 5)  |        |      | C     | GR   | AM ( | patte | ern 7 | 7) |   |

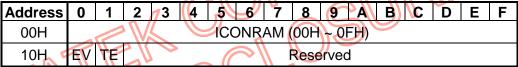

#### 10. ICONRAM Address Set

| RS | D7 | D6 | D5 | D4  | D3  | D2  | D1  | D0  | Hex                      |

|----|----|----|----|-----|-----|-----|-----|-----|--------------------------|

| 0  | 0  | 1  | 0  | IA4 | IA3 | IA2 | IA1 | IA0 | 40h to <mark>5</mark> Fh |

ICONRAM Address Set instruction fields ICONRAM / Registers address.

Before writing / reading data into /from ICON RAM, set the address by ICONRAM Address Set Instruction. Next when data are written / read in succession. The address is automatically increased by 1. For accessing ICONRAM, the ICONRAM Address Set Instruction should be set before. After accessing 0FH, the address of ICONRAM address is 00H. The ICONRAM address range are 00H ~ 1FH.

The 5 icons at a time can blink, if C and B bits of the display instructions are enabled. The blink attributes of ICON are same as the cursor blink.

EV: electronic volume register (10H) ~ default (00000) TE: test register (Do not use)(11H)

# 11. Write Data

| RS | D7 | 5 D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex |

|----|----|------|----|----|----|----|----|----|-----|

| 1  | D7 | D6   | D5 | D4 | D3 | D2 | D1 | D0 | XX  |

The instruction field makes NT7607 write binary 8-bit data to DDRAM/CGRAM/ICONRAM or register. The RAM address to be written into is determined by previous DD/CGRAM Address Set instruction. After writing operation, the address is automatically increased by 1.

#### 12. Read Data

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex |

|----|----|----|----|----|----|----|----|----|-----|

| 1  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | XX  |

#### DDRAM/CGRAM/ICONRAM data read instruction.

Each RAM is selected by address set instruction. And then you can read the RAM data. You can get correct RAM data from second read transaction. The first read data after setting RAM address is dummy data; so the correct RAM data come from the second read transaction. After reading operation, the address is increase by 1 automatically.

#### 13. NOP

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex |

|----|----|----|----|----|----|----|----|----|-----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00h |

**Non-Operation Instruction**

#### 14. V0 Regulator Internal Resistor Ratio Set

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Hex        |

|----|----|----|----|----|----|----|-----|-----|------------|

| 0  | 0  | 1  | 1  | 0  | 0  | 0  | RR1 | RR0 | 60h to 63h |

This command sets the V0 voltage regulator internal resistor ratio. For details, see explanation under "LCD supply voltage generator".

#### Table 16. Rb/Ra Ratio

| cy Selec | t   |                 | V |

|----------|-----|-----------------|---|

| 1        | 1   | 3.5             | Π |

| 1        | 0   | 3.2             |   |

| 0        | 1   | 2.9 (default)   |   |

| 0        | 0   | 2.5             |   |

| RR1      | RR0 | (1+Rb/Ra) Ratio | n |

#### **15. Frame Frequency Select**

| RS | D7 | D6 | D5 | D4 | D3 D2 | D1 | DO | Hex        |

|----|----|----|----|----|-------|----|----|------------|

| 0  | 0  | 1  |    | θ  | 1     | 0  | FS | 68h to 69h |

|    |    |    |    |    |       |    |    |            |

| FS | -rame Freq   | uency     |

|----|--------------|-----------|

| 0  | <b>80</b> Hz | (Default) |

| 5  | 67Hz         |           |

|    |              |           |

#### 16. Test Instruction

| RS | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex        |

|----|----|----|----|----|----|----|----|----|------------|

| 0  | 0  | 0  | 1  | 1  | *  | *  | *  | *  | 30h to 3Fh |

This is the dedicate IC chip test instruction. It must not be used for normal operation.

|                       |    |    |    |    | Co |    |    |     |     |                  |                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|----|----|----|----|----|----|----|-----|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction           | RS | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Hex              | Function                                                                                                                                                                                                                                                                                                                                                           |

| Return Home           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1   | -   | 02h<br>to<br>03h | DDRAM address is set to 00h from AC and<br>the cursor returns to 00h position.<br>The contents of DDRAM are not changed                                                                                                                                                                                                                                            |

| Double Height<br>Mode | 0  | 0  | 0  | 0  | 0  | 1  | 0  | DH2 | DH1 | 08h<br>to<br>0Bh | <ul> <li>Double height mode</li> <li>DH2 DH1 =</li> <li>00: normal display (default)</li> <li>01: COM1 ~ COM16 is a double height.<br/>COM17 ~ COM24 is normal</li> <li>10: 1) 2-line mode: normal display</li> <li>2) 3-line mode:</li> <li>COM1 ~ COM8 is normal and</li> <li>COM9 ~ COM24 is a double height.</li> <li>11: normal display</li> </ul>            |

| Power Save            | 0  | 0  | 0  | 0  | 0  | 1  | 1  | OS  | PS  | 0Ch<br>to<br>0Fh | Power save/oscillation circuit ON/OFF<br>OS = 0: oscillator OFF (default)<br>OS = 1: oscillator ON<br>PS = 0: power save OFF (default)<br>PS = 1: power save ON                                                                                                                                                                                                    |

| Function Set          | 0  | 0  | 0  | 0  | 1  | Ç  | N  | S   | ce  | 10h<br>to<br>17h | Display line mode<br>N = 0: 2-line display mode (default)<br>N = 1: 3-line display mode<br>Shifting direction of COM<br>S = 0: 1) 2-line mode: COM1 ~ COM16<br>(default)<br>2) 3-line mode: COM1 ~ COM24<br>S = 1: 1) 2-line mode: COM16 ~ COM1<br>2) 3-line mode: COM24 ~ COM1                                                                                    |

| MONA                  |    |    | Ľ  | T  | )  |    |    | J`  |     |                  | Select CGRAM or CGROM<br>CG = 0: CGROM (default)<br>CG = 1: CGRAM                                                                                                                                                                                                                                                                                                  |

| Line Shift Mode       | 0  | 0  | 0  | 0  | 1  | 1  | 0  | LS2 | LS1 | 18h<br>to<br>1Bh | Determination of the DDRAM line, which is<br>displayed at the first line at LCD.<br>LS2, LS1 = 00: DDRAM line 1 shows at<br>(default) the first line of LCD.<br>LS2, LS1 = 01: DDRAM line 2 shows at the<br>first line of LCD.<br>LS2, LS1 = 10: DDRAM line 3 shows at the<br>first line of LCD.<br>LS2, LS1 = 11: DDRAM line 4 shows at the<br>first line of LCD. |

| Bias Control          | 0  | 0  | 0  | 0  | 1  | 1  | 1  | -   | BS  | 1Ch<br>to<br>1Fh | Determination of Bias<br>BS = 0: 1/5 bias (default)<br>BS = 1: 1/4 bias                                                                                                                                                                                                                                                                                            |

#### Table 17. Instruction Table

| la staveti su                                  |    |    |     |     | C   | ode |     |     |     |                  | Franction                                                                                                                                                                                                                                        |

|------------------------------------------------|----|----|-----|-----|-----|-----|-----|-----|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                                    | RS | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Hex              | Function                                                                                                                                                                                                                                         |

| Power Control                                  | 0  | 0  | 0   | 1   | 0   | 0   | VC  | VR  | VF  | 20h<br>to<br>27h | LCD power control<br>VC = 0: voltage converter OFF (default)<br>VC = 1: voltage converter ON<br>VR = 0: voltage regulator OFF (default)<br>VR = 1: voltage regulator ON<br>VF = 0: voltage follower OFF (default)<br>VF = 1: voltage follower ON |

| Display Control                                | 0  | 0  | 0   | 1   | 0   | 1   | С   | В   | D   | 28h<br>to<br>2Fh | Cursor/ blink /display ON/OFF<br>C = 0: cursor OFF (default) 1: cursor ON<br>B = 0: blink OFF (default) 1:blink ON<br>D = 0: display OFF (default) 1:display ON                                                                                  |

| DD/CGRAM<br>Address Set                        | 0  | 1  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | 80h<br>to<br>FFh | DDRAM/CGRAM Range:<br>DDRAM 00h~3FH, CGRAM 40h~7FH                                                                                                                                                                                               |

| ICONRAM Address<br>Set                         | 0  | 0  | 1   | 0   | IA4 | IA3 | IA2 | IA1 | IA0 | 40h<br>to<br>5Fh | ICONRAM address, electronic volume and<br>test byte address<br>Range: ICONRAM 00H~0FH<br>EV 10H (Electronic volume byte)<br>TE 11H (Test byte)                                                                                                   |

| Write Data                                     | 1  | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | хх               | Write DDRAM/CGRAM/ICONRAM                                                                                                                                                                                                                        |