# NT7573

**Data Sheet**

132RGB X 132 RAM-Map STN LCD Controller/Driver for 65K Colors

> V0.03 Preliminary

NOVATEK 聯 詠 科 性

#### Features

- 132RGB x 132-dot graphics display LCD controller/driver for 65,536 STN colors

- RAM capacity: 132 x 16 x 132 = 278,784 bits

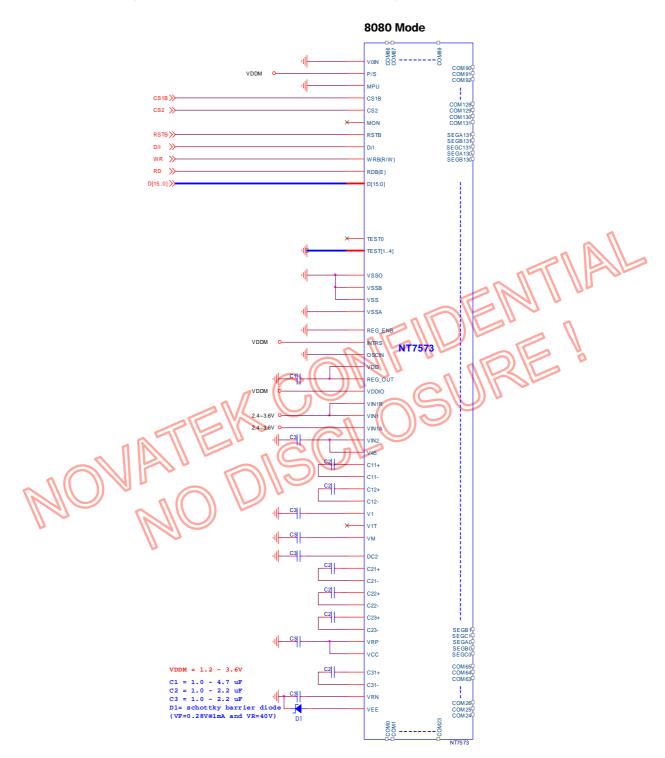

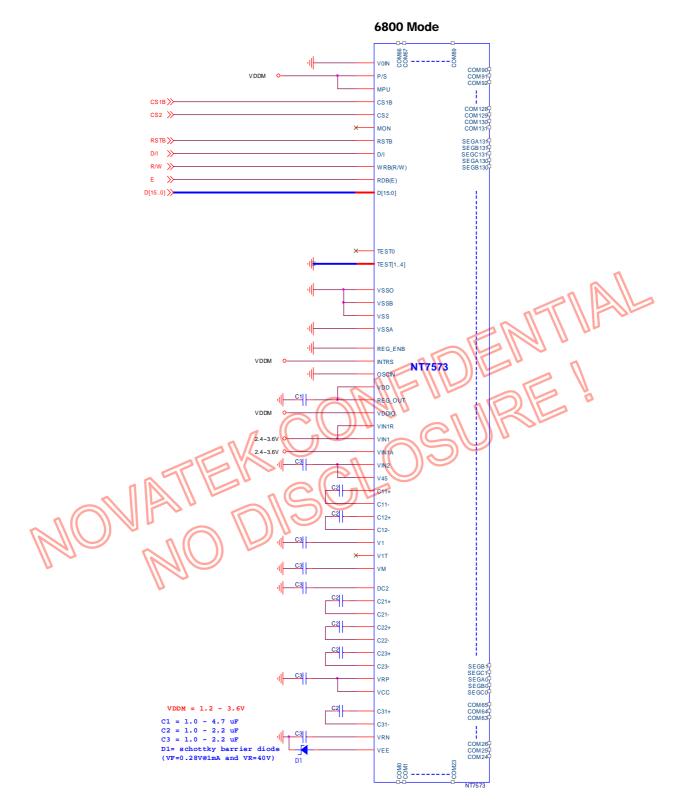

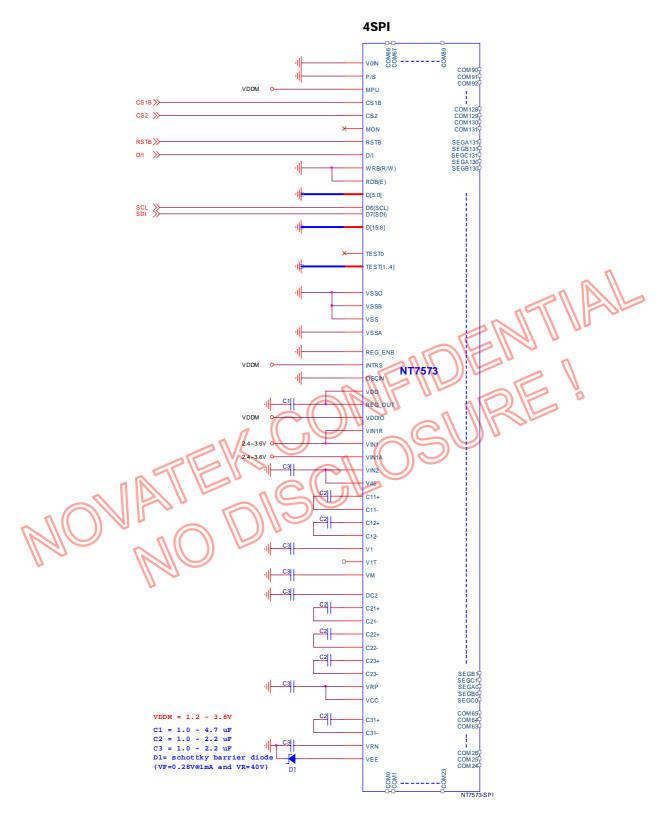

- 8-bit/16-bit parallel bus interface for both 8080 and 6800 series, 3-wire/4-wire Serial Peripheral Interface (SPI)

- 65,536 colors can be displayed at the same time by PWM and FRC

- Data output scan direction controlled by software commands

- Shift change of common drivers

- RAM addressing direction control (vertical and horizontal)

- Power supply voltage:

- VDDIO =  $1.2 \sim 3.6 \text{ V}$  (power supply for interface circuit)

- = 1.65 ~ 1.95 V (power supply for digital circuit) - VDD

- VIN1/VIN1A//VIN1R = 2.4 ~ 3.6 V (power supply for 1<sup>st</sup> booster circuit, VM Amp and regulator.)

- V1 =  $2.0 \sim 3.3$  V (power supply for Segment Driver)

- = 19.8 V Max.(power supply for Common Driver) - VCC-VEE

- On chip LCD driving voltage generator or external power supply selectable

- 256-step contrast adjuster and on chip voltage follower

- Programmable drive duty ratios (1/33, 1/66, 1/96, 1/108, 1/120, 1/132) and bias values (1/4-1/6)

- Programmable partial display, screen scrolling

- N-block inversion AC liquid-crystal drive

- On chip oscillation and hardware reset

- Multi-Time Programming (2 times) for V1 voltage

- Available in COG form

- CMOS process

#### **General Description**

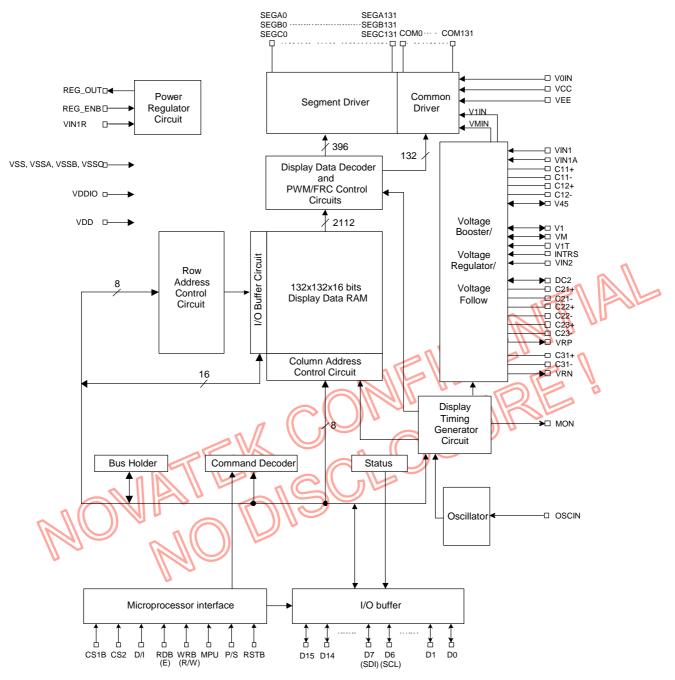

The NT7573 is a single-chip LCD controller/driver LSI for color-graphics, which displays 132 x 132-dot graphics for 65,536 STN colors. It accepts display data through 8-bit/16-bit parallel (8080 or 6800 series) or serial (3-wire or 4-wire) interface directly sent from a µC and stores it in an on-chip display data RAM.

The NT7573 contains 132 common output circuits and 132 x 3 segment output circuits. The capacity of the on-chip display data RAM is 132 x 132 x 16 bits and every 16-bit corresponds to one pixel (include RGB) LCD panel. It generates an LCD drive signal independent of the MPU clock.

No external operation clock is required for RAM read/write operations. Accordingly, this driver can be operated with a minimum current consumption. It can implement a high-performance handy display system with minimum current consumption and the smallest LSI configuration.

NT7573

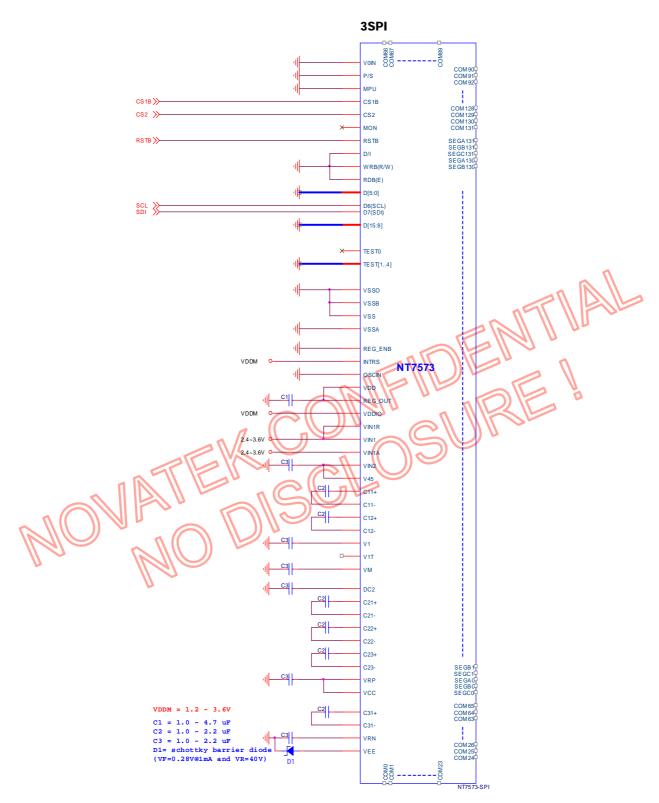

#### **Pad Configuration**

2006/03/23

#### **Block Diagram**

#### 2006/03/23

#### **Pad Descriptions**

#### **Power Supply**

| Pad No.                     | Designation | I/O    | Description                                                                                                                                                                     |  |  |  |  |  |  |  |

|-----------------------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 134~136                     | VDDIO       | Supply | Main power supply                                                                                                                                                               |  |  |  |  |  |  |  |

| 10, 20, 35,<br>120          | VDDIO       | 0      | Main power supply for pad option                                                                                                                                                |  |  |  |  |  |  |  |

| 126~130                     | VDD         | Supply | Power supply for internal digital and DDRAM block<br>This pin is connected to REG_OUT with stabilization capacitor<br>When internal regulator is not used, connect VDD to VDDIO |  |  |  |  |  |  |  |

| 5~7,<br>257~259,<br>107~111 | VSS         |        |                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 112~116                     | VSSA        | Supply | Ground. All pads must be connected to ground                                                                                                                                    |  |  |  |  |  |  |  |

| 102~106                     | VSSB        |        |                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 99~101                      | VSSO        |        |                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 13, 28, 117,<br>125         | VSS         | 0      | Ground for pad option                                                                                                                                                           |  |  |  |  |  |  |  |

| 137~140                     | VIN1R       | Supply | Internal regulator power supply                                                                                                                                                 |  |  |  |  |  |  |  |

| 141~145                     | VIN1        |        | Power supply for 1 <sup>st</sup> booster circuit and VM amplifier                                                                                                               |  |  |  |  |  |  |  |

| 146~148                     | VIN1A       | I      | Tower supprision poosier circuit and war anipinter                                                                                                                              |  |  |  |  |  |  |  |

| 149~152                     | VIN2        |        | Power supply for DC2 amplifier                                                                                                                                                  |  |  |  |  |  |  |  |

| 153~156                     | V45         | 0      | 1 <sup>st</sup> booster output pin, and Multi-Time Programming pin                                                                                                              |  |  |  |  |  |  |  |

| 100~100                     |             |        | Power supply for V1 (1 <sup>st</sup> booster off)                                                                                                                               |  |  |  |  |  |  |  |

| 181~184                     | ) V1        | 0      | LCD segment high driving voltage output                                                                                                                                         |  |  |  |  |  |  |  |

| 101~104                     |             | ((1))  | LCD segment high driving voltage input (OP AMP off)                                                                                                                             |  |  |  |  |  |  |  |

| 187~190                     | VM          | 00     | LCD common non-selected driving voltage output                                                                                                                                  |  |  |  |  |  |  |  |

| 107~190                     | V IVI V     | Ι      | LCD common non-selected driving voltage input (OP AMP off)                                                                                                                      |  |  |  |  |  |  |  |

| 192~196                     | DC2         | 0      | Power output pin for 2 <sup>nd</sup> booster circuit input                                                                                                                      |  |  |  |  |  |  |  |

| 192~190                     | 002         | Ι      | Power supply for 2 <sup>nd</sup> booster circuit (OP AMP off)                                                                                                                   |  |  |  |  |  |  |  |

| 2~4,<br>260~262             | V0IN        | Ι      | LCD segment low driving voltage input                                                                                                                                           |  |  |  |  |  |  |  |

| 233~235                     | VRP         | 0      | LCD common high selected driving voltage output                                                                                                                                 |  |  |  |  |  |  |  |

| 236~238                     | VCC         |        | LCD common high selected driving voltage input                                                                                                                                  |  |  |  |  |  |  |  |

| 251~253                     | VRN         | 0      | LCD common low selected driving voltage output                                                                                                                                  |  |  |  |  |  |  |  |

| 254~256                     | VEE         | Ι      | LCD common low selected driving voltage input                                                                                                                                   |  |  |  |  |  |  |  |

#### 2006/03/23

#### **Power Supply (continuous)**

| Pad No.                                                             | Designation                                       | I/O | Description                                                                 |

|---------------------------------------------------------------------|---------------------------------------------------|-----|-----------------------------------------------------------------------------|

| 157~162,<br>163~168,<br>169~174,<br>175~180                         | C11+,<br>C11-,<br>C12-,<br>C12+                   | 0   | External capacitor connection pins used for 1 <sup>st</sup> booster circuit |

| 197~202,<br>203~208,<br>209~214,<br>215~220,<br>221~226,<br>227~232 | C21+,<br>C21-,<br>C22-,<br>C22+,<br>C23+,<br>C23- | 0   | External capacitor connection pins used for 2 <sup>nd</sup> booster circuit |

| 239~244,<br>245~250                                                 | C31+,<br>C31-                                     | 0   | External capacitor connection pins used for 3 <sup>rd</sup> booster circuit |

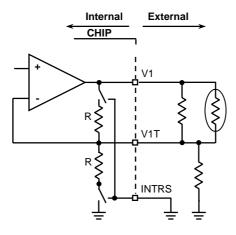

| 185, 186                                                            | V1T                                               | I   | Thermistor resistor connection pin                                          |

Note: The IN / OUT settings of V45, DC2, V1, VM are controlled by DC/DC and AMP ON/OFF Set command.

\* Make sure of the relationship of LCD driving voltage as follows:

(1) VCC > V1 > VM > V0IN (=VSS) > VEE

#### **LCD Driver Pads**

| (1) $VCC > VT > VM > VON (= VS3) > VEE$<br>(2) $VCC - VM = VM - VEE, V1 - VM = VM - VOIN$<br>LCD Driver Pads |                                              |     |                                                      |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|------------------------------------------------------|--|--|--|--|--|--|--|

| Pad No.                                                                                                      | Designation                                  | I/O | Description                                          |  |  |  |  |  |  |  |

|                                                                                                              | SEGA0 ~<br>SEGA131                           | 0   | Segment signal outputs for LCD display (Red or Blue) |  |  |  |  |  |  |  |

| 333~728                                                                                                      | SEGB0 ~<br>SEGB131                           | 0   | Segment signal outputs for LCD display (Green)       |  |  |  |  |  |  |  |

|                                                                                                              | SEGC0~<br>SEGC131                            | 0   | Segment signal outputs for LCD display (Blue or Red) |  |  |  |  |  |  |  |

| 265~288,<br>290~331,<br>730~771,<br>773~796                                                                  | COM0~23<br>COM24~65<br>COM131~90<br>COM89~66 | Q   | Common signal outputs for LCD display                |  |  |  |  |  |  |  |

#### **Configuration Pads**

| Pad No.  | Designation | I/O | Description                                                                                                                                 |

|----------|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| 121, 122 | INTRS       | I   | External resistor select for temperature compensation circuit<br>INTRS ="L" : external resistor mode<br>INTRS ="H" : internal resistor mode |

2006/03/23

Ver 0.03 With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

#### **System Bus Connection**

| Pad No. | Designation                                 | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------|---------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 23, 24  | RSTB                                        | I   | Reset input pin.<br>When RSTB is set to "L", the settings are initialized.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 8, 9    | P/S                                         | I   | MPU interface select pin.<br>When P/S is "H"<br>MPU = "L": 8080 series MPU interface<br>MPU = "H": 6800 series MPU interface                                                                                                                                                                                                                                                                   |  |  |  |  |

| 11, 12  | MPU                                         | I   | When P/S is "L"<br>MPU = "L": 3 pin SPI (Write only)<br>MPU = "H": 4 pin SPI (Write only)                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 14~16   | CS1B                                        | I   | Chip select input pin.<br>When CS1B is "L" and CS2 is "H", the data / command I/O is                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 17~19   | CS2                                         | I   | enabled. When chip select is non-active, D0 to D15 are high impedance                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 25~27   | D/I                                         | I   | Data / Command select input pin.<br>D/I = "H": Indicates that D0 to D15 are display data<br>D/I = "L": Indicates that D0 to D15 are control data                                                                                                                                                                                                                                               |  |  |  |  |

| 29~31   | WRB<br>(R/W)                                | I   | When 6800 series MPU is selected, this is the read / write<br>control input pin.<br>R/W = "H": read<br>R/W = "L": write<br>When 8080 MPU is selected, this is the write enable clock<br>input pin. The data on D0 to D15 are latched at the rising edge<br>of the WRB signal.                                                                                                                  |  |  |  |  |

| 32~34   |                                             |     | <ul> <li>When 6800 series MPU is selected, this is the enable control input pin.</li> <li>R/W = "H": D0 to D15 are in output status when E is "H".</li> <li>R/W = "L": The data on D0 to D15 are latched at the falling edge of WRB signal</li> <li>When 8080 MPU is selected, this is the read enable clock input pin. The data on D0 to D15 are in output status when RDB is "L".</li> </ul> |  |  |  |  |

| 36~83   | D15 ~ D8<br>D7 (SDI)<br>D6 (SCL)<br>D5 ~ D0 | I/O | <ul> <li>When parallel interface is selected, D15 to D0 (D7 to D0) are serves as the 16-bit (8-bit) bi-directional data bus.</li> <li>When the serial interface is selected,</li> <li>D7 (SDI): serial data input pin. The data is latched at the rising edge of SCL signal.</li> <li>D6 (SCL): serial clock input pin.</li> </ul>                                                             |  |  |  |  |

#### **Timing Signal for Monitor**

| Pad No. | Designation | I/O | Description                                   |

|---------|-------------|-----|-----------------------------------------------|

| 21, 22  | MON         | 0   | Monitor signal output pin. (CL, FR, PM, SYNC) |

#### **Oscillator and Internal Regulator**

| Pad No.  | Designation | I/O | Description                                                                                                                            |  |  |  |  |  |  |

|----------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 123, 124 | OSCIN       | I   | External clock input pin when external clcok is used<br>When the internal RC oscillator is used, fixed this pin to<br>VDDIO or VSS     |  |  |  |  |  |  |

| 118, 119 | REG_ENB     | I   | Internal regulator enable pin<br>REG_ENB = "L": Enable internal regulator<br>REG_ENB = "H": Disable internal regulator                 |  |  |  |  |  |  |

| 131~133  | REG_OUT     | 0   | Internal regulator output pin<br>This output voltage is used as a power supply for the internal<br>digital and DDRAM block via VDD pin |  |  |  |  |  |  |

#### **Test Pads**

| Pad No.   | Designation | I/O | Description                         |

|-----------|-------------|-----|-------------------------------------|

| 84~86     | TEST0       | 0   | Test pads. No connection            |

| 87~98     | TEST1 ~ 4   | Ι   | Test pads. Must be connected to VSS |

| No Connec | ted Pads    |     |                                     |

|           |             |     |                                     |

#### **No Connected Pads**

| Pad No.                                            | Designation        | I/O | Description               |

|----------------------------------------------------|--------------------|-----|---------------------------|

| 1, 191, 263,<br>264, 289,<br>332, 729,<br>772, 797 | DUMMY0 ~<br>DUMMY8 | -   | Dummy pads. No connection |

| M                                                  | ONA<br>N           |     | A SCLOSE<br>DISCLOSE      |

"-" Must always be VDDIO or VSS

#### **Functional Descriptions**

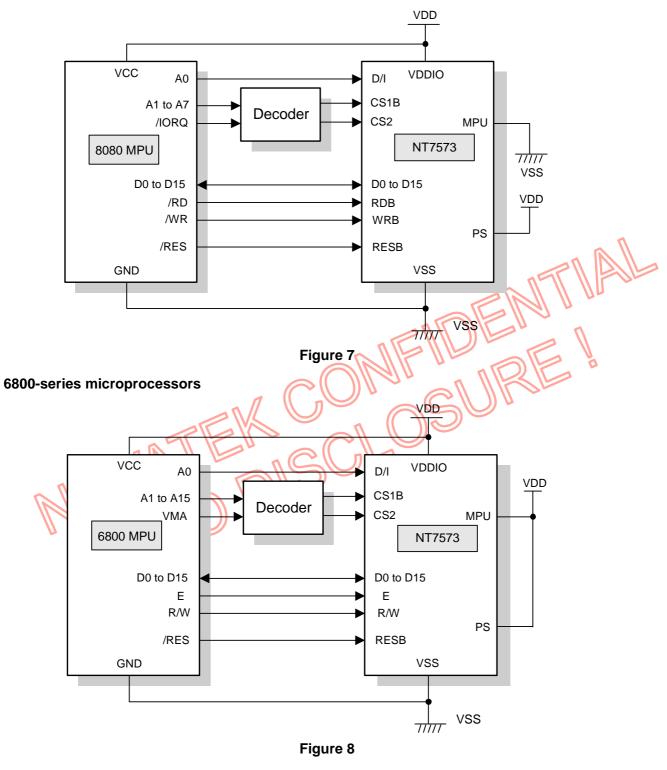

#### **Microprocessor Interface**

The NT7573 can transfer data via 16-bit bi-directional data bus (D15 to D0) or via serial data input (SDI). When high or low is selected for the parity of P/S, MPU pads and command bit 16B, either 8-bit/16-bit parallel data input or serial data input can be selected as shown in Table 1. When serial data input is selected, the RAM data cannot be read out.

| P/S | MPU | 16B | Туре               | CS1B | CS2 | D/I | RDB<br>(E) | WRB<br>(R/W) | D15 to D8 | D7  | D6  | D5 to D0 |

|-----|-----|-----|--------------------|------|-----|-----|------------|--------------|-----------|-----|-----|----------|

|     | L   | -   | 3-wire SPI         | CS1B | CS2 | -   | -          | -            | -         | SDI | SCL | -        |

|     | Н   | -   | 4-wire SPI         | CS1B | CS2 | D/I | -          | -            | -         | SDI | SCL | -        |

|     | L   | L   | 8080 series 8-bit  | CS1B | CS2 | D/I | RDB        | WRB          | -         | D7  | D6  | D5 to D0 |

| Н   | L   | Н   | 8080 series 16-bit | CS1B | CS2 | D/I | RDB        | WRB          | D15 to D8 | D7  | D6  | D5 to D0 |

|     | Н   | L   | 6800 series 8-bit  | CS1B | CS2 | D/I | Е          | R/W          | -         | D7  | D6  | D5 to D0 |

|     | Н   | Н   | 6800 series 16-bit | CS1B | CS2 | D/I | Е          | R/W          | D15 to D8 | D7  | D6  | D5 to D0 |

Table 1. Data Bus Interface Selection Mode

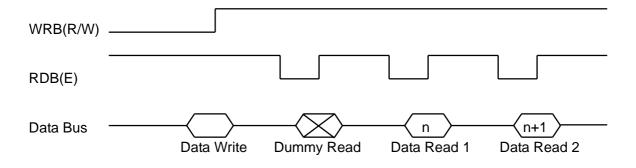

#### **Parallel Interface**

When the NT7573 selects parallel interface (P/S is high), the type of MPU interface is determined by MPU pad as shown in Table 1. The NT7573 identifies the data bus signal according to D/I, RDB (E), WRB (R/W) signals as shown in Table 2.

| Control | 6800 pr | ocessor | 8080 pr | ocessor | Function                |

|---------|---------|---------|---------|---------|-------------------------|

| D/I     | Е       | R/W     | RDB     | WRB     | I unclion               |

| 0       |         |         | 0       |         | Reads status            |

| 0       | (1)     | N N     |         | 0       | Writes instruction data |

| 1       | 1       | R       | 0       | 1       | Reads display data      |

| 1       | 1       | 0       | 1       | 0       | Writes display data     |

Table 2. Parallel Interface Read/Write Status

A dummy read is required before the first actual display data read for parallel interface.

2006/03/23

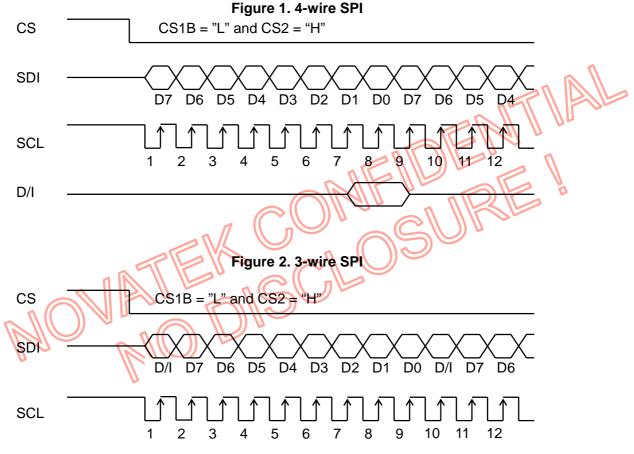

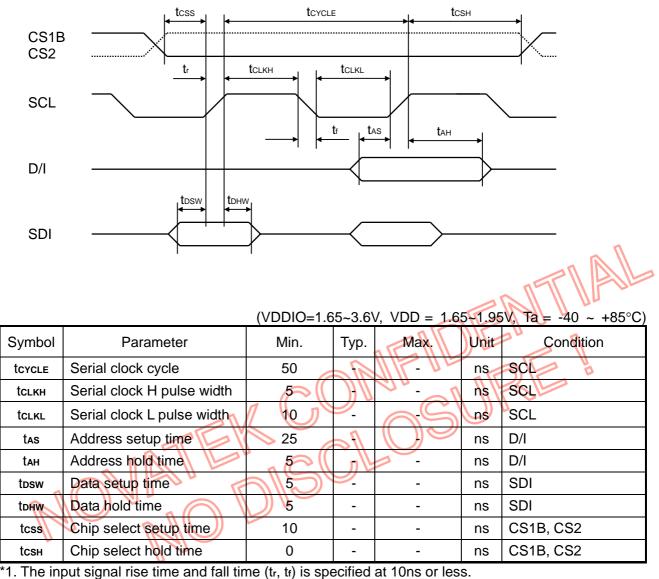

#### Serial Interface

When the serial interface has been selected (P/S is low), the 3-wire or 4-wire SPI can be selected by causing the MPU pad to go high or low.

In the 4-wire SPI, the serial data is read from the serial data input pin on the rising edge of the serial clocks in the order of D7, D6, D5, ....., D0. This data is converted to 8-bit parallel data on the rising edge of the eighth serial clock for processing. The D/I input is read on every 8th rising edge of the serial clock and used to determine whether the serial data input is specified as command or display data.

In the 3-wire SPI, the D/I pin is not used. The serial data is read from the serial data input pin on the rising edge of the serial clocks in the order of D/I, D7, D6, D5, ....., D0. This data is converted to 8-bit parallel data on the rising edge of the ninth serial clock for processing as command or display data that is determined by the first bit D/I.

#### Note:

- 1. When the chip is not active, the shift registers and the counter is reset to their initial states.

- 2. Reading is not possible while in serial interface mode.

- 3. Caution is required on the SCL signal when it comes to line-end reflections and external noise. We recommend the operation be rechecked on the actual equipment.

2006/03/23

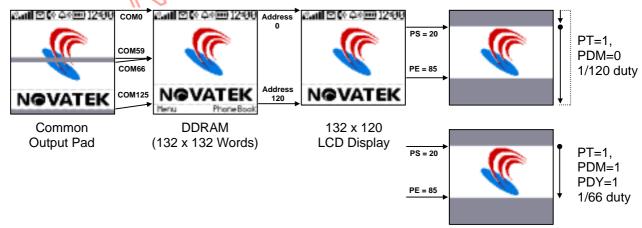

The display data RAM (DDRAM) is RAM that stores the dot data for the display. It has a 132 x 132 x 16 bit structure. The 16 bits of data are stored into the DDRAM to display one dot (Red: 5 bits, Green: 6 bits, Blue: 5 bits) for 65,536 colors. It is controlled by row and column addresses. RAM area selection and automatic address count modes are achieved by Row/Column Address Set and Entry Mode Set commands. Figure 3 shows the DDRAM addressing maps for the 8-bit parallel mode and 16-bit parallel mode.

Moreover, reading from and writing to the DDRAM from the MPU side is performed through the I/O buffer, which is an independent operation from signal reading for the liquid crystal driver.

#### Access to DDRAM and Internal Registers

The NT7573 can perform a series of pipeline processes between LSI's using the bus holder of the internal data bus in order to match the operating frequency of DDRAM and internal registers with the MPU. Also, the MPU temporarily stores display data in the bus holder, and stores it in DDRAM until the next data write cycle starts.

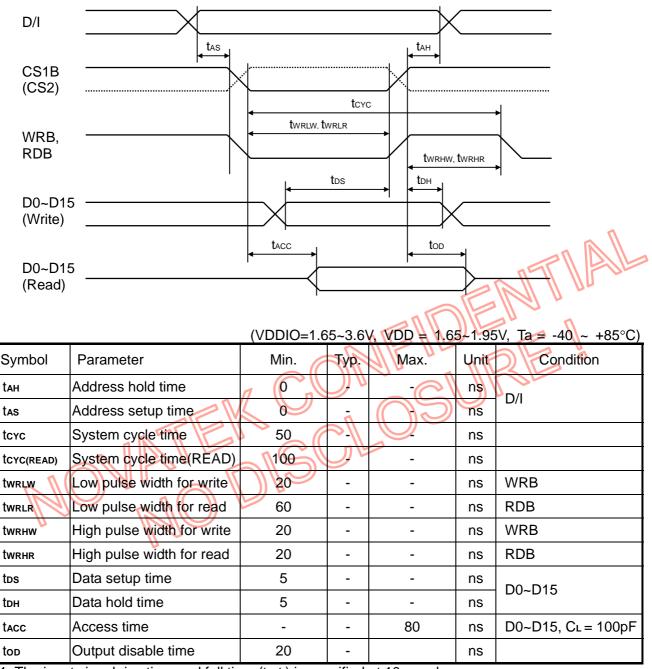

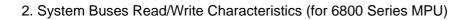

When viewed from the MPU, the NT7573 access speed greatly depends on the cycle time rather than access time to the DDRAM (tacc). This view shows that the data transfer speed to/ from the MPU can increase. If the cycle time is inappropriate, the MPU can insert the NOP instruction that is equivalent to the wait cycle setup.

However, when an address is set, the specified address data is not output immediately following the read instruction. The address data is output during the second data read. A single dummy read must be inserted after address setup and after the write cycle (refer to the Parallel Interface description).

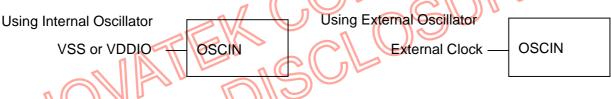

#### The Oscillator Circuit

The internal oscillator can produce the system clock. The oscillator circuit is only enabled when EXT=0. When EXT=1, the oscillation stops and the system clock is input through the OSCIN terminal.

#### **Display Timing Generator Circuit**

The display timing generator circuit generates the timing signal to the row address circuit and the display data decoder circuit using the system clock. Reading to the display data liquid crystal driver circuits is completely independent of access to the DDRAM by the MPU.

Moreover, the display timing generator circuit generates 4 type monitor signals from the system clock by setting Monitor Signal Control command. The 4 type monitor signals are common timing (CL), liquid crystal alternating current signal (FR), Field delimiter signal (PM), and Frame delimiter signal (SYNC).

## NT7573

#### Figure 3. Relationship Between DDRAM and Address

|                                                                                                           | 16-bit<br>Data Bus<br>Mode | D15<br>D14<br>D13<br>D12<br>D11 | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D4<br>D3<br>D2<br>D1<br>D0      | D15<br>D14<br>D13<br>D12<br>D11 | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D4<br>D3<br>D2<br>D1<br>D0      |             | D15<br>D14<br>D13<br>D12<br>D11 | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D4<br>D3<br>D2<br>D1<br>D0      | D15<br>D14<br>D13<br>D12<br>D11 | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D4<br>D3<br>D2<br>D1<br>D0      | SWP = 0                  |                 |                 |                 |                  |   |

|-----------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|-----------------------------------|---------------------------------|---------------------------------|-----------------------------------|---------------------------------|-------------|---------------------------------|-----------------------------------|---------------------------------|---------------------------------|-----------------------------------|---------------------------------|--------------------------|-----------------|-----------------|-----------------|------------------|---|

|                                                                                                           | 8-bit<br>Data Bus<br>Mode  | D7<br>D6<br>D5<br>D4<br>D3      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D4<br>D3<br>D2<br>D1<br>D0      | D7<br>D6<br>D5<br>D4<br>D3      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D4<br>D3<br>D2<br>D1<br>D0      |             | D7<br>D6<br>D5<br>D4<br>D3      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D4<br>D3<br>D2<br>D1<br>D0      | D7<br>D6<br>D5<br>D4<br>D3      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D4<br>D3<br>D2<br>D1<br>D0      |                          |                 |                 |                 |                  |   |

|                                                                                                           | 16-bit<br>Data Bus<br>Mode | D4<br>D3<br>D2<br>D1<br>D0      | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D15<br>D14<br>D13<br>D12<br>D11 | D4<br>D3<br>D2<br>D1<br>D0      | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D15<br>D14<br>D13<br>D12<br>D11 |             | D4<br>D3<br>D2<br>D1<br>D0      | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D15<br>D14<br>D13<br>D12<br>D11 | D4<br>D3<br>D2<br>D1<br>D0      | D10<br>D9<br>D8<br>D7<br>D6<br>D5 | D15<br>D14<br>D13<br>D12<br>D11 | SWP = 1                  |                 |                 |                 |                  | _ |

| COM Output<br>(CDR = 1)                                                                                   | 8-bit<br>Data Bus<br>Mode  | D4<br>D3<br>D2<br>D1<br>D0      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D7<br>D6<br>D5<br>D4<br>D3      | D4<br>D3<br>D2<br>D1<br>D0      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D7<br>D6<br>D5<br>D4<br>D3      |             | D4<br>D3<br>D2<br>D1<br>D0      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D7<br>D6<br>D5<br>D4<br>D3      | D4<br>D3<br>D2<br>D1<br>D0      | D2<br>D1<br>D0<br>D7<br>D6<br>D5  | D7<br>D6<br>D5<br>D4<br>D3      |                          |                 | COM<br>(CDR     | Output<br>= 0)  |                  |   |

| DL[1,0] DL[1,0] DL[1,0] DL[1,0]<br>= 11 = 10 = 01 = 00                                                    | Row<br>Address<br>MY = 1   | R                               | G                                 | В                               | R                               | G                                 | в                               |             | R                               | G                                 | В                               | R                               | G                                 | в                               | Row<br>Address<br>MY = 0 | DL[1,0]<br>= 00 | DL[1,0]<br>= 01 | DL[1,0]<br>= 10 | DL[1,0]          |   |

| COM131 COM125 COM119 COM113                                                                               | 131                        |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 0                        | COM0            | COM0            | COM0            | СОМО             |   |

| COM130 COM124 COM118 COM112<br>: : : : :                                                                  | 130                        |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 1                        | COM1            | COM1<br>:       | COM1            | COM1             | 2 |

| : : : : :<br>COM84 COM78 COM72 COM66                                                                      | :<br>84                    |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | :                        | :<br>COM47      | COM47           | COM47           | :<br>COM47       | - |

| COM83 COM77 COM71 COM47                                                                                   | 83                         |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 48                       | COM66           | COM48           | COM48           | COM48            |   |

| : : : : :<br>COM78 COM72 COM66 COM42                                                                      | :<br>78                    |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 | 25                              |                                   |                                 | ;<br>53                  | COM71           | :<br>COM53      | :<br>COM53      | :<br>COM53       | - |

| COM77         COM71         COM53         COM41                                                           | 77                         |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 | 1                                 | 1                               | 1                               |                                   |                                 | 54                       | COM72           | COM66           | COM54           | COM54            |   |

|                                                                                                           | :                          |                                 |                                   |                                 |                                 |                                   |                                 | 6           | <u>_</u>                        | $\mathcal{I}$                     |                                 |                                 | U                                 |                                 | :                        |                 | :               |                 | :                | ] |

| COM72         COM66         COM48         COM36           COM71         COM59         COM47         COM35 | 72<br>71                   |                                 |                                   |                                 |                                 |                                   |                                 | s ((        | $\mathcal{H}$                   |                                   | 5                               |                                 |                                   | n                               | 59<br>60                 | COM77<br>COM78  | COM71<br>COM72  | COM59<br>COM66  | COM59<br>COM60   | - |

| : : : :                                                                                                   | :                          |                                 |                                   |                                 | 1                               | (                                 |                                 |             | ノ                               | 2                                 |                                 |                                 |                                   | 21                              |                          |                 | :               | :               | :                |   |

| COM66         COM54         COM42         COM30           COM65         COM53         COM41         COM29 | 66<br>65                   |                                 |                                   | L                               |                                 |                                   |                                 | リー          |                                 |                                   | ſ                               |                                 |                                   | )                               | 65<br>66                 | COM83<br>COM84  | COM77<br>COM78  | COM71<br>COM72  | COM65<br>COM66   | - |

| : : : :                                                                                                   | 00                         | 21                              |                                   | 2 \                             | $\sim$                          | 2                                 |                                 | 6           | 59                              |                                   | $\mathcal{J}$                   |                                 | 0                                 |                                 | :                        | :               | :               | :               | :                | - |

| : : : : :<br>COM37 COM25 COM13 COM1                                                                       | 37                         |                                 |                                   |                                 |                                 |                                   |                                 | <u>s ((</u> |                                 |                                   | 2                               |                                 |                                   |                                 | :<br>94                  | :<br>COM112     | :<br>COM106     | :<br>COM100     | :<br>COM94       | - |

| COM36 COM24 COM12 COM0                                                                                    | 36                         | U                               |                                   |                                 |                                 | 1                                 | J                               | もし          | ノ                               |                                   |                                 |                                 |                                   |                                 | 95                       | COM113          | COM107          | COM101          | COM95            |   |

| : : :<br>COM31_COM19_COM7                                                                                 | : 31                       |                                 |                                   | -{{                             |                                 | $\mathcal{H}$                     | 6                               | ノ           |                                 |                                   |                                 |                                 |                                   |                                 | :<br>100                 |                 | :<br>COM112     | :<br>COM106     | :<br>COM100      | - |

| COM30 COM18 COM6                                                                                          | 30                         | $\left( \right)$                |                                   |                                 |                                 | <u> </u>                          |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 100                      |                 | COM113          |                 | COM101           | - |

|                                                                                                           |                            |                                 | J                                 |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | :                        |                 | :               | :               | :                | ] |

| COM25 COM13 COM1<br>COM24 COM12 COM0                                                                      | 25<br>24                   |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 106<br>107               |                 |                 |                 | COM106<br>COM107 | - |

| : :                                                                                                       | V                          |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | :                        |                 |                 | :               | :                |   |

| COM19 COM7<br>COM18 COM6                                                                                  | 19<br>18                   |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 112<br>113               |                 |                 |                 | COM112<br>COM113 | - |

|                                                                                                           | :                          |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | :                        |                 |                 | :               | :                | _ |

| COM13 COM1                                                                                                | 13                         |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 118                      |                 |                 | COM124          |                  | - |

| COM12 COM0<br>:                                                                                           | 12                         |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 119<br>:                 |                 |                 | COM125          | COM119<br>:      | - |

| COM7                                                                                                      | 7                          |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 124                      |                 |                 |                 | COM124           | - |

| COM6<br>:                                                                                                 | 6<br>:                     |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 125                      |                 |                 |                 | COM125<br>:      | i |

| COM1                                                                                                      | . 1                        |                                 |                                   |                                 |                                 |                                   |                                 |             |                                 |                                   |                                 |                                 |                                   |                                 | 130                      |                 |                 |                 | COM130           | ) |

| СОМО                                                                                                      | 0                          |                                 | _                                 |                                 |                                 |                                   |                                 |             |                                 | 40-                               |                                 |                                 | 40                                |                                 | 131                      |                 |                 |                 | COM131           | ] |

| Column<br>Address                                                                                         | MX = 0<br>MX = 1           | -                               | 0<br>131                          |                                 |                                 | 1<br>130                          |                                 |             |                                 | 130<br>1                          |                                 |                                 | 131<br>0                          |                                 |                          |                 |                 |                 |                  |   |

| SEG                                                                                                       |                            | SEGAO                           | SEGBO                             | SEGC0                           | SEGA1                           | SEGB1                             | SEGC1                           |             | SEGA130                         | SEGB130                           | SEGC130                         | SEGA131                         | SEGB131                           | SEGC131                         |                          |                 |                 |                 |                  |   |

2006/03/23

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

#### Ver 0.03

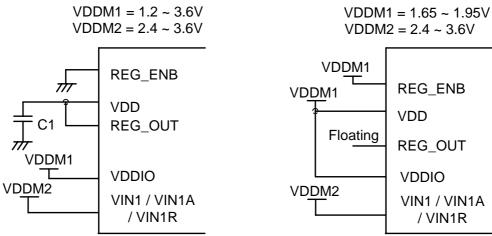

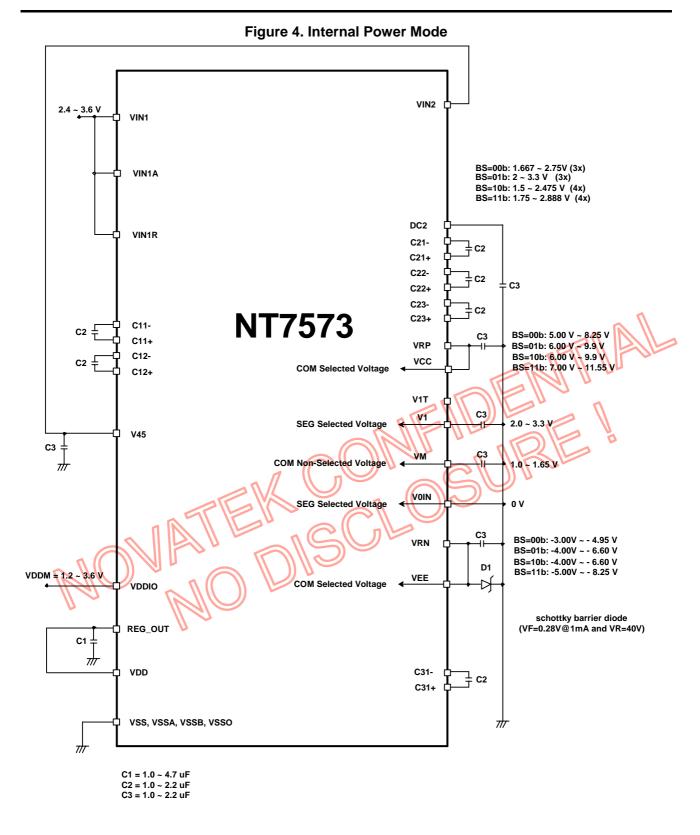

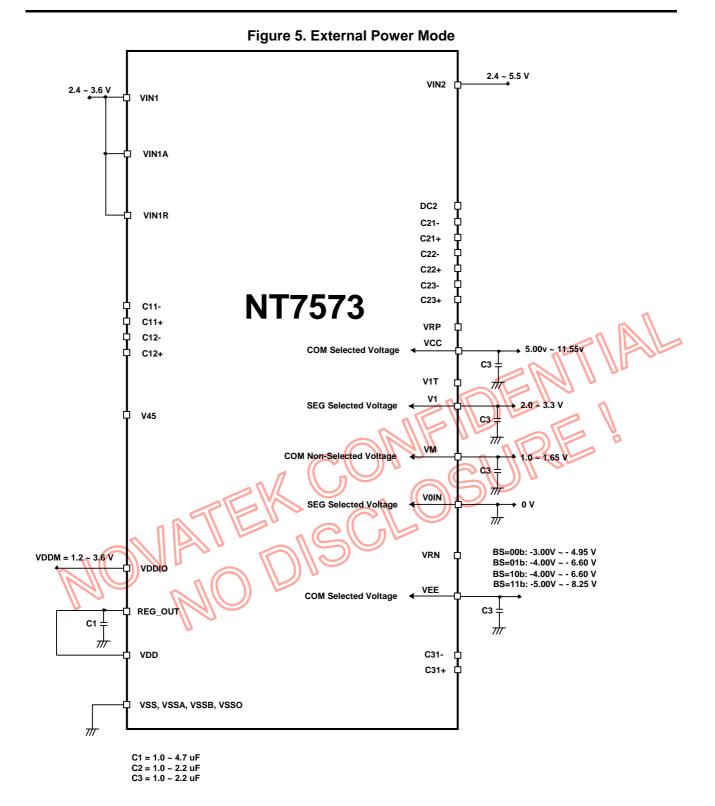

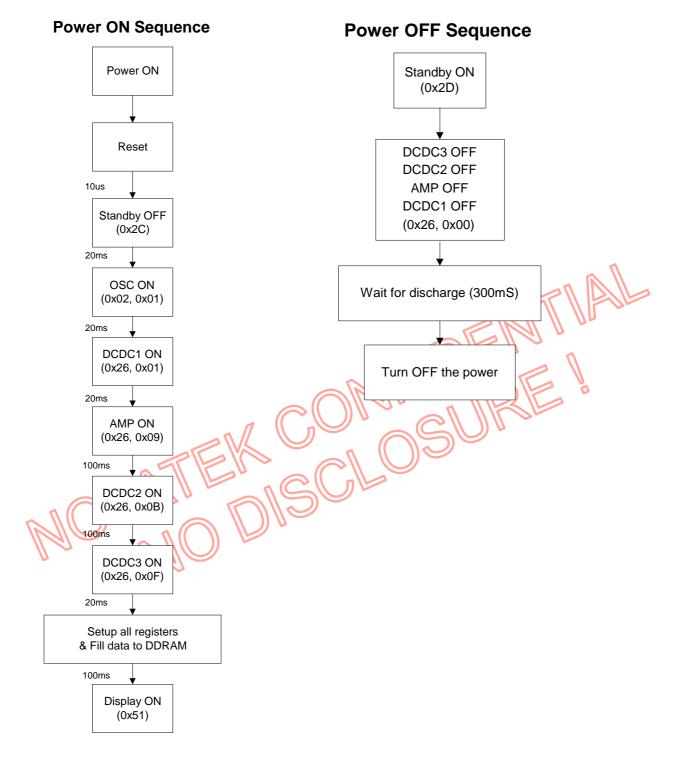

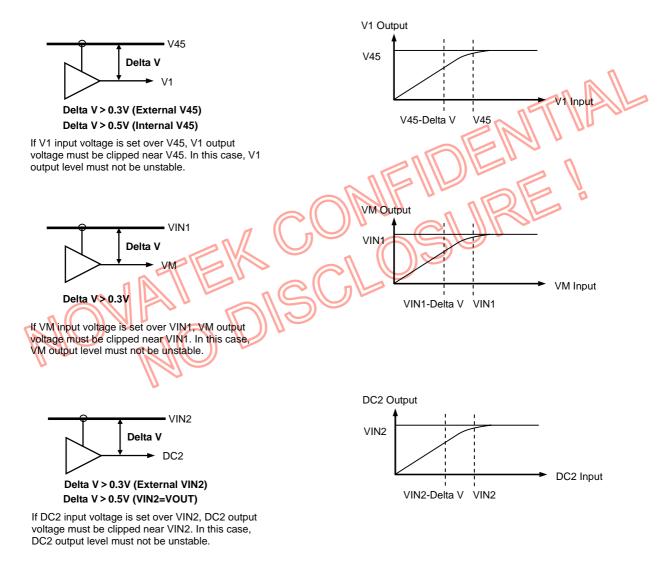

## **The Power Regulator Circuit**

The NT7573 has a regulator circuit for VDD supply. The on-chip regulator configuration is shown as follows:

#### The Voltage Regulator Circuit for V1

The NT7573 has an internal high-accuracy fixed voltage power supply with 256 steps electronic volume function for V1 OP-Amp. Through the use of V1 electronic volume function, the LCD driving voltage V1 can be controlled by Contrast Control (1) or (2) command to adjust the V1 voltage from 2.0V to 3.3V by 5.098mV per step which then makes it possible to adjust LCD brightness. The 1<sup>st</sup> booster circuit generates V45 used for power supply of internal OP-Amps.

|       | C1[7:0] or C2[7:0] | Value | V1       |

|-------|--------------------|-------|----------|

|       | 00000000           |       | 2.0      |

|       | 00000001           | 1     | 2.005098 |

| n R   | 00000010           | 2     | 2.010196 |

|       |                    |       | :        |

| ANO V | 1111101            | 253   | 3.289804 |

| la c  | 1111110            | 254   | 3.294902 |

|       | 1111111            | 255   | 3.3      |

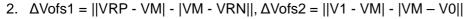

#### The Power Supply Circuit for VM, VRN and VRP

The common non-selected voltage VM is generated from V1 to keep V1 =  $2 \times VM$ . And through the DC2 OP-Amp and 2<sup>nd</sup> booster circuit. VRP can be controlled by Bias Set command and this keeps the relation VRP - VM = B x VM (bias ratio is 1/B). Finally, the 3<sup>rd</sup> booster circuit inverts the VRP that refers to VM to generate VRN. The VRN and VRP are both common selected voltages.

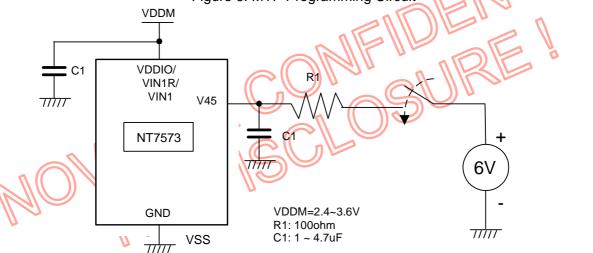

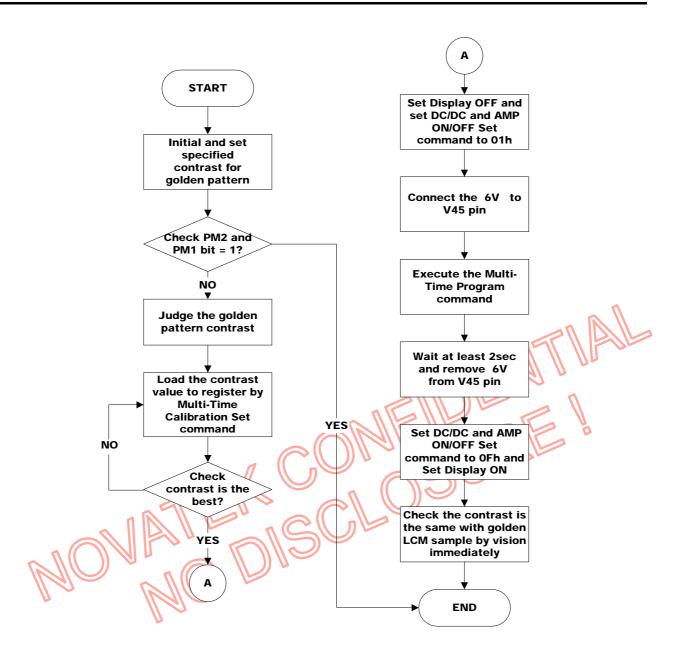

#### Multi-Time Programming (MTP) for V1 voltage

The NT7573 has a MTP function for V1 voltage calibration. Because the variation of LCD module in term of contrast level, the MTP (Multi-Time Program) can be used to achieve the best visual contrast of every LCD module by adjusting V1 voltage. The NT7573 provides only two times for V1 voltage programming. Refer to the Multi-Time Calibration Set and Multi-Time Programming Set command section.

#### 2006/03/23

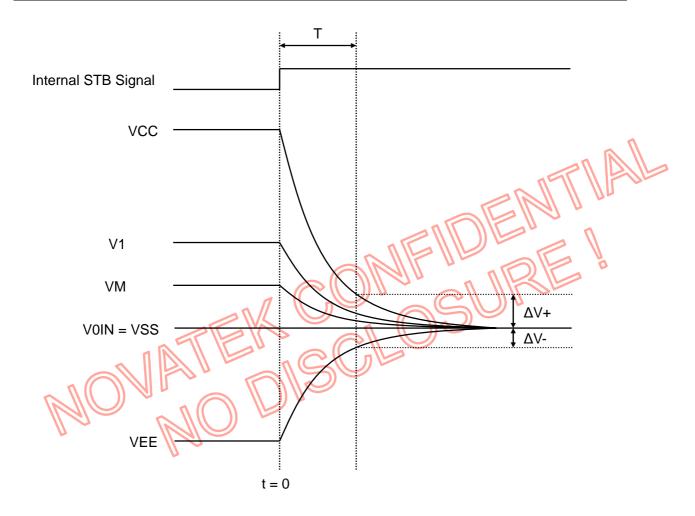

#### The Discharge Circuit

When executing the command Standby Mode ON (STB is high), the driving voltage levels will be discharged. The relation between driving voltage levels and discharge time is as follows:

| Driving Voltage  | Condition                             | Т      | ΔV+, ΔV- |

|------------------|---------------------------------------|--------|----------|

|                  | VCC = 11.55 V, V1 = 3.3V              | 100 ms | < 50 mV  |

| VCC, V1, VM, VEE | VEE = -8.25 V, VM= 1.65 V<br>at t = 0 | 300 ms | < 20 mV  |

NT7573

2006/03/23

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

Ver 0.03

## NT7573

NTIAL

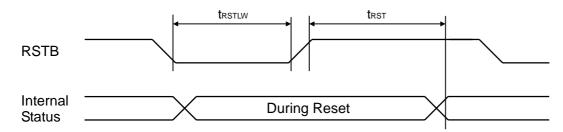

#### **Reset Circuit**

When the RSTB input falls to LOW, the NT7573 enter their default state shown as below:

- 1. Internal clock mode and internal oscillator OFF, EXT=0, OSCEN=1

- 2. Driving Output Mode

- Display duty ratio 1/132, DL[1:0]=(1,1)

- No swap for segment driver and normal common scan direction, SWP=CDR=0

- Monitor Signal Control SYNC, PM, CL and FR output VSS level, SYN=PM=CL=FR=0 SYNC output at the head of the 1<sup>st</sup> subframe, SY[1:0]=(0,0)

- 4. x1.5 time boost for  $1^{st}$  booster circuit, DC[3:0]=(0,1,0,1)

1/4 bias ratio and x(3) time  $2^{nd}$  boost for Partial mode 1 and 1/6 bias ratio and x(4) time  $2^{nd}$  boost for Normal, Partial mode 0. BS[3:0]=(0,0,1,1)

- 5. DC/DC Clock Division

- Clock division fOSC/8 for normal and partial display mode 0, DV[2:0] = (0,0,0)

- Clock division fOSC/8 (1/66duty) or fOSC/32 (1/33duty) for partial display mode 1, DV[5:3] = (0,0,0)

- 6. All booster circuits and AMP circuit OFF, AMP=BT3=BT2=BT1=0

- 7. Temperature coefficient is -0.05%/°C, TC[1:0]=(0,1)

- 8. Contrast Control C1[7:0]=C2[7:0]=(0,0,0,0,0,0,0,0)

- 9. Standby Mode ON, STB=1

- 10. Addressing Mode

- One extra dummy subgroup is none, DSG=1

- Subgroup frame inversion ON, SGF=1

- Subgroup is different phase by one pixel unit, SGP=1

- 11. Row vector increase by every subframe, INC=1

- 12. Frame inversion for AC driving, FIM=1 and NB[4:0]=(0,1,1,0,1)

- 13. Normal Frame Rate, LFS=0

- 14. Frame Frequency (1/132, 1/66, 1/33duty)=100Hz, FR[3:0]=(0,1,1,1)

- 15. Entry Mode

- 8-bit parallel data bus mode, 16B=0

- Memory data inversion OFF, MDI=0

- Column/Row address count increment, MX=MY=0

- Column address count first, Y/X=0

- Read modify write mode OFF, RMW=0

- 16. Start row address YS[7:0]=(0,0,0,0,0,0,0,0), End row address YE[7:0]=(1,0,0,0,0,0,1,1)

- 17. Start column address XS[7:0]=(0,0,0,0,0,0,0,0,0), End column address XE[7:0]=(1,0,0,0,0,0,1,1)

- 18. LCD display OFF, DOF=0

- 19. Normal display pattern, DP[1:0]=(0,0)

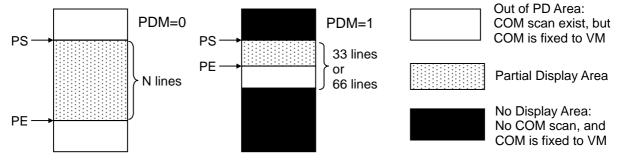

- 20. Partial Display

- Partial display mode OFF (Normal mode), PT=PDM=PDY=0

- Partial display start line PS[7:0]=(0,0,0,0,0,0,0,0)

- Partial display end line PE[7:0]=(0,0,0,0,0,0,0,0)

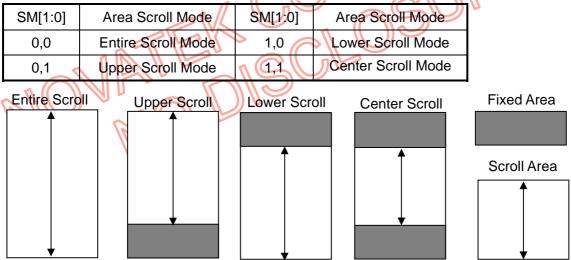

- 21. Area Scroll

- Entire display scroll mode, SM[1:0]=(0,0)

- Area scroll start line SS[7:0]=(0,0,0,0,0,0,0,0)

- Area scroll end line SE[7:0]=(1,0,0,0,0,0,1,1)

- Low fixed line number LF[7:0]=(0,0,0,0,0,0,0,0)

- Start scroll line SL[7:0]=(0,0,0,0,0,0,0,0)

- 22. Internal status register is selected for Status Read command, SR[1:0]=(0,0)

- 23. MTP calibration function is turned ON, MOF=1

#### 2006/03/23

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

#### Commands

#### 1. Non Operation

This command is non-operation.

| D/I | RDB | WRB | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex |

|-----|-----|-----|----|----|----|----|----|----|----|----|-----|

| 0   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00h |

#### 2. Oscillation Mode Set

This command is used to select the internal or external clock. When external clock is selected, the internal system clock is halted and the external system clock can be input from OSCIN pin. The internal oscillator circuit can be enabled or disabled by setting bit OSC. This command is only for internal or external system clock selection used. Do not use this command for LCD display control.

| D/I | RDB | WRB | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Hex |

|-----|-----|-----|----|----|----|----|----|----|-----|-----|-----|

| 0   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1   | 0   | 02h |

| 0   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | EXT | OSC | XX  |

The setting status is as follows:

| EXT | OSC | Status                  | OSC pins                    |

|-----|-----|-------------------------|-----------------------------|

| 0   | 0   | Internal oscillator OFF | Connect resisters between   |

| 0   | 1   | Internal oscillator ON  | OSC1, OSC2 and OSC3, OSC4   |

| 1   | *   | External clock mode     | System clock input to OSCIN |

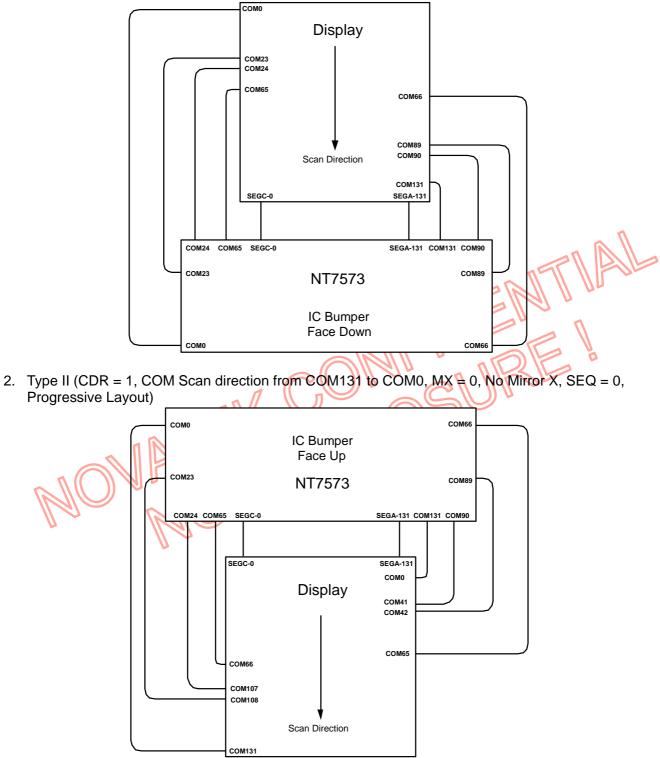

#### 3. Driver Output Mode Set

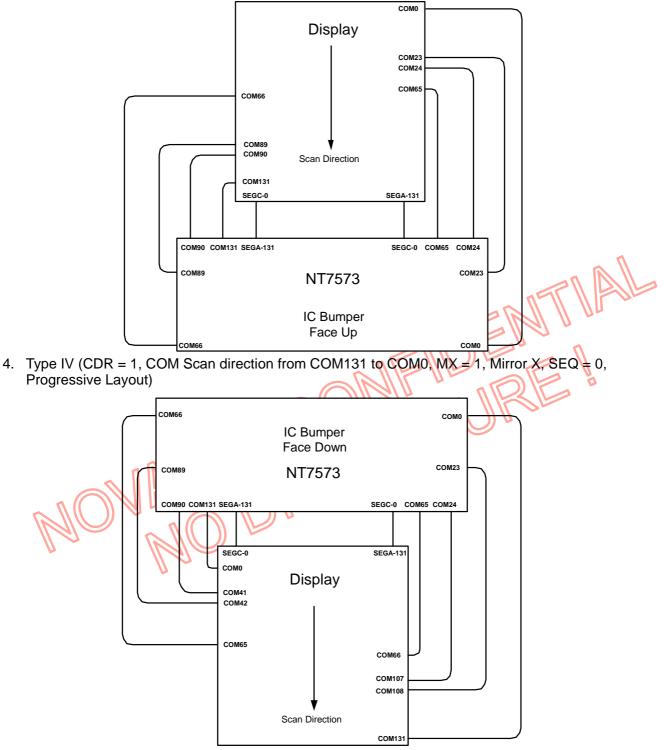

This command is for setting the scan direction of COM output allowing flexible ITO layout in LCD module assembly. The display will have an immediate effect once this command is executed, except the SWP function.

| D/I | RDB | WRB | D7  | D6 | D5  | D4  | D3 | D2 | D1  | D0  | Hex |

|-----|-----|-----|-----|----|-----|-----|----|----|-----|-----|-----|

| 0   |     | 0 < | 0   | 0  | 0   | 1   | 0  | 0  | 0   | 0   | 10h |

| 0   | 1   | 0   | SEQ | 0  | DL1 | DL0 | 0  | 0  | SWP | CDR | XX  |

The non-used common outputs are no scanning field and set to VM level.

| SEQ | DL[1:0] | Duty  | Scan Line    | Common Ou              | tput Pads              |

|-----|---------|-------|--------------|------------------------|------------------------|

|     | טבני.טן | Ratio |              | CDR = 0                | CDR = 1                |

|     | 00      | 1/96  | Line 0 ~ 95  | COM[0-47], COM[66-113] | COM[113-66], COM[47-0] |

| 0   | 01      | 1/108 | Line 0 ~ 107 | COM[0-53], COM[66-119] | COM[119-66], COM[53-0] |

| 0   | 10      | 1/120 | Line 0 ~ 119 | COM[0-59], COM[66-125] | COM[125-66], COM[59-0] |

|     | 11      | 1/132 | Line 0 ~ 131 | COM[0-65], COM[66-131] | COM[131-66], COM[65-0] |

| 050 |              | Duty  | Coop Line   | Common C                                            | Output Pads                                          |                         |                        |                                                      |                                                   |

|-----|--------------|-------|-------------|-----------------------------------------------------|------------------------------------------------------|-------------------------|------------------------|------------------------------------------------------|---------------------------------------------------|

| SEQ | DL[1:0]      | Ratio | Scan Line   | CDR = 0                                             | CDR = 1                                              |                         |                        |                                                      |                                                   |

|     |              |       | Line 0~47   | COM[0-2], COM[66-68],<br>COM[3-5],COM[69-71],       | COM[122-120],COM[56-54],<br>COM[119-117],COM[53-51], |                         |                        |                                                      |                                                   |

|     | 00           | 1/96  |             | COM[21-23], COM[87-89]                              | COM[101-99],COM[35-33]                               |                         |                        |                                                      |                                                   |

|     | 00           |       | ., 50       |                                                     | 1730                                                 | 1/30                    | Line 48~95             | COM[33-35], COM[99-101],<br>COM[36-38],COM[102-104], | COM[89-87], COM[23-21],<br>COM[86-84],COM[20-18], |

|     |              |       |             | COM[54-56],COM[120-122]                             | COM[68-66], COM[2-0]                                 |                         |                        |                                                      |                                                   |

|     |              |       | Line 0~53   | COM[0-2], COM[66-68],<br>COM[3-5],COM[69-71],       | COM[125-123],COM[59-57],<br>COM[122-120],COM[56-54], |                         |                        |                                                      |                                                   |

|     | 01           | 1/108 | 1/100       | 4/400                                               |                                                      | COM[24-26], COM[90-92], | COM[101-99],COM[35-33] |                                                      |                                                   |

| 1   | 01           | 1/108 | Line 54~107 | COM[33-35],COM[99-101],<br>COM[36-38],COM[102-104], | COM[92-90], COM[26-24],<br>COM[89-87],COM[23-21],    |                         |                        |                                                      |                                                   |

|     |              |       |             | ,<br>COM[57-59], COM[123-125]                       | COM[68-66], COM[2-0],                                |                         |                        |                                                      |                                                   |

|     |              |       | Line 0~59   | COM[0-2], COM[66-68],<br>COM[3-5],COM[69-71],       | COM[128-126],COM[62-60],<br>COM[125-124],COM[59-58], |                         |                        |                                                      |                                                   |

|     | 10           | 1/120 |             | COM[27-29], COM[93-95]                              | COM[101-99],COM[35-33]                               |                         |                        |                                                      |                                                   |

|     | ~ 1          |       | Line 60~119 | COM[33-35],COM[99-101],<br>COM[36-38],COM[102-104], | COM[95-93], COM[29-27],<br>COM[92-90],COM[26-24],    |                         |                        |                                                      |                                                   |

| n   | $\mathbb{A}$ |       |             | COM[60-62], COM[126-128]                            | ,<br>COM[68-66], COM[2-0],                           |                         |                        |                                                      |                                                   |

| Ma  | 11           | 1/132 | Line 0~131  | COM[0-2], COM[66-68],<br>COM[3-5],COM[69-71],       | COM[131-129],COM[65-63],<br>COM[128-126],COM[62-60], |                         |                        |                                                      |                                                   |

|     |              |       |             | COM[63-65], COM[129-131]                            | COM[68-66], COM[2-0]                                 |                         |                        |                                                      |                                                   |

The SEG output can be swapped as follows:

SWP=0: Normal (SEGAi is D15~D11, SEGBi is D10~D5 and SEGCi is D4~D0) SWP=1: Reverse (SEGAi is D4~D0, SEGBi is D10~D5 and SEGCi is D15~D11)

#### **Monitor Signal Control** 4.

This command is used to control the MON output signal for SYNC, PM, CL or FR.

| ſ | D/I | RDB | WRB | D7 | D6 | D5  | D4  | D3  | D2 | D1 | D0 | Hex |

|---|-----|-----|-----|----|----|-----|-----|-----|----|----|----|-----|

|   | 0   | 1   | 0   | 0  | 0  | 0   | 1   | 1   | 0  | 0  | 0  | 18h |

|   | 0   | 1   | 0   | 0  | 0  | SY1 | SY0 | SYN | РМ | CL | FR | XX  |

The output status is shown as below:

| Bit  |   | Monitor Signal Status    | Bit |   | Monitor Signal Status  |  |  |

|------|---|--------------------------|-----|---|------------------------|--|--|

| SYNC | 0 | SYNC is output VSS level | CL  | 0 | CL is output VSS level |  |  |

| SYNC | 1 | SYNC is operating        | ΟL  | 1 | CL is operating        |  |  |

| РМ   | 0 | PM is output VSS level   | FR  | 0 | FR is output VSS level |  |  |

| FIVI | 1 | PM is operating          | ГК  | 1 | FR is operating        |  |  |

When SYN=1, the output timing of SYNC is set by SY[1:0] as follows.

| SY[1:0] | SYNC signal output timing        |

|---------|----------------------------------|

| 00      | Head of 1 <sup>st</sup> subframe |

| 01      | Head of 2 <sup>nd</sup> subframe |

| 10      | Head of 3 <sup>rd</sup> subframe |

| 11      | Head of 4 <sup>th</sup> subframe |

|         |                                  |

FR: Polarity indicator signal.

CL: Shift clock signal

PM: Field delimiter signal.

SYNC: Frame delimiter signal.

Note: The priority of the monitor signal is: FR > CL > PM > SYNC.

#### **DC/DC Select** 5.

To select the boost times of the 1<sup>st</sup> booster circuit in normal display mode, partial display mode 0 and partial display mode 1.

| D/I | RDB | WRB | D7 | D6 | D5  | D4  | <b>D</b> 3 | D2 | D1  | D0  | Hex |

|-----|-----|-----|----|----|-----|-----|------------|----|-----|-----|-----|

| 0   | 3   | 0   | 0  | 0  | F   | 0   | 0          | 0  | 0   | 0   | 20h |

| 0   | 1   | 0   | 8  |    | DC3 | DC2 | 0          | 0  | DC1 | DC0 | XX  |

The boost times of 1<sup>st</sup> internal DC/DC converter circuit are set as follows:

| In F    | Partial Display Mode 1                 | In Normal, Partial Display Mode 0 |                                        |  |  |  |  |

|---------|----------------------------------------|-----------------------------------|----------------------------------------|--|--|--|--|

| DC[3:2] | 1 <sup>st</sup> Booster Circuit Set Up | DC[1:0]                           | 1 <sup>st</sup> Booster Circuit Set Up |  |  |  |  |

| 00      | x 1.0                                  | 00                                | x 1.0                                  |  |  |  |  |

| 01      | x 1.5                                  | 01                                | x 1.5                                  |  |  |  |  |

| 10      | x 2.0                                  | 10                                | x 2.0                                  |  |  |  |  |

| 11      | x 2.0                                  | 11                                | x 2.0                                  |  |  |  |  |

2006/03/23

#### 6. Bias Set

This command is the LCD driving bias ratio selection in normal display mode, partial display mode 0 and partial display mode 1.

| ľ | D/I | RDB | WRB | D7 | D6 | D5  | D4  | D3 | D2 | D1  | D0  | Hex |

|---|-----|-----|-----|----|----|-----|-----|----|----|-----|-----|-----|

|   | 0   | 1   | 0   | 0  | 0  | 1   | 0   | 0  | 0  | 1   | 0   | 22h |

| I | 0   | 1   | 0   | 0  | 0  | BS3 | BS2 | 0  | 0  | BS1 | BS0 | XX  |

The boost times of the 2<sup>nd</sup> booster circuit and output voltage of DC2 are decided when the bias ratio is set.

|         | In Par | tial Display Mode 1                    | In Normal, Partial Display Mode 0 |      |                                        |  |  |  |

|---------|--------|----------------------------------------|-----------------------------------|------|----------------------------------------|--|--|--|

| BS[3:2] | Bias   | 2 <sup>nd</sup> Booster Circuit Set Up | BS[1:0]                           | Bias | 2 <sup>nd</sup> Booster Circuit Set Up |  |  |  |

| 00      | 1/4    | x (3.0)                                | 00                                | 1/4  | x (3.0)                                |  |  |  |

| 01      | 1/5    | x (3.0)                                | 01                                | 1/5  | x (3.0)                                |  |  |  |

| 10      | 1/5    | x (4.0)                                | 10                                | 1/5  | x (4.0)                                |  |  |  |

| 11      | 1/6    | x (4.0)                                | 11                                | 1/6  | x (4.0)                                |  |  |  |

#### 7. DC/DC Clock Division Set

To set the internal booster clock frequency to normal display mode, partial display mode 0 and partial display mode 1.

| D/I | RDB | WRB | D7 | D6  | D5  | D4  | D3 | D2  | D1  | DO  | Hex |    |

|-----|-----|-----|----|-----|-----|-----|----|-----|-----|-----|-----|----|

| 0   | 1   | 0   | 0  | 0   | 1   | 0   | 0  | ))\ | 0   | 0   | 24h | SF |

| 0   | 1   | 0   | 0  | DV5 | DV4 | DV3 | 0  | DV2 | DV1 | D∀0 | XX  |    |

The booster clock frequency is set as follows:

| In Pa   | artial Display Mode 1   |         | nal, Partial Display Mode 0   |

|---------|-------------------------|---------|-------------------------------|

| DV[5:3] | Booster Clock Frequency | DV[2:0] | Booster Clock Frequency       |

| DV[5.5] | 1/66, 1/33duty          |         | 1/132, 1/120, 1/108, 1/96duty |

| 000     | fOSC/8                  | 000     | fOSC/8                        |

| 001     | fOSC/16                 | 001     | fOSC/16                       |

| 010     | fOSC/32                 | 010     | fOSC/32                       |

| 011     | fOSC/64                 | 011     | fOSC/64                       |

| 100     | fOSC                    | 100     | fOSC                          |

| 101     | fOSC/2                  | 101     | fOSC/2                        |

| 110     | fOSC/4                  | 110     | fOSC/4                        |

| 111     | fOSC/8                  | 111     | fOSC/8                        |

Note: 1.  $fOSC = (Duty/3 + Dummy) \times 4 \times 8 \times frame frequency.$

2. The suitable frequency of the boost clock is in a range from 5kHz to 16kHz.

#### 8. DC/DC and AMP ON/OFF Set

This command is to turn ON or OFF the internal OP-AMP and booster circuits.

|   | D/I | RDB | WRB | D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0  | Hex |

|---|-----|-----|-----|----|----|----|----|-----|-----|-----|-----|-----|

|   | 0   | 1   | 0   | 0  | 0  | 1  | 0  | 0   | 1   | 1   | 0   | 26h |

| I | 0   | 1   | 0   | 0  | 0  | 0  | 0  | AMP | BT3 | BT2 | BT1 | XX  |

The setting status is shown as below:

| В     | sit | Internal Power Circuit Status       | Bit |   | Internal Power Circuit Status       |  |  |  |

|-------|-----|-------------------------------------|-----|---|-------------------------------------|--|--|--|

| AMP - | 0   | Internal OP-AMP OFF                 | BT2 | 0 | 2 <sup>nd</sup> booster circuit OFF |  |  |  |

|       | 1   | Internal OP-AMP ON                  | DIZ | 1 | 2 <sup>nd</sup> booster circuit ON  |  |  |  |

| BT1   | 0   | 1 <sup>st</sup> booster circuit OFF | BT3 | 0 | 3 <sup>rd</sup> booster circuit OFF |  |  |  |

| ЫІ    | 1   | 1 <sup>st</sup> booster circuit ON  | ыз  | 1 | 3 <sup>rd</sup> booster circuit ON  |  |  |  |

#### 9. Temperature Compensation Set

This command can select the average temperature compensation coefficients.

| D/I | RDB | WRB | D7 | D6 | D5 | D4 | D3 | D2 | D1   | D0   | Hex |

|-----|-----|-----|----|----|----|----|----|----|------|------|-----|

| 0   | 1   | 0   | 0  | 0  | 1  | 0  | 1  | 0  | 0    | 0    | 28h |

| 0   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | TCS1 | TCS0 | XX  |

The four sets of temperature compensation coefficients can be selected as follows:

| TCS[1:0] | Temperature Compensation Coefficient (at 25°C) |

|----------|------------------------------------------------|

| 00       | -0.00%/°C                                      |

| 01       | -0.05%/°C                                      |

| 10       | -0.10%/C                                       |

|          | -0.15%/°C                                      |

If external temperature compensation is needed, two resistors and one thermistor are connected as in the following circuit:

2006/03/23

With respect to the information represented in this document, Novatek makes no warranty, expressed or implied, including the warranties of merchantability, fitness for a particular purpose, non-infringement, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any such information.

Ver 0.03

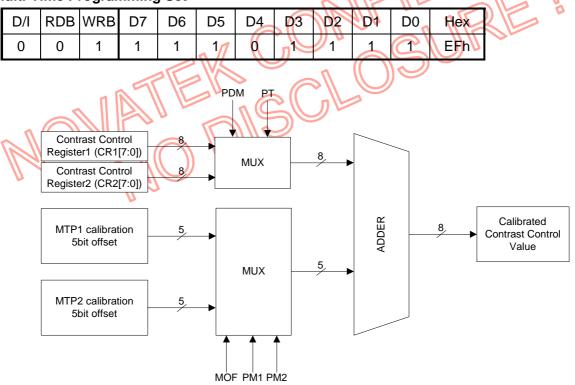

#### 10. Contrast Control (1) and Contrast Control (2)

The command Contrast Control (1) is to set the contrast value C1[7:0] in normal display mode and partial display mode 0.

| D/I | RDB | WRB | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Hex |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 2Ah |

| 0   | 1   | 0   | C17 | C16 | C15 | C14 | C13 | C12 | C11 | C10 | XX  |

The command Contrast Control (2) is to set the contrast value C2[7:0] in partial display mode 1.

| D/I | RDB | WRB | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Hex |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 1   | 1   | 2Bh |

| 0   | 1   | 0   | C27 | C26 | C25 | C24 | C23 | C22 | C21 | C20 | XX  |

Both commands adjust V1 voltage from 2.0V to 3.3V, so the contrast resolution is 5.098mV in one step value.

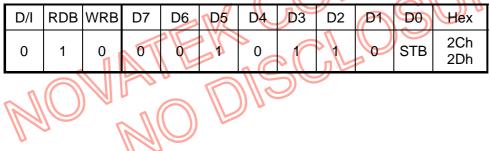

#### 11. Standby Mode ON/OFF Set

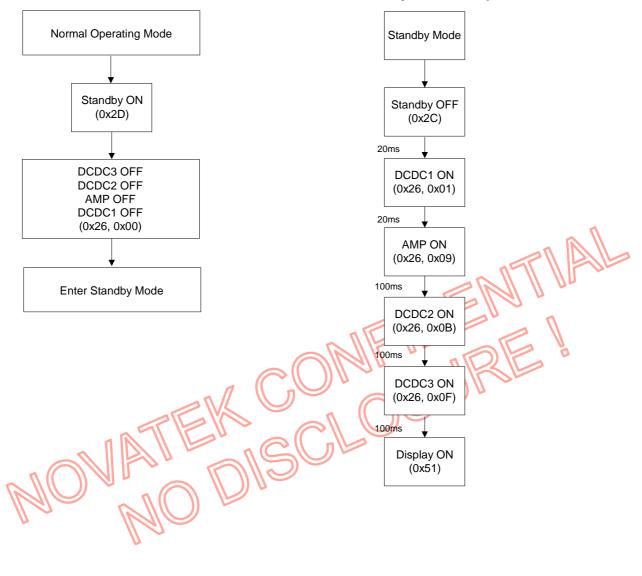

This command is used to set the IC to enter or exit the standby mode. When STB is high, the IC enters the standby mode to save the power consumption as in the following status:

- (1) All LCD driver outputs (common and segment): VSS level

- (2) Internal LCD driving power outputs (VRP, V1, VM and VRN); VSS level

- (3) Internal booster circuits (1<sup>st</sup>, 2<sup>nd</sup> and 3<sup>rd</sup> booster): OFF

- (4) Oscillator circuit: OFF

(5) The content of DDRAM is not cleared and the data can be written through the MPU interface.

Set standby mode off and display on commands for returning to the normal operation status.

#### 12. Addressing Mode Set

This command is for setting the duty adjusts DSG, subgroup frame inversion mode SGF and subgroup phase mode SGP.

| D/I | RDB | WRB | D7 | D6 | D5 | D4  | D3  | D2 | D1  | D0 | Hex |

|-----|-----|-----|----|----|----|-----|-----|----|-----|----|-----|

| 0   | 1   | 0   | 0  | 0  | 1  | 1   | 0   | 0  | 0   | 0  | 30h |

| 0   | 1   | 0   | 0  | 0  | 0  | DSG | SGF | 0  | SGP | 0  | XX  |

The setting function is shown as below:

| В     | Bit | Subgroup Function Status       | В   | it | Subgroup Function Status        |

|-------|-----|--------------------------------|-----|----|---------------------------------|

| DSG - | 0   | Dummy subgroup is one subgroup | SGP | 0  | Same phase in all pixel         |

| 036   | 1   | Dummy subgroup is none         |     | 1  | Different phase by 1 pixel unit |

| SGF   | 0   | Subgroup frame inversion OFF   |     |    |                                 |

| 30    | 1   | Subgroup frame inversion ON    |     |    | 2                               |

#### 13. Row Vector Mode Set

| Row \  | /ector | Mode     | Set      |        |       |         |       |       |     |    |     |          |

|--------|--------|----------|----------|--------|-------|---------|-------|-------|-----|----|-----|----------|

| This c | omma   | nd is to | o set tl | he row | vecto | or upda | te me | thod. |     |    | ~   | NGT VENE |

| D/I    | RDB    | WRB      | D7       | D6     | D5    | D4      | D3    | D2    | D1  | D0 | Hex |          |

| 0      | 1      | 0        | 0        | 0      | 1     | 1       | 0     | 0     | 1   | 0  | 32h |          |

| 0      | 1      | 0        | 0        | 0      | 0     | 0       | 0     | 0     | INC | 0  | XX  |          |

The row vector sequence is  $R1 \rightarrow R2 \rightarrow R3 \rightarrow R4 \rightarrow R1 \rightarrow ...$  and updated as follows by setting INC.

| В   | Bit | Row Vector L   | pdate |

|-----|-----|----------------|-------|

| INC | 0   | Every subgroup |       |

|     | 1   | Every subframe | nCl   |

#### 14. N-block Inversion Set

This command is for setting the N-block inversion for liquid crystal polarity alternation.

| D/I | RDB | WRB | D7  | D6 | D5 | D4  | D3  | D2  | D1  | D0  | Hex |

|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 0   | 0   | 0  | 1  | 1   | 0   | 1   | 0   | 0   | 34h |

| 0   | 1   | 0   | FIM | 0  | 0  | NB4 | NB3 | NB2 | NB1 | NB0 | XX  |

All the driver outputs will have polarity inversion as in the following setting: