PRELIMINARY DOT MATRIX LCD 80-OUT SEGMENT DRIVER

## GENERAL DESCRIPTION

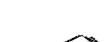

The NJU6415 is a serial input, 80-out segment driver for dot matrix LCDs, especially useful as extension driver for LCD controller drivers like NJU6426.

It consists of bidirectional shift register, 80-bit latch, and 80-out high voltage LCD drivers.

The bidirectional shift register performs the efficient extension driver allocation according to the number of characters and easy wiring with the LCD panel.

As the 80-driver has 4 level voltage input to drive the LCD, adjustable driving voltage according to the LCD panel can be supplied from the external power source.

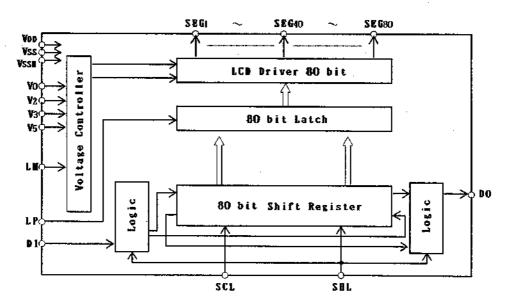

PACKAGE OUTLINE

NJU6415F

#### FEATURES

- 80 Segment Drivers

- 🔴 80-bit Shift Register

- (Bidirectional Shift Register)

- Two of Shift Direction Select Terminal

- Fast Data Transmission (Shift Clock 3.3 MHz min.)

- External Power Supply for ECD Driving Voltage

- LCD Driving Voltage --- VDD 3.0V ~ VDD 13.5V

- Operating Voltage --- 5.0 V ± 10 %

- Package Outline --- QFP100/Chip

- C-MOS Technology

#### BLOCK DIAGRAM

New Japan Radio Co.,Ltd.

# NJU6415

#### PIN CONFIGURATION

JRC

# TERMINAL DESCRIPTION

| NO.               | SYMBOL                    | FUNCTION                                                                                                                                                                                                                                                                                                    |

|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~30<br>51~100    | SEG30~SEG1<br>SEG80~SEG31 | LCD segment driving terminal.<br>Each terminal corresponds to each bit of shift register                                                                                                                                                                                                                    |

| 41                | DI                        | Data input terminal. The DI terminal is fixed the input terminal regardless the shift direction.<br>Display data is input synchronized with the clock signal.                                                                                                                                               |

| 42                | DO                        | Data output terminal. The DO terminal is fixed the output terminal regardless the shift direction.<br>The data is output synchronized with the clock signal.                                                                                                                                                |

| 40                | SCL                       | Shift register clock pulse input terminal.<br>The data is shifted in the shift register by the falling edge of<br>the clock pulse. A data setup time and hold time are required<br>between data input and SCL. Clock pulse rising time and falling<br>time should be set less than 50ms (MAX) respectively. |

| 39                | SHL                       | Shift direction select terminal.<br>"H": Shift direction is from 80th bit to 1st bit.<br>"L": Shift direction is from 1st bit to 80th bit.<br>The DI and DO terminals are fixed input and output terminal re-<br>spectively regardless this terminal input level.                                           |

| 37                | LP                        | Latch pulse input terminal. The data in the shift register is<br>latched to the Latch by this signal.<br>"H": Data writing, "L": Data latch                                                                                                                                                                 |

| 44                | LM                        | Alternate signal input for LCD driving.                                                                                                                                                                                                                                                                     |

| 46<br>36          | V <sub>DD</sub><br>Vs9    | Power supply terminal (connect to the controller's V <sub>DD</sub> terminal)<br>Power supply terminal (connect to the controller's V <sub>SS</sub> terminal)                                                                                                                                                |

| 33,35,34,32<br>31 | V0,V2,V3,V5<br>VssH       | LCD driving power source terminals.<br>Vpp≧Vo≧V2≧V3≧V5≧VssH                                                                                                                                                                                                                                                 |

| 38,43,45<br>47~50 | NC                        | Non connection.(Normally open)                                                                                                                                                                                                                                                                              |

-New Japan Radio Co.,Ltd.

5

#### FUNCTIONAL DESCRIPTION

## (1) Shift register control

The 80-bit shift register is a bidirectional register. The shift direction of 80-bit bidirectional shift register is shown below:

| Control Terminal | Input | Shift Direction |  |  |

|------------------|-------|-----------------|--|--|

|                  | "H"   | 80 → 1          |  |  |

| SHL              | "L"   | . 1 → 80        |  |  |

(Note) D) and D0 terminals are fixed input and output terminal respectively regardless the SHL input level.

#### (2) LCD driver output truth table

| Input Data | Selection/Non-selection | LM | Driver Output (SEG1 to SEG80) |

|------------|-------------------------|----|-------------------------------|

| "H"        | Selection               | H  | ٧s                            |

|            | Selection               | L  | V0 (VDD)                      |

| "L"        |                         | н  | ¥٤                            |

|            | Non-selection           | L  | V2                            |

#### ABSOLUTE MAXIMUM RATINGS

## (Ta=25°C)

| PARAMETER                  | SYMBOL           | RATINGS                        | UNIT |

|----------------------------|------------------|--------------------------------|------|

| Supply Voltage (1)         | Vod              | - 0.3 ~ + 7.0                  | ۷    |

| Supply Voltage (2) Note 1) | V0,V2,V3,V5,V98H | $V_{DD}$ -13.5 ~ $V_{DD}$ +0.3 | ٧    |

| Input Voltage              | ¥۱»              | - 0.3 ~ V <sub>DD</sub> +0.3   | ٧    |

| Operating Temperature      | Topr             | - 30 ~ + 80                    | ĉ    |

| Storage Temperature        | Tstg             | - 55 ~ + 150                   | Ċ    |

-New Japan Radio Co.,Ltd.-

Note 1) The relation :  $V_{DD} \ge V_0 \ge V_2 \ge V_3 \ge V_5 \ge V_{SSH}$  must be maintained.

#### ELECTRICAL CHARACTERISTICS

JRC

• DC Characteristics

(  $V_{\text{DD}}\text{=}5V{\pm}10\%$  , Ta=-20  $\sim$  +75°C )

| PARAMETER                                | SYMBOL | CONDITIONS                                                                 | MIN                  | TYP | MAX      | UNIT |

|------------------------------------------|--------|----------------------------------------------------------------------------|----------------------|-----|----------|------|

|                                          | Vів    |                                                                            | 0.8Vpd               |     | Vpo      | v    |

| Input Voltage Notel)                     | Ύιι    | - <u> </u>                                                                 |                      |     | 0.2Vpp   |      |

| 1                                        | เห     | $V_{1H} = V_{DD}$                                                          |                      |     | 1        | μA   |

| Input Current Notel)                     | lı1    | $V_{TL} = 0V$                                                              | - 1                  |     |          | μη   |

|                                          | Vон    | to = -40µA                                                                 | 4.2                  |     |          | ۷    |

| Output Voltage Note2)                    | Vol    | l₀ = 0.4anA                                                                |                      |     | 0.4      |      |

| Driver On-resistance<br>Note3)           | Ron    | 1d = 0.05mA                                                                |                      |     | 5        | kΩ   |

| Operating Current<br>(Logic Part)        | lsso   | LM,LP=130µs cycle,<br>SCL=1.5MHz. Every one bit<br>Inverted Data. No Load. |                      | 1.1 | 1.5      | mA   |

| Operating Current<br>( LCD Driver Part ) | Івяно  | LM.LP=130µs cycle,<br>SCL=1.5MHz. Every one bit<br>Inverted Data. No Load. |                      | 70  | 100      | μA   |

| LCD Driving Voltage                      | VLCD   | Vesa Terminal, Voo=5V                                                      | V <sub>DD</sub> -3.0 |     | Vpp-13.5 | V    |

Note 1) Apply to LM, LP, SCL, SHL and DI terminals. Note 2) Apply to DO terminal.

Note 3) Apply to SEG<sub>1</sub>  $\sim$  SEG<sub>80</sub> terminals.

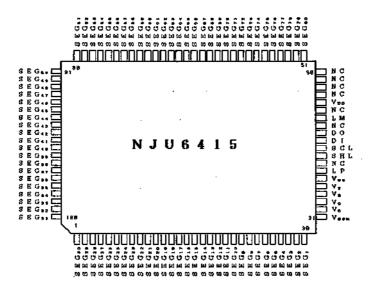

• AC Characteristics

| PARAMETER                   | SYMBOL   | CONDITIONS  | MIN | TYP | MAX | UNIT |

|-----------------------------|----------|-------------|-----|-----|-----|------|

| Propagation Delay Time      | Трън(нь) |             |     | 1   | 250 | ns   |

| Maximum Operating Frequency | fsci     | Duty = 50 % | 3.3 |     |     | MHz  |

| SCL Pulse Width             | Tws      |             | 125 |     |     | ns   |

| LP Pulse Width              | Twi      |             | 125 |     |     | ns   |

| Set up Time                 | Tset     |             | 50  | -   |     | ns   |

| $SCL \rightarrow LP$ Time   | Tsi      |             | 250 |     |     | n\$  |

| $LP \rightarrow SCL$ Time   | Tus      |             | 0   |     |     | ns   |

| Data Hold Time              | Тного    |             | 50  |     |     | ns   |

| SCL Rise, Fall Time         | Trs, Trs |             |     |     | 50  | ns   |

| LP Rise, Fall Time          | TRL, TFL |             |     |     | 1   | μs   |

.

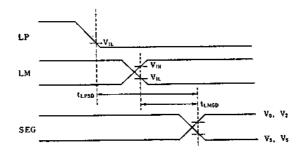

## AC CHARACTERISTICS TIMING CHART

All and an and a second and a

# -New Japan Radio Co., Ltd.:

SEGMENT SIGNAL OUTPUT TIMING

| PARAMETER                  | SYMBOL | CONDITIONS             | MIN | TYP | MAX | UNIT |

|----------------------------|--------|------------------------|-----|-----|-----|------|

| LP - SEG Output Delay Time | TLPSD  | C <sub>L</sub> = 100pF |     |     | 4.5 |      |

| LM - SEG Output Delay Time | TLMSD  | C <sub>L</sub> = 100pF |     |     | 4.5 | μs   |

5

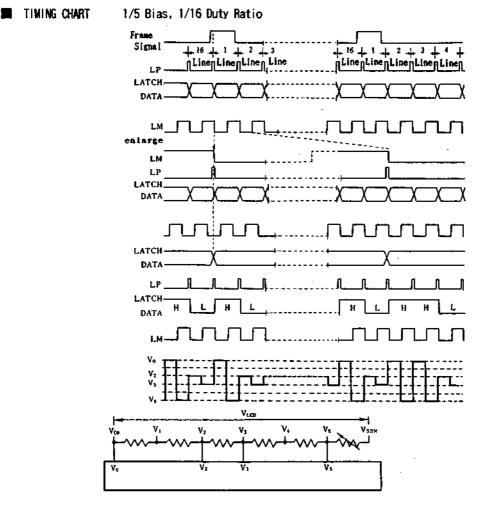

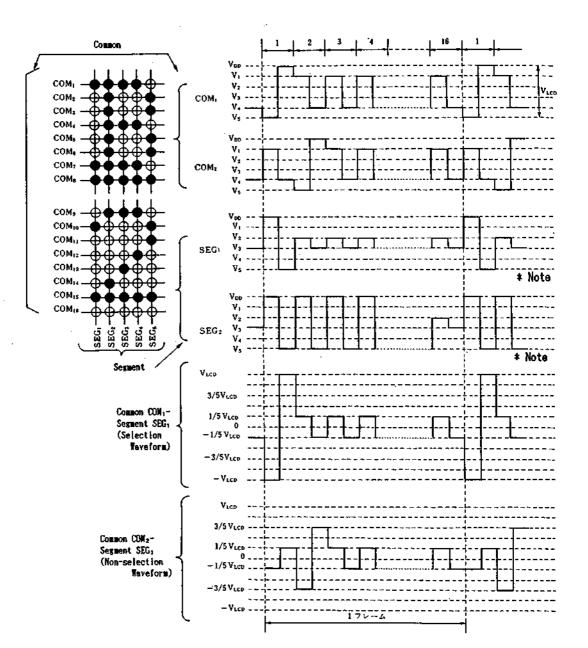

## LCD DRIVING WAVEFORM EXAMPLE

1/5 Bias, 1/16 Duty Ratio

NJU6415

\* Note : In case of  $V_0$  terminal connected to the  $V_{DD}$ .

-New Japan Radio Co.,Ltd.

5

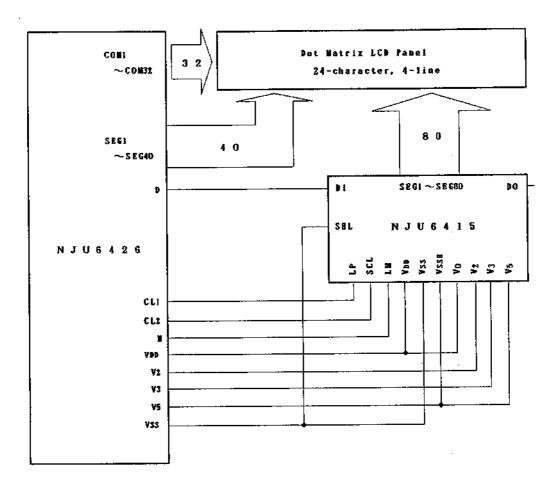

# APPLICATION CIRCUIT

24-character 4-line Display Example (NJU6426 + NJU6415)

**MEMO**

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.