145 Royal Crest Court Unit 42, Markham, ON, Canada L3R 9Z4 Tel: 905-477-1166, Fax: 905-477-1782 http://www.orientdisplay.com

### SPECIFICATION FOR LCM MODULE

MODULE NO.: AMG240128PR-G-W6WFDW DOC.REVISION: 01

**Customer Approval:**

|                              | SIGNATURE | DATE |

|------------------------------|-----------|------|

| PREPARED BY<br>(RD ENGINEER) |           |      |

| PREPARED BY<br>(QA ENGINEER) |           |      |

| CHECKED BY                   |           |      |

| APPROVED BY                  |           |      |

#### **DOCUMENT REVISION HISTORY**

| Version  | DATE                       | DESCRIPTION                                           | CHANGED<br>BY |

|----------|----------------------------|-------------------------------------------------------|---------------|

| 00<br>01 | Nov-04-2009<br>Nov-20-2009 | First issue Update backlight characteristics(Page 13) | Chen<br>Chen  |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

|          |                            |                                                       |               |

#### **CONTENTS**

| 1. Functions & Features                                     | 2     |

|-------------------------------------------------------------|-------|

| 2. Mechanical specifications                                | 2     |

| 3. Block diagram                                            | 2     |

| 4. Dimensional outline                                      | 3     |

| 5. LCD driving voltage generator and bias reference circuit | 4     |

| 6. Pin description                                          | 5-6   |

| 7. Maximum absolute limit                                   | 6     |

| 8. Electrical characteristics                               | 7     |

| 9. Timing characteristics                                   | 8-11  |

| 10. Control and display command                             | 12    |

| 11. Electro-Optical characteristics                         | 13    |

| 12. Backlight characteristics                               | 13    |

| 13. Precaution for using LCD/LCM                            | 14-15 |

| 14. LCM test criteria                                       | 16-25 |

#### 1. FUNCTIONS & FEATURES

1.1. Format : 240\*128 Dots

1.2. LCD mode : FSTN /Positive Mode /Transflective

1.3. Viewing direction : 6 o'clock

1.4. Driving scheme : 1/128 Duty cycle, 1/12 Bias

1.5. Power supply voltage  $(V_{DD})$  : 3.3V

1.6. LCD driving voltage (VLCD) : 14.5V(Reference voltage)

1.7. Operation temp:  $-20\sim70^{\circ}$ C1.8. Storage temp:  $-30\sim80^{\circ}$ C1.9. Back light: Edge White

1.10. RoHS compliant.

#### 2. MECHANICAL SPECIFICATIONS

2.1. Module size : 101.30mm(L)\*76.3mm+30.0mm(FPC length)(W)\*4.50mm(H)

2.2. Viewing area

: 92.0mm(L)\*60.50mm(W)

2.3. Dot pitch

: 0.36mm(L)\*0.40mm(W)

2.4. Dot size

: 0.33mm(L)\*0.37mm(W)

2.5. Weight : Approx.

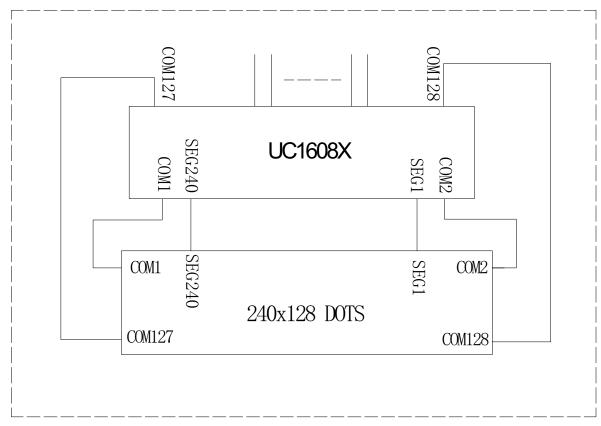

#### 3. BLOCK DIAGRAM

Figure 1.Block diagram

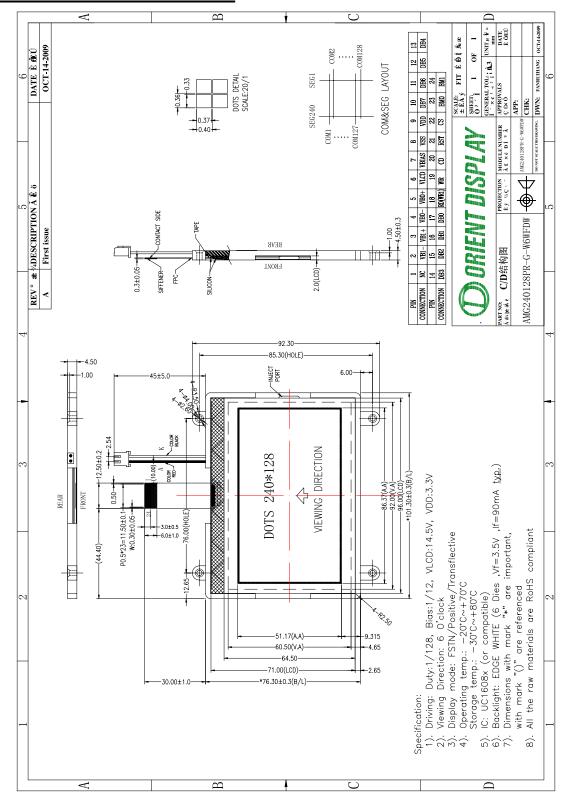

#### 4. DIMENSIONAL OUTLINE

Figure 2. Dimensional outline

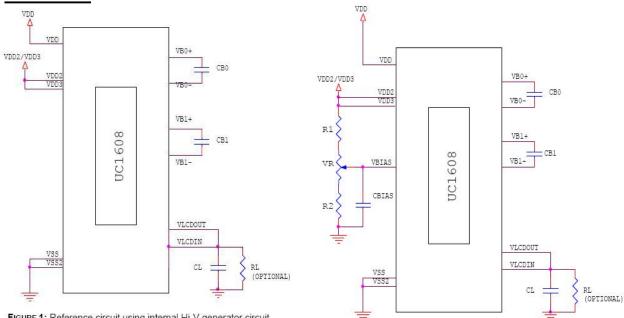

#### 5. LCD DRIVING VOLTAGE GENERATOR AND BIAS REFERENCE CIRCUIT

FIGURE 1: Reference circuit using internal Hi-V generator circuit

Figure 2: Reference circuit using external Bias source

NOTE: Recommended component values.

CB: 150~250xLCD load capacitance or 4.7 uF (2V). whichever is higher.

CL: 50Nf~0.1uF(25V)is appropriate for most applications..

Rl:  $10M\Omega$  Acts as a draining circuit when the power is abnormally shut down.

VR:  $1M\Omega$ .

R1,R2: See instructions below.

CBIAS: 10nF~0.1Nf.

- The above component values are for reference only. Please optimize the values for individual requirements of each specific application.

- To ensure consistency of LCM contrast. VLCD fine tuning is highly recommended. Since the value of R1/R2 depends strongly on the GN,PM,BR settings, and vary slightly depends on the value of VDD2, each LCM design will need to be optimized individually.

The following is the recommended procedures for selecting R1, R2 and VR values.

- Step 1: adjust LCM for best contrast which CBIAS. But without R1, R2, VR.

- Step 2: measure VBIAS voltage.

- Step 3: select VR and R2 (recommend to start with VR=1M $\Omega$ , R2=200K)

- Step 4: calculate R1 by:  $R1 = R2 \times (VDD2/VBIAS-1)$

- Step 5: install R1, R2, VR. The "neutral position" of VR is at VBIAS/VDD2.

- Step 6: Test the fine tuning range by adjusting VR over the full range.

- Step7: if adjustment fang is too narrow, reduce R2,... and vise versa.

- Step 8: repeat from Sept 4.

#### **6. PIN DESCRIPTION**

|        | 1 DESCRII              | TTOIT          |                                                                                                                                                                          |              |            |           |               |                 |          |  |

|--------|------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-----------|---------------|-----------------|----------|--|

| No.    | Symbol                 |                |                                                                                                                                                                          |              | Function   | 1         |               |                 |          |  |

| 1      | NC                     | No connecti    | No connection                                                                                                                                                            |              |            |           |               |                 |          |  |

| 2~5    | VB1-,VB1+<br>VB0-,VB0+ |                | LCD Bias voltage. These are the voltage source to provide SEG driving currents. These voltages are generated internally. Connect capacitors of CBX between VBX- and VBX+ |              |            |           |               |                 |          |  |

| 6      | VLCD                   | Main LCD p     | ower supp                                                                                                                                                                | ly, capacito | or CL sho  | uld be co | onnected betw | ween VLCD and   | VSS.     |  |

| 7      | VBIAS                  | This is the re | eference vo                                                                                                                                                              | oltage to ge | nerate the | actual S  | SEG driving v | oltage.         |          |  |

| 8      | VSS                    | Power GND      |                                                                                                                                                                          |              |            |           |               |                 |          |  |

| 9      | VDD                    | Power Supp     | ly (+3.3V).                                                                                                                                                              |              |            |           |               |                 |          |  |

|        |                        | Bi-direction:  | i-directional bus for both serial and parallel host interfaces.                                                                                                          |              |            |           |               |                 |          |  |

|        | ļ                      |                | BM=                                                                                                                                                                      |              | BM=02      |           | BM=01         | BM=00           |          |  |

|        |                        | D0             | DIVI-                                                                                                                                                                    |              |            |           |               |                 |          |  |

|        |                        | D0             |                                                                                                                                                                          | D0           | D0/        |           | SCK           | SCK             |          |  |

|        |                        | D1             |                                                                                                                                                                          | D1           | D1/        |           | -             | -               |          |  |

|        |                        | D2             |                                                                                                                                                                          | D2           | D2/        | 'D6       | -             | -               |          |  |

| 10~17  | DB7~DB0                | D3             |                                                                                                                                                                          | D3           | D3/        | D7        | SDA           | SDA             |          |  |

| 10,417 | טם אין פט              | D4             |                                                                                                                                                                          | D4           |            |           |               | _               |          |  |

|        | <br> -                 | D5             |                                                                                                                                                                          | D5           |            |           |               |                 |          |  |

|        | <br> -                 |                |                                                                                                                                                                          |              |            | _         | -             | - GO/O          |          |  |

|        | <br> -                 | D6             |                                                                                                                                                                          | D6           |            | •         | S9            | S8/s8uc         |          |  |

|        |                        | D7             |                                                                                                                                                                          | D7           | (          |           | 1             | 1               |          |  |

|        |                        | Connect th     | e unused p                                                                                                                                                               | oins to VDI  | OR VS      | S         |               |                 |          |  |

| 1.0    | DD/WD1)                | These termin   | nals contro                                                                                                                                                              | ls the read/ | write ope  | ration of | host interfac | e.              |          |  |

| 18     | RD(WR1)                |                |                                                                                                                                                                          | 8080         | )          | (         | 6800          | Serial          |          |  |

|        | i<br>I                 | WR             |                                                                                                                                                                          | /RW          | 7          |           | R/W           | 0               |          |  |

| 19     | WR                     | RD(W           |                                                                                                                                                                          | /RD          |            |           | EN            | 0               |          |  |

|        |                        |                |                                                                                                                                                                          |              |            | verita an |               | mode, CD pin is | no       |  |

| 20     | CD                     | used, connec   |                                                                                                                                                                          |              |            |           |               | ': display data | 110      |  |

| 21     | RST                    | Reset signal   |                                                                                                                                                                          |              |            |           |               |                 |          |  |

| 22     | CS                     | Chip select s  | signal                                                                                                                                                                   |              |            |           |               |                 |          |  |

| 23     | BM0                    | The interfa    | ce bus me                                                                                                                                                                | ode is det   | ermined    | by ME     | B[1:0] and I  | D[7:6] by the f | ollowing |  |

|        |                        | relationship.  |                                                                                                                                                                          |              |            | •         | . ,           |                 | C        |  |

|        | <u> </u>               | BM[1:0]        | D[7:6]                                                                                                                                                                   | MODE         |            |           |               |                 |          |  |

|        | <u> </u>               | 11             | Data                                                                                                                                                                     | 6800/8bit    |            |           |               |                 |          |  |

| 04     | DM1                    |                |                                                                                                                                                                          |              |            |           |               |                 |          |  |

| 24     | BM1                    | 10             | Data                                                                                                                                                                     | 8080/8bit    |            |           |               |                 |          |  |

|        |                        | 01             | 0x                                                                                                                                                                       | 6800/4bit    |            |           |               |                 |          |  |

|        |                        | 00             | 0x                                                                                                                                                                       | 8080/4bit    |            |           |               |                 |          |  |

|        |                        | 01             | 10                                                                                                                                                                       | 3-wire SI    | PI w/9-bit | token.(s  | s9:convention | al)             |          |  |

| 00 | 10 | 4-wire SPI w/8-bit token.(s8:conventional) |  |

|----|----|--------------------------------------------|--|

| 00 | 11 | 3-or 4-wire SPI w/8-bit token.(s8ul)       |  |

## 7. MAXIMUM ABSOUTE LIMIT (Voltage Reference to VSS)(for IC)

| Symbol                              | Parameter                                                         | Min. | Max.                  | Unit |

|-------------------------------------|-------------------------------------------------------------------|------|-----------------------|------|

| $V_{DD}$                            | Logic Supply voltage                                              | -0.3 | +4.0                  | ٧    |

| $V_{DD2}$                           | LCD Generator Supply voltage                                      | -0.3 | +4.0                  | V    |

| $V_{DD3}$                           | Analog Circuit Supply voltage                                     | -0.3 | +4.0                  | ٧    |

| V <sub>DD2/3</sub> -V <sub>DD</sub> | Voltage difference between V <sub>DD</sub> and V <sub>DD2/3</sub> | -    | 1.6                   | ٧    |

| V <sub>LCD</sub>                    | LCD Generated voltage (-30°C ∼ +80°C)                             | -0.3 | +17.0                 | ٧    |

| V <sub>IN</sub>                     | Any input voltage                                                 | -0.4 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>OPR</sub>                    | Operating temperature range                                       | -30  | +85                   | °C   |

| T <sub>STR</sub>                    | Storage temperature                                               | -55  | +125                  | °C   |

#### Note:

- 1.  $V_{DD}$  is based on  $V_{SS} = 0V$

- 2. Stress values listed above may cause permanent damages to the device.

#### **8. ELECTRICAL CHARACTERISTICS**

#### DC CHARACTERISTICS

| Symbol              | Parameter                  | Conditions                                   | Min.               | Тур.    | Max.               | Unit |

|---------------------|----------------------------|----------------------------------------------|--------------------|---------|--------------------|------|

| $V_{DD}$            | Supply for digital circuit |                                              | 2.7                | 2.8~3.3 | 3.6                | V    |

| V <sub>DD2/3</sub>  | Supply for bias & pump     |                                              | 2.7                | 2.8~3.3 | 3.6                | ٧    |

| V <sub>LCD</sub>    | Charge pump output         | V <sub>DD2/3</sub> ≥ 2.7V, 25 <sup>0</sup> C |                    | 12.5    | 16                 | V    |

| VD                  | LCD data voltage           | $V_{DD2/3} \ge 2.7V, 25^{\circ}C$            |                    |         | 1.53               | V    |

| V <sub>IL</sub>     | Input logic LOW            |                                              |                    | 300     | 0.2V <sub>DD</sub> | V    |

| V <sub>IH</sub>     | Input logic HIGH           |                                              | 0.8V <sub>DD</sub> | 90      |                    | ٧    |

| VoL                 | Output logic LOW           |                                              |                    |         | 0.2V <sub>DD</sub> | V    |

| Voн                 | Output logic HIGH          |                                              | 0.8V <sub>DD</sub> |         | 32                 | V    |

| I <sub>IL</sub>     | Input leakage current      |                                              |                    | 3 3     | 1.5                | μΑ   |

| CIN                 | Input capacitance          |                                              |                    | 5       | 10                 | PF   |

| Cout                | Output capacitance         |                                              |                    | 5       | 10                 | PF   |

| Ro(SEG)             | SEG output impedance       | V <sub>LCD</sub> = 12.5V                     |                    | 1.5     | 3                  | kΩ   |

| R <sub>0(COM)</sub> | COM output impedance       | V <sub>LCD</sub> = 9                         |                    | 1.5     | 3                  | kΩ   |

| $f_{LINE}$          | Average frame rate         |                                              | 69                 | 75      | 122                | Hz   |

#### POWER CONSUMPTION

$V_{DD}$  = 2.7V,  $V_{DD2/3}$  = 2.7V, Bias Ratio (BR) = 10b, GN = 11b, PM = 000000b, Panel Loading (PL): 26~43nF, MR = 128, Bus mode = 6800,  $C_L$  = 0.1 $\mu$ F,  $C_B$  = 4.7 $\mu$ F. All outputs are open circuit.

| Display Pattern | Conditions                   | Тур. (µА)       | Max. (µA) |

|-----------------|------------------------------|-----------------|-----------|

| All-OFF         | Bus = idle                   | 580             | 870       |

| 2-pixel checker | Bus = idle                   | 730             | 1095      |

| - T-3           | Bus = idle (standby current) | 2 <del>35</del> | 5         |

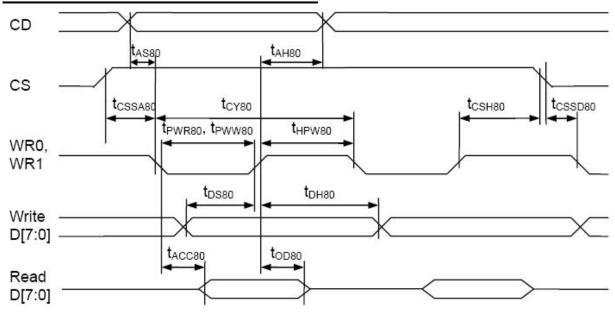

#### 9. TIMING CHARACTERISTICS

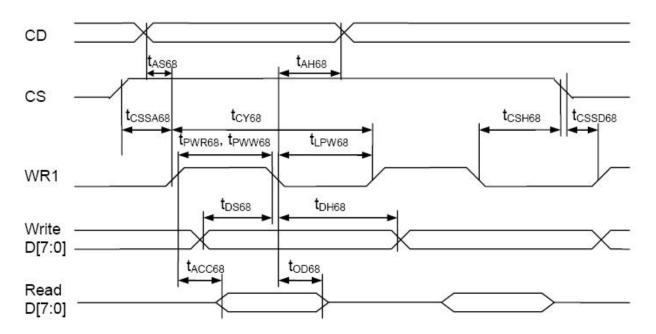

FIGURE 15: Parallel Bus Timing Characteristics (for 8080 MCU)

$(2.7 \text{V} \le \text{V}_{DD} < 3.6 \text{V}, \text{Ta} = -30 \text{ to } +85^{\circ}\text{C})$

| Symbol                                                          | Signal   | Description                                                          | Condition              | Min.                 | Max.           | Units |

|-----------------------------------------------------------------|----------|----------------------------------------------------------------------|------------------------|----------------------|----------------|-------|

| t <sub>AS80</sub><br>t <sub>AH80</sub>                          | CD       | Address setup time<br>Address hold time                              |                        | 0<br>20              | 1. <del></del> | nS    |

| t <sub>CY80</sub>                                               |          | System cycle time 8-bit bus (read)                                   |                        | 140<br>140           | ( <del>-</del> | nS    |

|                                                                 |          | 8-bit bus (write)<br>4-bit bus (read)<br>4-bit bus (write)           |                        | 140<br>140<br>140    |                |       |

| t <sub>PWR80</sub>                                              | WR1      | Pulse width<br>8-bit bus (read)<br>4-bit bus (read)                  |                        | 65<br>65             | -              | nS    |

| t <sub>PWW80</sub>                                              | WR0      | Pulse width 8-bit bus (write) 4-bit bus (write)                      |                        | 35<br>35             | -              | nS    |

| t <sub>HPW80</sub>                                              | WR0, WR1 | High pulse width  8-bit bus (read) (write)  4-bit bus (read) (write) |                        | 65<br>35<br>65<br>35 | -              | nS    |

| t <sub>DS80</sub><br>t <sub>DH80</sub>                          | D0~D7    | Data setup time<br>Data hold time                                    |                        | 30<br>20             | -              | nS    |

| t <sub>ACC80</sub><br>t <sub>OD80</sub>                         |          | Read access time<br>Output disable time                              | C <sub>L</sub> = 100pF | -<br>12              | 60<br>20       | nS    |

| t <sub>SSA80</sub><br>t <sub>CSSD80</sub><br>t <sub>CSH80</sub> | CS1/CS0  | Chip select setup time                                               |                        | 10<br>10<br>20       |                | nS    |

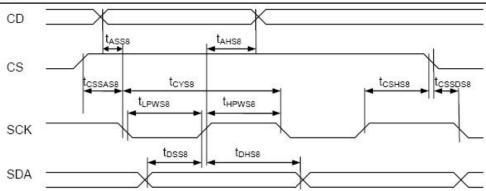

FIGURE 16: Parallel Bus Timing Characteristics (for 6800 MCU)

$(2.7V \le V_{DD} < 3.6V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol                                                           | Signal   | Description                                                                                       | Condition              | Min.                     | Max.     | Units |

|------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------|------------------------|--------------------------|----------|-------|

| t <sub>AS68</sub><br>t <sub>AH68</sub>                           | CD       | Address setup time<br>Address hold time                                                           |                        | 0<br>20                  | -        | nS    |

| Тсүев                                                            |          | System cycle time  8-bit bus (read)  8-bit bus (write)  4-bit bus (read)  4-bit bus (write)       |                        | 140<br>140<br>140<br>140 | =        | nS    |

| t <sub>PWR68</sub>                                               | WR1      | Pulse width<br>8-bit bus (read)<br>4-bit bus (read)                                               |                        | 65<br>65                 | =        | nS    |

| tpww68                                                           | WR0      | Pulse width<br>8-bit bus (write)<br>4-bit bus (write)                                             |                        | 35<br>35                 | _        | nS    |

| t <sub>LPW68</sub>                                               | WR0, WR1 | Low pulse width<br>8-bit bus (read)<br>8-bit bus (write)<br>4-bit bus (read)<br>4-bit bus (write) |                        | 65<br>35<br>65<br>35     | =:       | nS    |

| t <sub>DS68</sub><br>t <sub>DH68</sub>                           | D0~D7    | Data setup time<br>Data hold time                                                                 |                        | 30<br>20                 | -        | nS    |

| t <sub>ACC68</sub><br>t <sub>OD68</sub>                          |          | Read access time<br>Output disable time                                                           | C <sub>L</sub> = 100pF | -<br>12                  | 60<br>20 | nS    |

| t <sub>CSSA68</sub><br>t <sub>CSSD68</sub><br>t <sub>CSH68</sub> | CS1/CS0  | Chip select setup time                                                                            |                        | 10<br>10<br>20           |          | nS    |

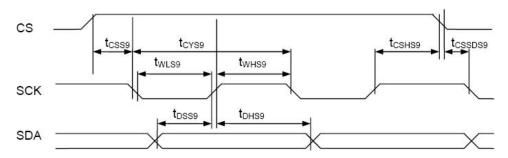

FIGURE 17: Serial Bus Timing Characteristics (for S8 / S8uc)

$(2.7V \le V_{DD} < 3.6V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol                                 | Signal | Description                       | Condition | Min.           | Max.          | Units |

|----------------------------------------|--------|-----------------------------------|-----------|----------------|---------------|-------|

| t <sub>ASS8</sub>                      | CD     | Address setup time                |           | 0              | <u>-</u>      | nS    |

| t <sub>AHS8</sub>                      | CD     | Address hold time                 |           | 20             | <u> </u>      | nS    |

| t <sub>CYS8</sub>                      |        | System cycle time                 |           | 140            | _             | nS    |

| t <sub>LPWS8</sub>                     | SCK    | Low pulse width                   |           | 65             | -             | nS    |

| t <sub>HPWS8</sub>                     |        | High pulse width                  |           | 65             | ( <del></del> | nS    |

| t <sub>DSS8</sub><br>t <sub>DHS8</sub> | SDA    | Data setup time<br>Data hold time |           | 30<br>20       | · ·           | nS    |

| tcssase<br>tcssdse<br>tcshse           | cs     | Chip select setup time            |           | 10<br>20<br>10 |               | nS    |

FIGURE 18: Serial Bus Timing Characteristics (for S9)

$(2.7 \text{V} \le \text{V}_{DD} < 3.6 \text{V}, \text{Ta} = -30 \text{ to } +85^{\circ}\text{C})$

| Symbol                                 | Signal | Description                       | Condition | Min.           | Max. | Units |

|----------------------------------------|--------|-----------------------------------|-----------|----------------|------|-------|

| t <sub>CYS9</sub>                      |        | System cycle time                 |           | 140            | -    | nS    |

| t <sub>LPWS9</sub>                     | SCK    | Low pulse width                   |           | 65             | -    | nS    |

| t <sub>HPWS9</sub>                     |        | High pulse width                  |           | 65             | -    | nS    |

| t <sub>DSS9</sub><br>t <sub>DHS9</sub> | SDA    | Data setup time<br>Data hold time |           | 30<br>20       | -    | nS    |

| tcssas9<br>tcssbs9<br>tcshs9           | cs     | Chip select setup time            |           | 10<br>20<br>10 |      | nS    |

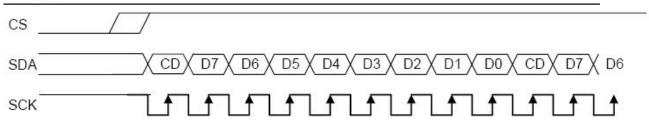

FIGURE 4.c: 3-wire Serial Interface (S9)

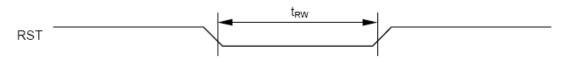

#### **RESET TIMING**

Reset Characteristics

$(2.7V \le V_{DD} < 3.6V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol          | Signal | Description           | Condition | Min. | Max. | Units |

|-----------------|--------|-----------------------|-----------|------|------|-------|

| t <sub>RW</sub> | RST    | Reset low pulse width |           | 1000 | -    | nS    |

#### 10. CONTROL AND DISPLAY INSTRUCTION

- # Useful Data bits

- Don't Care

|    | Command                                             | C/D | W/R | D7  | D6     | D5  | D4     | D3  | D2  | D1     | D0     | Action                             | Default           |

|----|-----------------------------------------------------|-----|-----|-----|--------|-----|--------|-----|-----|--------|--------|------------------------------------|-------------------|

| 1  | Write Data Byte                                     | 1   | 0   | #   | #      | #   | #      | #   | #   | #      | #      | Write 1 byte                       | N/A               |

| 2  | Read Data Byte                                      | 1   | 1   | #   | #      | #   | #      | #   | #   | #      | #      | Read 1 byte                        | N/A               |

| 3  | Get Status                                          | 0   | 1   | BZ  | MX     | DE  | RS     | WA  | GN1 | GN0    | 1      | Get Status                         | N/A               |

| 4  | Set Column Address LSB                              | 0   | 0   | 0   | 0      | 0   | 0      | #   | #   | #      | #      | Set CA[3:0]                        | 0                 |

| 4  | Set Column Address MSB                              | 0   | 0   | 0   | 0      | 0   | 1      | #   | #   | #      | #      | Set CA[7:4]                        | 0                 |

| 5  | Set Mux Rate and temperature compensation.          | 0   | 0   | 0   | 0      | 1   | 0      | 0   | #   | #      | #      | Set {MR, TC[1:0]}                  | MR: 1b<br>TC: 00b |

| 6  | Set Power Control                                   | 0   | 0   | 0   | 0      | 1   | 0      | 1   | #   | #      | #      | Set PC[2:0]                        | 101b              |

| 7  | Set Adv. Program Control.                           | 0   | 0   | 0   | 0      | 1   | 1      | 0   | 0   | 0      | R      | For UltraChip only.                | N/A               |

| 1  | (double byte command)                               | 0   | 0   | #   | #      | #   | #      | #   | #   | #      | #      | Do not use.                        | IN/A              |

| 8  | Set Start Line                                      | 0   | 0   | 0   | 1      | #   | #      | #   | #   | #      | #      | Set SL[5:0]                        | 0                 |

| 9  | Set Gain and Potentiometer<br>(double-byte command) | 0   | 0   | 1 # | 0<br># | 0   | 0<br># | 0 # | 0   | 0<br># | 1 #    | Set {GN[1:0],<br>PM[5:0]}          | GN=3<br>PM=0      |

| 10 | Set RAM Address Control                             | 0   | 0   | 1   | 0      | 0   | 0      | 1   | #   | #      | #      | Set AC[2:0]                        | 001b              |

| 11 | Set All-Pixel-ON                                    | 0   | 0   | 1   | 0      | 1   | 0      | 0   | 1   | 0      | #      | Set DC[1]                          | 0=disable         |

| 12 | Set Inverse Display                                 | 0   | 0   | 1   | 0      | 1   | 0      | 0   | 1   | 1      | #      | Set DC[0]                          | 0=disable         |

| 13 | Set Display Enable                                  | 0   | 0   | 1   | 0      | 1   | 0      | 1   | 1   | 1      | #      | Set DC[2]                          | 0=disable         |

| 14 | Set Fixed Lines                                     | 0   | 0   | 1   | 0      | 0   | 1      | #   | #   | #      | #      | Set FL[3:0]                        | 0                 |

| 15 | Set Page Address                                    | 0   | 0   | 1   | 0      | 1   | 1      | #   | #   | #      | #      | Set PA[3:0]                        | 0                 |

| 16 | Set LCD Mapping Control                             | 0   | 0   | 1   | 1      | 0   | 0      | #   | #   | #      | #      | Set LC[3:0]                        | 0                 |

| 17 | System Reset                                        | 0   | 0   | 1   | 1      | 1   | 0      | 0   | 0   | 1      | 0      | System Reset                       | N/A               |

| 18 | NOP                                                 | 0   | 0   | 1   | 1      | 1   | 0      | 0   | 0   | 1      | 1      | No operation                       | N/A               |

| 19 | Set LCD Bias Ratio                                  | 0   | 0   | 1   | 1      | 1   | 0      | 1   | 0   | #      | #      | Set BR[1:0]                        | 10b=12            |

| 20 | Reset Cursor Mode                                   | 0   | 0   | 1   | 1      | 1   | 0      | 1   | 1   | 1      | 0      | AC[3]=0, CA=CR                     | N/A               |

| 21 | Set Cursor Mode                                     | 0   | 0   | 1   | 1      | 1   | 0      | 1   | 1   | 1      | 1      | AC[3]=1, CR=CA                     | N/A               |

| 22 | Set Test Control<br>(double byte command)           | 0   | 0   | 1 # | 1 #    | 1 # | 0      | 0 # | 1 # | #      | T<br># | For UltraChip only.<br>Do not use. | N/A               |

<sup>\*</sup> Other than commands listed above, all other bit patterns may result in undefined behavior.

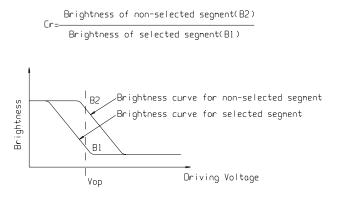

## $\frac{\textbf{11. ELECTRO-OPTICAL CHARACTERISTICS}}{(V_{DD}=3.3V,\,Ta=25^{\circ}C)}$

| Item                      | Symbol | Condition                        | Min  | Тур  | Max  | Unit |

|---------------------------|--------|----------------------------------|------|------|------|------|

| Operating Voltage for LCD |        | $Ta = -20^{\circ}C$              | 14.7 | 15.0 | 15.3 |      |

|                           | Vop    | Vop $Ta = 25^{\circ}C$ 14.2 14.5 | 14.5 | 14.8 | V    |      |

|                           |        | $Ta = 70^{\circ}C$               | 13.7 | 14.0 | 14.3 |      |

| Dagaga dina               | Tr     | Ta = 25°C                        |      | 250  | 500  | ms   |

| Response time             | Tf     |                                  |      | 300  | 600  | ms   |

| Contrast                  | Cr     | $Ta = 25^{\circ}C$               | 2    | 10   |      |      |

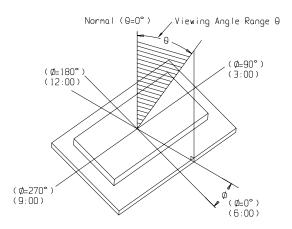

| Viewing angle range       | θ      | Cr≥2                             | -35  |      | +35  | deg  |

|                           | Ф      | Cr=2                             | -35  |      | +40  | deg  |

## 12. BACK LIGHT CHARACTERISTICS LCD Module with Edge white LED Backlight

ELECTRICAL RATINGS. Ta = 25°C

| Item                            | Symbol | Condition | Min  | Тур | Max  | Unit  |

|---------------------------------|--------|-----------|------|-----|------|-------|

| Forward Curret                  | IF     | VF=3.5V   |      | 90  | 110  | mA    |

| Reverse Current                 | IR     | VR=0.8V   |      | 30  |      | mA    |

| Luminous Intensity(Without LCD) | Lv     | VF=3.5V   | 300  | 380 |      | cd/m2 |

| Color coordinates(without       | X      | VF=3.5V   | 0.27 |     | 0.31 |       |

| LCD)                            | Y      | VT-3.3 V  | 0.26 |     | 0.30 |       |

| Color                           | white  |           |      |     |      |       |

#### Note:

During high temperature operation, please refer to the LED spec(current vs temperature) to decide the current of single LED.

#### 13. PRECAUTION FOR USING LCD/LCM

After reliability test, recovery time should be 24 hours minimum. Moreover, functions, performance and appearance shall be free from remarkable deterioration within 50,000 hours(average) under ordinary operating and storage conditions room temperature (20±8°C), normal humidity (below 65% RH), and in the area not exposed to direct sun light. Using LCM beyond these conditions will shorten the life time.

Precaution for using LCD/LCM

LCD/LCM is assembled and adjusted with a high degree of precision. Do not attempt to make any alteration or modification. The followings should be noted.

#### **General Precautions:**

- 1. LCD panel is made of glass. Avoid excessive mechanical shock or applying strong pressure onto the surface of display area.

- 2. The polarizer used on the display surface is easily scratched and damaged. Extreme care should be taken when handling. To clean dust or dirt off the display surface, wipe gently with cotton, or other soft material soaked with isoproply alcohol, ethyl alcohol or trichlorotriflorothane, do not use water, ketone or aromatics and never scrub hard.

- 3. Do not tamper in any way with the tabs on the metal frame.

- 4. Do not made any modification on the PCB without consulting Orient Display.

- 5. When mounting a LCM, make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of the elements.

- 6. Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels and also cause rainbow on the display.

- 7. Be careful not to touch or swallow liquid crystal that might leak from a damaged cell. Any liquid crystal adheres to skin or clothes, wash it off immediately with soap and water.

#### **Static Electricity Precautions:**

- 1. CMOS-LSI is used for the module circuit; therefore operators should be grounded whenever he/she comes into contact with the module.

- 2. Do not touch any of the conductive parts such as the LSI pads; the copper leads on the PCB and the interface terminals with any parts of the human body.

- 3. Do not touch the connection terminals of the display with bare hand; it will cause disconnection or defective insulation of terminals.

- 4. The modules should be kept in anti-static bags or other containers resistant to static for storage.

- 5. Only properly grounded soldering irons should be used.

- 6. If an electric screwdriver is used, it should be grounded and shielded to prevent sparks.

- 7. The normal static prevention measures should be observed for work clothes and working benches.

- 8. Since dry air is inductive to static, a relative humidity of 50-60% is recommended.

#### **Soldering Precautions:**

- 1. Soldering should be performed only on the I/O terminals.

- 2. Use soldering irons with proper grounding and no leakage.

- 3. Soldering temperature: 350°C+10°C

- 4. Soldering time: 3 to 4 second.

- 5. Use eutectic solder with resin flux filling.

- 6. If flux is used, the LCD surface should be protected to avoid spattering flux.

- 7. Flux residue should be removed.

#### **Operation Precautions:**

- 1. The viewing angle can be adjusted by varying the LCD driving voltage Vo.

- 2. Since applied DC voltage causes electro-chemical reactions, which deteriorate the display, the applied pulse waveform should be a symmetric waveform such that no DC component remains. Be sure to use the specified operating voltage.

- 3. Driving voltage should be kept within specified range; excess voltage will shorten display life.

- 4. Response time increases with decrease in temperature.

- 5. Display color may be affected at temperatures above its operational range.

- 6. Keep the temperature within the specified range usage and storage. Excessive temperature and humidity could cause polarization degradation, polarizer peel-off or generate bubbles.

- 7. For long-term storage over 40°C is required, the relative humidity should be kept below 60%, and avoid direct sunlight.

#### **Limited Warranty**

Orient DisplyayLCDs and modules are not consumer products, but may be incorporated by Orient's customers into consumer products or components thereof, Orient Display does not warrant that its LCDs and components are fit for any such particular purpose.

- The liability of Orient Display is limited to repair or replacement on the terms set forth below.

Orient Display will not be responsible for any subsequent or consequential events or injury or

damage to any personnel or user including third party personnel and/or user. Unless otherwise

agreed in writing between Orient and the customer, Orient will only replace or repair any of its

LCD which is found defective electrically or visually when inspected in accordance with Orient

general LCD inspection standard.

- (Copies available on request)

- 2. No warranty can be granted if any of the precautions state in handling liquid crystal display above has been disregarded. Broken glass, scratches on polarizer mechanical damages as well as defects that are caused accelerated environment tests are excluded from warranty.

3. In returning the LCD/LCM, they must be properly packaged; there should be detailed description of the failures or defect.

#### 14. LCM TEST CRITERIA

#### 1. Objective

The criteria is applied for consolidating the LCM quality standard between Orient Display and customer in finished products acceptance inspection and shipment, to guarantee the products quality to meet with customer's demand.

#### 2. Scope

2.1 This criteria is applicable to all the LCM products produced by Orient Display.

#### 3. Inspection equipment

Function Tester、Vernier Calipers、Microscope、Magnifier、ESD Wrist Strap、Finger Cover、Labels、High-Low Temperature Oven、Refrigerator、Constant Voltage Power Supply (DC), Desk Lamp, etc.

#### 4. Sampling Plan and Reference Standard

4.1.1 According to GB/T 2828.1---2003/ISO2859-1:1999, single sampling under normal inspection, general inspection level II.

| Item of Inspection | Times of Sampling  | AQL Judgment  |

|--------------------|--------------------|---------------|

| Cosmetic           | II Single Sampling | MA=0.4 MI=1.5 |

| Mechanical         | N=3                | C=0           |

| Functional         | II Single Sampling | MA=0.4 MI=1.5 |

- 4.1.2 GB/T 2828.1---2003/ISO2859-1:1999 Counting and sampling procedures and sampling table for Batch-to-Batch Inspection.

- 4.1.3 GB/T 1619.96 Test method for TN LCD.

- 4.1.4 GB/T 12848.91 General Specification for STN LCD.

- 4.1.5 GB2421-89 Basic Environmental Test Procedures for Electrical and Electronic Products

- 4.1.6 IPC-A-610C Acceptance Condition for Electrical Assemblies.

#### 5. Inspection Condition and Inspection Reference

5.1 The ambient temperature and humidity are  $25\pm5\,^{\circ}\text{C}$  and  $45\pm20\%\text{RH}$  respectively, and the ambient luminance should be more than  $300\text{cd/cm}^2$ . The distance between inspector's eyes and the LCD panel should be 30cm away. Normally we inspect products with reflected light, when we inspect the LCD produces with backlight turned on, the ambient luminance should be less than  $100\text{cd/cm}^2$ .

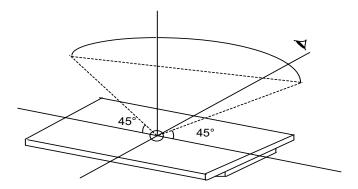

5.2 The LCD should be test with 45° both left and right side, 0-45° both upside and downside (if for STN product, -20-55° is needed).

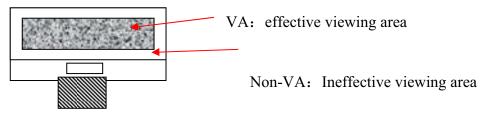

#### 5.3 Definition of VA

- 5.4 Inspection with viewed eyes (not including defect size measure by magnifiers).

- 5.5 Electrical property

Inspect with the test jig to meet with the requirement indicated in the approved documents, including the pattern design and the display performance.

- 5.5.1 Testing voltage (V)

- 5.5.1.1 According to the inspection of test jig and production specification the test voltage setting is  $Vop \pm 0.3V$  when the Vop is under 9.0V, and  $Vop \pm 3\%Vop$  when the Vop is above 9.0V.

- 5.5.1.2 As per the product with the fixed voltage the test voltage setting is same as Vop and keeps the constant voltage through the internal circuit. And the limited sample on the voltage range is needed if necessary.

- 5.5.2 Current Consumption (I): refer to product document and approval drawing to confirm it.

#### 6. Inspection Item and Acceptance Standard

6.1 Outer dimension: For the outer dimension and the sizes which could influence the assembly at the customer's side, it should be in accordance to the approval drawing, and it belongs to the major defect.

#### 6.2 Functional Test:

| No.    | Item                      | Description                                                                                                                                 | MAJ      | MIN      | Accept standard                                                                            |

|--------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------------------------------------------------------------------------------------|

| 6.2.1  | Missing<br>Segment        | Any missing segment caused by an open circuit; Any missing COM, pattern, dot or segment caused by an open circuit or poor crossover contact | √        |          | Rejected                                                                                   |

| 6.2.3  | No display/no action      | No segment is displayed when the product is connected correctly.                                                                            | <b>√</b> |          | Rejected                                                                                   |

| 6.2.4  | Display<br>error/abnormal | The display pattern and display order is not as required under the normal scanning procedure.                                               | <b>√</b> |          | Rejected                                                                                   |

| 6.2.5  | Viewing angle wrong       | The direction with the best display of patterns should be as customer required (or refer to the approval samples)                           | <b>√</b> |          | Rejected                                                                                   |

| 6.2.6  | Display<br>dim/dark       | The contrast of LCD is too dark or too dim under normal operation                                                                           | 1        |          | Beyond the voltage tolerance, Rejected                                                     |

| 6.2.7  | Slow response             | Response of some segments is different with others when turned on or off the LCD                                                            | ✓        |          | Rejected                                                                                   |

| 6.2.8  | Extra segment             | Display of wiring, or extra pattern, caused by wrong alignment or insufficient corrosion                                                    |          | 1        | refer to<br>spot/line<br>standard                                                          |

| 6.2.9  | Dim segment               | Under the normal voltage, the contrast of segment are uneven                                                                                |          | 1        | Reject or refer to samples                                                                 |

| 6.2.10 | PI black/white spot       | Partial black and white spot are visible while changing display content due to the PI layer defective                                       |          | 4        | refer to the spot/line criteria for the visible spots when display image stopped, others O |

| 6.2.11 | pinhole/white<br>spot     | The phenomena of missing patterns when turned on caused by missing of ITO fragment.                                                         |          | <b>√</b> | refer to<br>spot/line<br>standard                                                          |

|        |                       | d = (X+Y)/2                                                                                                                                                                    |   |                                   |

|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------|

| 6.2.12 | Pattern<br>distortion | Width of pattern displayed is wider, narrower or deformed from the specifications caused by wrong alignment, i.e. extra heave or missing:  Ia-Ib ≤ 1/4W(W is the normal width) | √ | Acceptable  Ia-Ib >1/4W, rejected |

| 6.2.13 | High current          | the current is bigger than regulated value.                                                                                                                                    | √ | Rejected                          |

#### 6.3 LCD Visual Defect

#### 6.3.1 Dot defect(defined within VA, out of VA spots not accounted)

| Defect item                           | Average diameter (d                                         | Accept numbers | MAJ | MIN |

|---------------------------------------|-------------------------------------------------------------|----------------|-----|-----|

| Spot defect                           | d≤0.2                                                       | 3              |     |     |

| (black spot, foreign                  | 0.2 <d≤0.25< td=""><td>2</td><td></td><td>\</td></d≤0.25<>  | 2              |     | \   |

| material, nick, scratches, LC defect) | 0.25 <d≤0.30< td=""><td>1</td><td></td><td>•</td></d≤0.30<> | 1              |     | •   |

#### 6.3.2 Line defect(defined within VA, out of VA spots not accounted)

| Defective item              | length(L) | width(W) | Accept numbers | MAJ | MIN |

|-----------------------------|-----------|----------|----------------|-----|-----|

| line defect (scratch, liner | ≤5.0      | ≤0.02    | 3              |     |     |

| foreign material)           | €3.0      | ≤0.03    | 3              |     | ļ , |

|                             | €3.0      | €0.05    | 1              |     | •   |

note: 1. If the width is bigger than 0.1mm, it can be treated as spot defect.

#### 6.3.3 Polarizer Air Bubble (defined within VA, out of VA spots not accounted)

| Defective item                          | Average diameter (d                                             | Accept numbers | MAJ | MIN      |

|-----------------------------------------|-----------------------------------------------------------------|----------------|-----|----------|

| polarizer Air Bubble Concave-Convex Dot | d≤0.3                                                           | 3              |     |          |

|                                         | 0.3 <d≤0.5< td=""><td>2</td><td></td><td><b> </b></td></d≤0.5<> | 2              |     | <b> </b> |

| d=(w+1)/2                               | 0.5 <d≤0.8< td=""><td>1</td><td></td><td></td></d≤0.8<>         | 1              |     |          |

6.3.4 Damaged(For the products with LCD edge expose to outside without mental frame, including products in COG, with H/S or assembled with backlight)

| No.     | Item                             | Accepta                                                                                                                                                                                     | nce Standard                                    | MAJ | MIN          |  |

|---------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|--------------|--|

|         | Chin on load                     |                                                                                                                                                                                             | (mm)                                            |     |              |  |

|         | Chip on lead                     | X                                                                                                                                                                                           | ≤1/8L                                           |     |              |  |

|         |                                  | Y                                                                                                                                                                                           | ≤1/3W                                           |     | $\checkmark$ |  |

| 6.3.4.1 | Z                                | Z                                                                                                                                                                                           | ≤1/2t                                           |     |              |  |

|         |                                  | Accept<br>number                                                                                                                                                                            | 2                                               |     |              |  |

|         | TX                               |                                                                                                                                                                                             | 2mm, neglect the lead, and not perfoax, accept. |     |              |  |

|         | chip on corner(ITO lead)         |                                                                                                                                                                                             | (mm)                                            | MAJ | MIN          |  |

|         | cmp on corner(110 lead)          | X                                                                                                                                                                                           | Not enter into frame epoxy                      |     |              |  |

|         |                                  | Y                                                                                                                                                                                           | and touch the lead                              |     |              |  |

| 6.3.4.2 | Z                                | Z                                                                                                                                                                                           | ≤t                                              |     | √            |  |

|         |                                  | Accept numbers                                                                                                                                                                              | 2                                               |     |              |  |

|         |                                  |                                                                                                                                                                                             | ner refer to 6.3.4.3 y. If chips on lead,       |     |              |  |

|         | Chip on sealed area (outer chip) |                                                                                                                                                                                             | (mm)                                            | MAJ | MIN          |  |

|         |                                  | X                                                                                                                                                                                           | ≤1/8 L                                          |     |              |  |

|         | \ \ \                            | Y                                                                                                                                                                                           | ≤1/2H                                           |     | ,            |  |

| 6.3.4.3 |                                  | Z                                                                                                                                                                                           | ≤ 1/2t                                          |     | √            |  |

|         |                                  | Accept numbers                                                                                                                                                                              | 2                                               |     |              |  |

|         | z dass thickness I length H. The | The standard for inner chip on sealed area is same as the standard for outer. If chip on the opposite side of ITO lead, the value Y refer to 6.3.4.1 for the chip on the side without lead. |                                                 |     |              |  |

note: t---glass thickness, L---length, H---The distance between the LCD edge to the inner of LCD frame epoxy. W—The width of ITO lead

#### 6.3.5 Others

| No. | Item | Description | MAJ | MIN | Accept standard |

|-----|------|-------------|-----|-----|-----------------|

|-----|------|-------------|-----|-----|-----------------|

# ORIENT DISPLAY (North America) Limited

| 6.3.5.1 | Newton/<br>B/G color<br>uniformity<br>not good | There exists more than one color on one product or same batch. |          | √ | Reject or refer<br>to limited<br>sample |

|---------|------------------------------------------------|----------------------------------------------------------------|----------|---|-----------------------------------------|

| 6.3.5.2 | Leakage(LC)                                    | /                                                              | <b>√</b> |   | Rejected                                |

| 6.3.5.3 | No<br>protective<br>film                       | /                                                              |          | √ | Rejected                                |

#### 6.4 Backlight components

| No.   | Item                                  | Description                                                                                                                                                              | MAJ | MIN      | Accept standard             |

|-------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------------------------|

| 6.4.1 | Backlight<br>not work,<br>wrong color | /                                                                                                                                                                        | √   |          | Rejected                    |

| 6.4.2 | Color<br>deviation                    | Turn backlight, the color differ from the sample, do not match the drawing after testing                                                                                 |     | <b>√</b> | Refer to sample and drawing |

| 6.4.3 | Brightness<br>deviation               | Turn on backlight, the brightness is differ from the sample, or do not match the drawing after testing, or over $\pm 30\%$ compare with sample if drawing not specified. |     | <b>√</b> | Refer to sample and drawing |

| 6.4.4 | Uneven<br>brightness                  | Turn on the backlight, the brightness is uneven on the same LED and beyond the specification of drawing.                                                                 |     | √        | Refer to sample and drawing |

| 6.4.5 | Spot/line scratch                     | There is stain, scratches on backlight when turn on.                                                                                                                     |     | <b>√</b> | Refer to 6.3.1/6.3.2        |

#### 6.5 Mental frame

| No.   | Item                                                                           | Description                                                                                                                                                                                                                                                | MAJ | MIN | Accept standard |

|-------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| 6.5.1 | material/surface                                                               | Mental frame/surface approach inconsistent with specification.                                                                                                                                                                                             | √   |     | Rejected        |

| 6.5.2 | Twist not qualified/without twisting                                           | Twist method/direction wrong, not twist as required                                                                                                                                                                                                        | √   |     | Rejected        |

| 6.5.3 | Oxidized steak, paint<br>stripped, color<br>changed, dented<br>mark, scratches | 1.Oxidized steak on the surface of the metal frame;2. front surface paint scratch to substrate, the stripped spot ≤0.8mm and exceed 3 areas;3.line defect in length≤5.0mm and width ≤0.05mm exceed 2 areas, front dent, bubble and side surface have paint |     | √   | Rejected        |

|       |        | stripping to substrate≤1.0mm<br>exceed 3 areas, line defect in width<br>≤0.05mm exceed 3 areas. |          |          |

|-------|--------|-------------------------------------------------------------------------------------------------|----------|----------|

| 6.5.4 | Burred | Burr is too long, enter into viewing area                                                       | <b>√</b> | Rejected |

#### 6.6 PCB/COB

| No.   | Item                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MAJ | MIN | Accept standard |

|-------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| 6.6.1 | Epoxy<br>Cover<br>Improper | <ol> <li>The Pad within the round white mark is exposed to outside.</li> <li>The height of epoxy covers beyond document /drawing specification.</li> <li>The epoxy should be covered within the white round mark and the maximum overage is 2mm more than the radius of white mark.</li> <li>Clear liner mark on COB surface or pinhole that it is possible to penetrate through the epoxy to chip.</li> <li>The pinhole diameter over 0.25mm or other material on COB surface.</li> </ol> |     | ✓   | Rejected        |

| 6.6.2 | PCB<br>cosmetic<br>defect  | <ol> <li>PCB pad surface can not be oxidized or contaminated.</li> <li>PCB can not appear bubbles after through the reflow oven.</li> <li>Copper lead due to the PCB green oil drop or scratches.         If repaired by adding the green oil, circuit diameter Φ can not over 1.3mm, other diameter Φ can not over 2.6mm, total less than 10 areas. Otherwise reject.     </li> </ol>                                                                                                     |     | 4   | Rejected        |

| 6.6.3 | Components<br>error        | <ol> <li>PCB components inconsistent with drawing. Wrong components, more or less pa, polar reverse (The bias circuit of LCD voltage or BL limit current value adjustment is not controlled if not special specified.)</li> <li>The JUMP short of PCB should be consistent of the mechanical drawing.</li> <li>The components is specially required by the customers and specified in</li> </ol>                                                                                           | √   |     | Rejected        |

| mechanical drawing / technical                                 |

|----------------------------------------------------------------|

| documents, the components specification should be conformed to |

| technique demand. Otherwise rejected                           |

|                                                                |

#### 6.7 SMT part (Refer to IPC-A-610C if not specified)

| No.   | Item                         | Description                                                                                                                                                                              | MAJ | MIN      | Accept standard |

|-------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------------|

| 6.7.1 | Soldering defect             | Cold soldering, false solder, missing solder, tin crack, tin un-dissolved happened with soldering.                                                                                       |     | <b>√</b> | Rejected        |

| 6.7.2 | Solder<br>ball/splash        | Solder ball/tin dross drop lead to solder short.                                                                                                                                         |     | <b>√</b> | Rejected        |

| 6.7.3 | DIP parts                    | DIP parts, keypad, connection appear floating and tilted.                                                                                                                                |     | √        | Rejected        |

| 6.7.4 | Spot weld shape              | The spot weld should be inner dent, can not form to cover solder or less solder or icicle, otherwise reject                                                                              |     | <b>√</b> | Rejected        |

| 6.7.5 | Component<br>foot<br>exposed | For the DIP type components, after soldered, 0.5~2mm component foot must be remained, and should not damage the solder surface nor fully covered the component foot. Otherwise rejected. |     | <b>√</b> | Rejected        |

| 6.7.6 | Appearance poor              | After soldering, the solder residues appear brown or black. PCB solder spot remained white mist residues after clean.                                                                    |     | <b>√</b> | Rejected        |

#### 6.8 Heating pressure part (including H/S, FPC, etc.)

| No.   | Item                  | Description                                                                                                                                                                         | MAJ | MIN | Accept standard |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| 6.8.1 | Out of specif ication |                                                                                                                                                                                     | √   |     | Rejected        |

| 6.8.2 | Size/position         | The size of heating material should be within the specification of the drawing, the contact area of conducted material should be attached more than 1/2 of the body (ITO, PDA, etc) |     | √   | Acceptable      |

| 6.8.3 | Heat pressure dirty   | The obstacle existed in non-conductive heating area and not lead to short, or existed in conductive area but the obstacle is less than 50% of pressure area, it is acceptable.      |     | √   | Acceptable      |

| 6.8.4 | Folding defect |  | √ | Refer to limited sample |

|-------|----------------|--|---|-------------------------|

|       |                |  |   | Sample                  |

#### 6.9 Connector and other parts

| No.   | Item                   | Description                                                                                                                                             | MAJ      | MIN | Accept standard |

|-------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----------------|

| 6.9.1 | Specification improper | The specification of connector and other components do not conform to the drawing as required.                                                          | <b>√</b> |     | Rejected        |

| 6.9.2 | Position and order     | Solder position and Pin 1 should be consistent with the drawing.                                                                                        |          | √   | Rejected        |

| 6.9.3 | Cosmetic               | <ol> <li>The body of outer component and the PIN has flux.</li> <li>The deformation bigger of PIN connector is bigger than 1/2 of PIN width.</li> </ol> |          | 1   | Rejected        |

#### 6.10 General cosmetic

| No.    | Item                   | Description                                                                                                                                                                                                                              | MAJ | MIN      | Accept standard |

|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------------|

| 6.10.1 | Connection<br>material | Copper lead on FPC pad or the pin terminal of H/S, FFC and damaged. FPC,FFC, COF,H/S connected material curved (except for original). FPC, PCB pad is bigger than 1PIN width. FPC/FFC material segment, crease exceed the specification. |     | <b>√</b> | Rejected        |

| 6.10.2 | Stiffing type defect   | Stiffening tape is not covered or fully covered the product's circuit needs to be protected. (Like H/S, FFC, FPC) or cover to the output pin.                                                                                            |     | √        | Rejected        |

| 6.10.3 | Visual dirty           | Dirty on surface of finished products, residual glue, solder spatter or solder ball remain on non-soldered area of PCB/COB.  The defective mark or label on product does not remove.                                                     |     | <b>√</b> | Rejected        |

| 6.10.4 | Assembly black spot    | The spot or black dots found after assembly the products with backlight or diffuser.                                                                                                                                                     |     | √        | Refer to 6.3.1  |

| 6.10.5 | Product<br>mark        | Part number and batch mark is not conformed with the technical requirement and position, not clear or without mark.                                                                                                                      |     | 1        | Rejected        |

| 6.10.6 | Inner<br>packing       | Packing is inconsistent with requirement, short or over load, Packing is inconsistent with shipment mark/ order demand.                                                                                                                  |     | √        | Rejected        |

| Test item           | Condition                                         | Time(hrs) | Accept standard          |

|---------------------|---------------------------------------------------|-----------|--------------------------|

| High Temp Storage   | 80°C                                              | 120       |                          |

| High Temp Operating | 70°C                                              | 120       |                          |

| Low Temp Storage    | -30°C                                             | 120       | No abnormalities in      |

| Low Temp Operating  | -20°C                                             | 120       | functions and appearance |

| Temp& Humidity Test | 40°C/90%RH                                        | 120       | Tomestons and appearance |

| Town Charle         | -20°C ← 25°C → +70°C                              | 101       |                          |

| Temp Shock          | $(30 \min \leftarrow 5 \min \rightarrow 30 \min)$ | 10 cycles |                          |

#### 7. Reality test